文章目录

1. 基元

在AHDL中有一系列基元(primitivities),这些基元可以被理解为C中的Structure,我们在定义变量时也需要定义变量所属的基元

除了最基本的NODE外,AHDL还提供了许多不同的基元,我们需要根据应用的场景来为变量选择适当的基元,常用的基元如下:

可以看到,每一个基元都对应某一种硬件类型,编写AHDL时需要根据硬件类型设定变量归属的基元

每个基元都会拥有自己的成员,这些成员通常与逻辑电路的输入输出直接关联,比如时序电路会有名为clk的基元,对应CLOCK,我们所要做的就是为每个成员分配适当的值来实现我们需求的功能

2. 锁存器与触发器

2.1 D锁存器 (D latch)

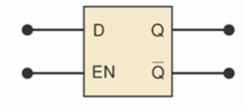

通常来说,简单的锁存器具有两个输入D, EN和两个输出

Q

,

Q

‾

Q, \overline{Q}

Q,Q,如图:

锁存器可以将D中输入的信号存储起来,并不断输出到

Q

,

Q

‾

Q, \overline{Q}

Q,Q,只有在端口EN被正确触发时,锁存器才会接受下一个从D中输入的信号

在AHDL中,锁存器的基元为:LATCH

输入为:

- Data Input,通常用d表示

- Enable,通常用EN表示

输出为:

- Data Output,通常用q表示

注意,虽然实际的锁存器具有两个输出,但在AHDL中我们只用声明一个

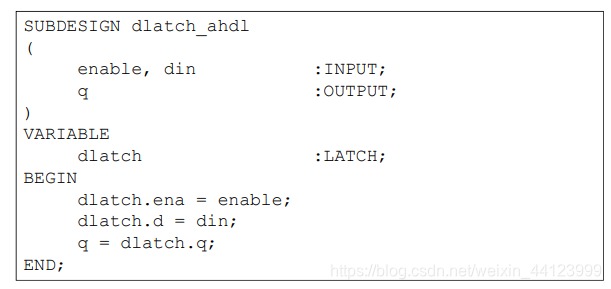

D锁存器是锁存器的一种,下面给出D锁存器的一份示例代码:

可以看到,我们声明了两个输入enable, din和一个输出q

接着,我们将变量dlatch分配给了属于锁存器的基元LATCH,这个基元有三个成员,其中ena对应输入EN,d对应输入D,q对应输出Q。因此,我们可以注意到,在代码中定义的输出enable和din被分配给了dlatch.ena和dlatch.d,意味着dlatch变量中的ena成员与enable相等,d成员与din相等

2.2 触发器 (Flip-Flop)

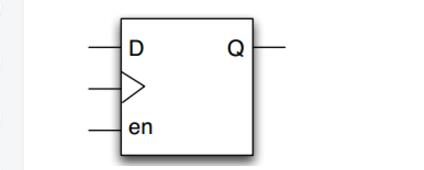

触发器实际上就是引入时钟脉冲(CLK)的锁存器,相比锁存器只要EN触发就可以接收输入,触发器还必须被时钟信号触发才能读入D的输入,最常见的触发器如下图所示:

可以看到,除了锁存器应有的D和EN外,触发器还有一个时钟脉冲接收端,即图中D和EN中间的三角

触发器根据功能的不同可以分为D触发器,J-K触发器,S-R触发器和T触发器,下面将详细描述不同触发器对应的基元,输入和输出,每一个输入输出对应的基元的成员用括号写在后面

2.2.1 D 触发器

基元:DFF 或 DFFE

输入:

- Data Input (d)

- Clock (clk)

- Asynchronous Clear (clrn) and Set (prn),

both active-LOW. - Enable (ena), 只有DFFE才有

输出:

- Data Output (q)

2.2.2 J-K 触发器

基元:JKFF 或 JKFFE

输入:

- Set (j) and Reset (k)

- Clock (clk)

- Asynchronous Clear (clrn) and Set (prn), both active-LOW

- Enable (ena), 只有JKFFE才有

输出:

- Data Output (q)

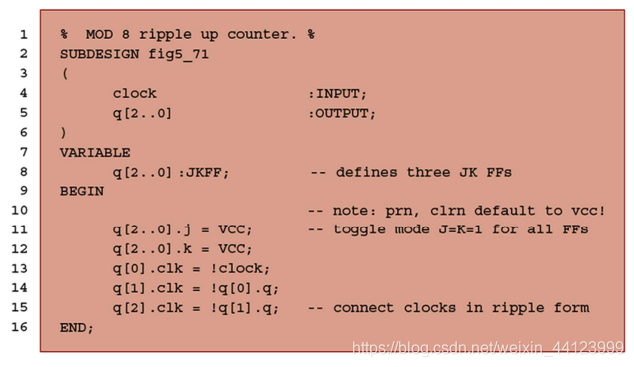

下图是J-K 触发器的一份示例代码:

可以看到这里的基元是JKFF而非JKFFE,所以输出不含ena

2.2.3 S-R 触发器

基元:SRFF 或 SRFFE

输入:

- Set (s) and Reset (r)

- Clock (clk)

- Asynchronous Clear (clrn) and Set (prn), both

active-LOW. - Enable (ena), 只有SRFFE才有

输出:

- Data Output (q)

2.2.4 T 触发器

基元:TFF 或 TFFE

输入:

- Toggle (t)

- Clock (clk)

- Asynchronous Clear (clrn) and Set (prn), both

active-LOW. - Enable (ena), 只有TFFE才有

输出:

- Data Output (q)

3. 计数器 (Counter)

计数器本质上是由多个触发器组成的电路,不同计数器可以根据CLK是否统一分为同步计数器 (Synchronous counter) 和异步计数器 (Asynchronous)

3.1 异步计数器

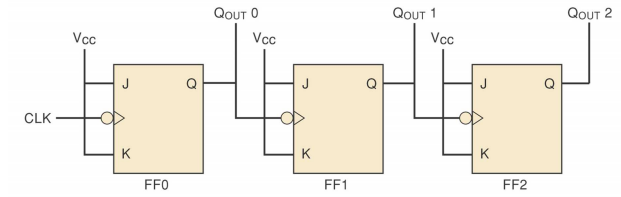

异步计数器中,一个触发器的CLK来自于上一个触发器的输出,一个由J-K 触发器构成的计数器电路如图所示:

可以看到,每个触发器的CLK都与上一个触发器的输出Q相连

示例代码如下:

可以看到我们用q[2…0]定义了三个基元为JKFF的变量,每一个变量的j, k成员都等于VCC,也就是等于1,除了第一个触发器q[0]的时钟脉冲直接与定义的输入clock相关外i,其它触发器的clk都等于上一个触发器的输出q

注意,由于图中clk前面有反向符号,每一个clk都等于输入的反向,需要在前面加上!

3.2 同步计数器

同步计数器中每个触发器的CLK都连接到一个相同的输入,这也意味着他们clk端接收到的输入始终相等

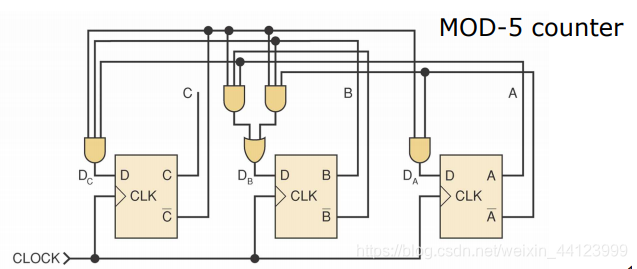

下图是一个由D 触发器组成的同步计数器(注意,计数器并不只有触发器,图中的基本逻辑门也是计数器的一部分):

在用AHDL描述同步计数器时,我们不必再考虑复杂的连线,而是只用考虑如何准确地描述出电路的逻辑

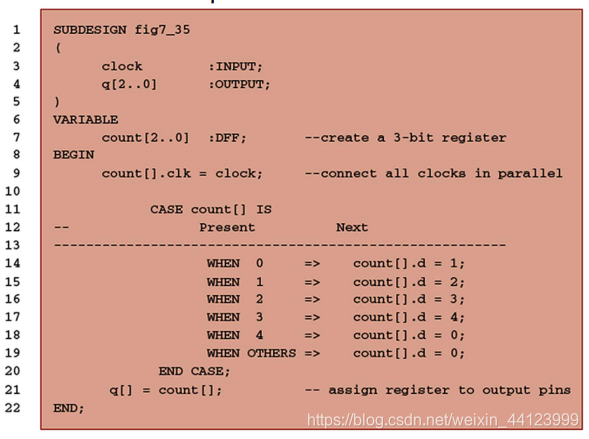

一个MOD-5同步计数器示例代码如下:

MOD-5计数器指的是从0数到4,再回到0的循环计数器,上图中我们在变量里声明了三个基元为DFF的变量

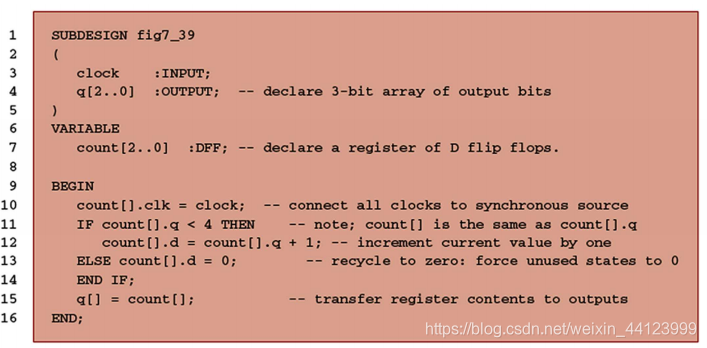

我们先让每个触发器的时钟脉冲输入都等于clock,接着让触发器的输入等于输出+1,上图将这一过程拆成了多种case来表达,这显得有些繁琐,下图是一个仅描述行为的代码:

可以看到,当触发器的输出小于4时,电路会将输出+1后重新送进输入,如果输入大于4,则会直接清零

这里注意,count[] 与count[].q 是等效的

计数器有时还会包含其它功能,比如清零,停止计数,使计数器接受当前给它输入的数字(load),向上计数,向下计数,以及在每一轮计数完成时输出一个计数结束符等功能,下图是一个包含了这些功能的计数器代码:

4. 移位寄存器

移位寄存器也是由多个触发器组成的器件,它可以将接收数据流,并在每一个时间脉冲将其移动一位进行输出,如图所示:

可以看到在最开始设置了初始值后,移位寄存器会将自己的数据流一位一位向右移,将最右一位的数据输出,并用左边第一位接受新的输入

移位寄存器可以串行或并行的方式接受数据,也可以穿行或并行的方式输出数据,根据数据输入/输出方式的不同,可以将其分为四种,这里仅介绍最简单的串行输入,串行输出移位寄存器,下图是示例代码:

可以看到,简单的串行输入/串行输出移位寄存器有三个输入,clk, shift 和 serial_in

输出只有一个serial_out

在变量里我们定义三个基元为DFF的变量,移位寄存器先将最小的变量的输出q分配给serial_out

如果shift 为 true,则通过第12行代码将数据整体右移,并在最左端添加我们的输入serial.in

如果shift没有触发,则会保持当前的数据

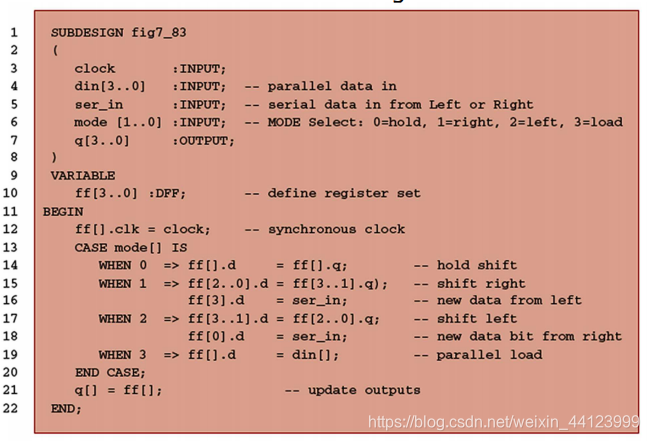

同样的,移位寄存器也可以有许多额外功能,包括串行接收数据,并行接收数据,左移数据,右移数据,保持数据,整体替换数据等,下图是一个包含这些功能的移位寄存器示例代码:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?