一、概述

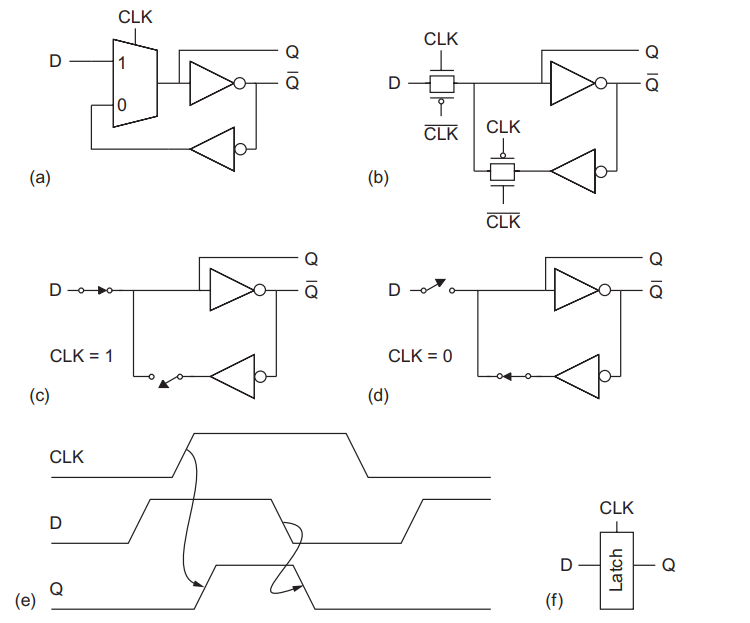

下图为D锁存器,由一个二输入多路开关和两个反相器构成。由于两个反相器可复原电平,因此多路开关可以用一对传输门构成。当CLK=1时锁存器透明,因而D通过它到达Q。当CLK下降至0时,锁存器将变为不透明。此时沿这对反相器建立起一条反馈通道,使当前的Q状态能无限期的保持下去。

D锁存器也称为电平灵敏锁存器(Level-sensitive latch),这是因为它的输出状态取决于时钟信号的电平。传输门和反相器都是由一个nmos和pmos组合而来。

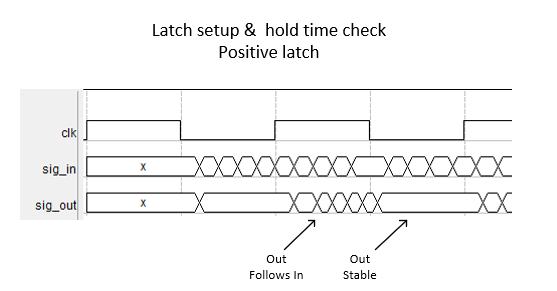

考虑高电平敏感的锁存器,输入必须在时钟下降沿附近的一段较短时间内稳定以满足建立时间(setup time)和维持时间(hold time)的要求(即考虑锁存器关闭输入信号的沿)。一般在做同步RTL设计时,我们应该避免设计出latch,因为latch的时序相比DFF复杂,不利于分析。如果在设计中必须要使用latch,会在rtl代码中直接例化标准单元中的latch cell。本文主要讨论latch在一些特殊场景下的应用。

Latch timing

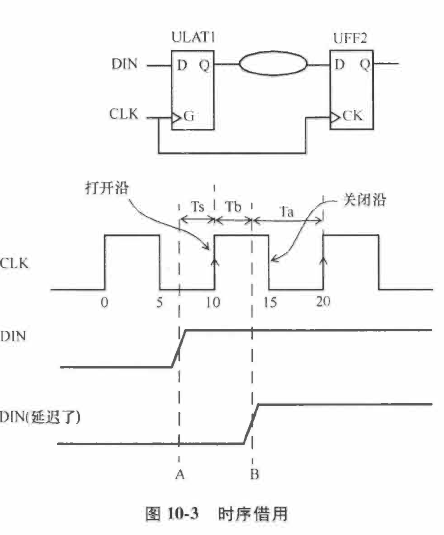

二、time borrowing

文献《IC芯片设计中的静态时序分析实践》(Static Timing Analysis for Nanometer Designs:A Practical Approach)10.2小节很好的解释了latch的time borrowing特性,图 2中ULAT1是高电平敏感的锁存器,UFF2是上升沿有效的D触发器。对于ULAT1,假如DIN在Opening edge到来前稳定(A时刻点),那么此时没有发生time borrowing,ULAT1的setup slack为正;假如DIN在Opening edge之后,Closing edge之间稳定,此时发生了time borrowing,ULAT1的setup slack为0,向下一条路径“借”的时间为Tb;假如DIN在Closing edge之后才到来,此时setup违例,为负值。需要注意的是当发生了time borrowing之后,ULAT1到UFF2的setup time计算总量就不是一个时钟周期了,原本的计算总量是20ns,time borrowing后变成Ta=20 - Tb。

latch time borrowing

三、latch在ICG中的应用

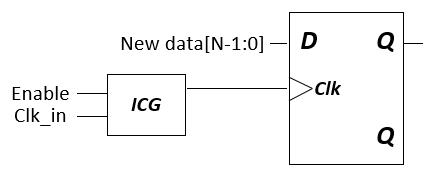

3.1 ICG结构

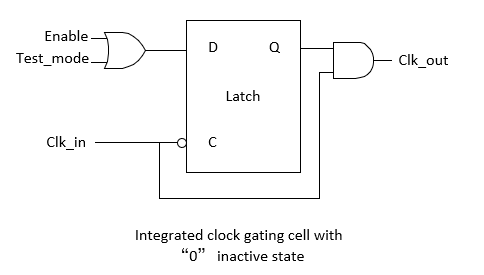

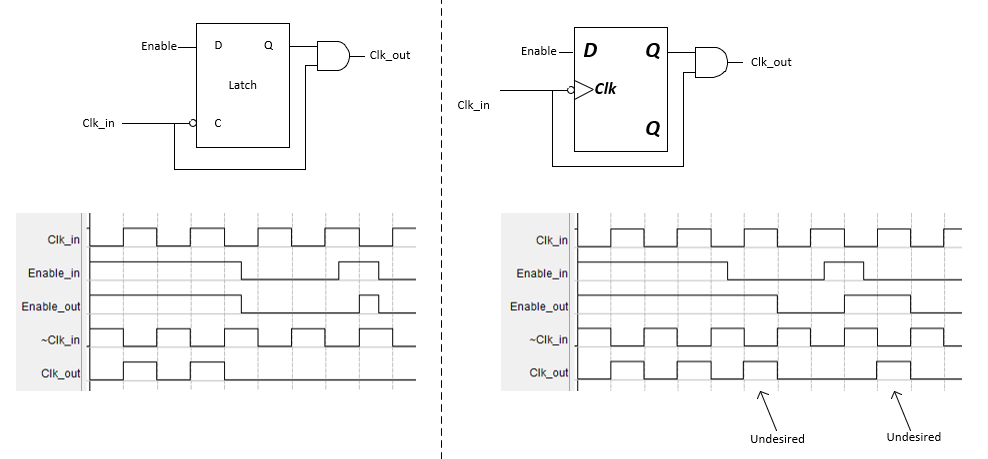

ICG,全称是Integrated Clock Gating,在需要对时钟信号进行控制的场合常常会用到,最常见的ICG内部结构由一个低电平敏感的DLatch和一个与门组成。

常见的ICG门电路结构

3.2 门控时钟原理

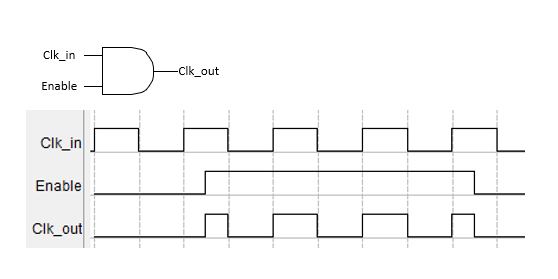

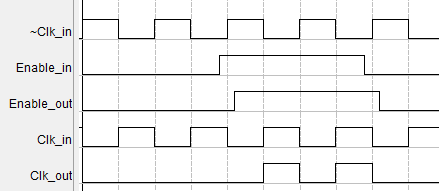

对于与门的ICG,只有clk为低电平时,En信号才会通过ICG。保证了输出的第一个波形是上升沿,对于或类型正好相反。

图 4直接采用与门作为时钟的gating信号,容易产生毛刺。图 5使用ICG作时钟的gating,无毛刺产生。

使用与门作门控时钟

使用ICG作门控时钟

3.3 why Dlatch,not DFF?

思考这么个问题,把ICG里面的DLatch换成下降沿触发的DFF,也可以实现和ICG一样的功能,为什么各大fab厂的标准DLatch没有这样做呢?总结了一些参考资料,主要原因有以下几点

1、“用latch可以borrow timing,即便enable信号不满足setup,也可以成功采到实现gating功能。如果用Flop,一旦因为干扰或者时序本身的问题,很可能导致第一拍采不到数,会使得gating的时序落后一拍,如果时序要求严格,会产生问题。”eetop网友(陈涛),也就是使用DFF对时序的要求比较高。同时我们可以看到使用DFF容易产生多余的时钟。

使用DLatch与DFF gating的波形比较

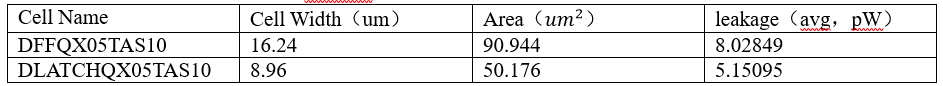

2、DLatch和DFF相比,面积更小,具有更低的leakage,是台积电M31LLSC1050TH180GS标准单元库中相同驱动能力的DFF和DLatch的一些参数对比

DLatch与DFF 标准单元比较

3.4 ICG的用途

1.用于关断时钟,降低功耗。

2.用于动态切换时钟时防止产生毛刺。

3.用于时钟分频。

En信号要求:

1.En不能异步,一定要同步。否则En和时钟沿离得太近,容易亚稳态。

2.En一定不能是门控后的信号产生的,否则会出现死锁的情况。

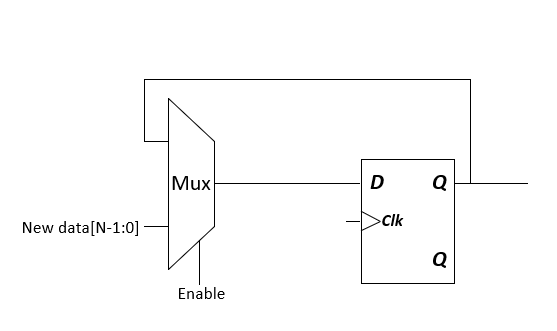

3.5 ICG除了可以起到降低功耗的作用,还可以减少面积。

未加ICG生成的multi-bit触发器电路结构

加ICG生成的multi-bit触发器电路结构

第一种电路消耗的Cell数会更多,Mux的En信号会控制多个bit,即Q的位宽大小的信号,但是时钟门控的En只会控制单个bit,即时钟。

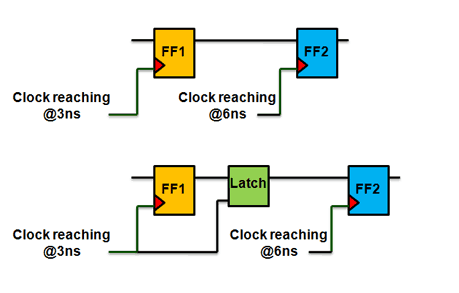

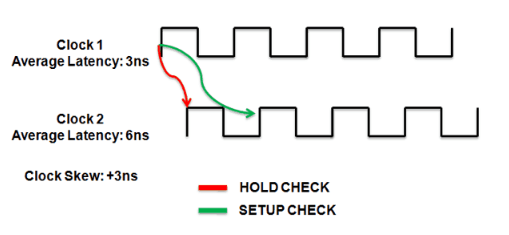

四、latch在DFT中的应用,Lockup-Latch

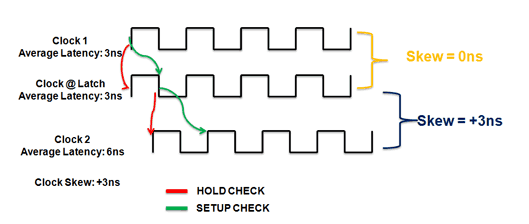

假设FF1和FF2分别属于不同的时钟域,在function模式下,两者设为false path,各自的时钟树不同,两者之间存在时钟skew,在test模式下,二者通过扫描链串联起来,如果此时FF2的skew过大,很有可能会导致对FF1的hold time检测违例,解决办法就是在FF1和FF2之间插入一个DLatch,利用DLatch的timing borrow特性减轻时序压力,就算DLatch有向下一条路径“借”用时间,由于测试模式下时钟频率可控,可以通过降低时钟频率,确保test模式下数据传输与采集的正确性。详情可参考文献[5][6]。

Lockup-latch解决hold time问题

2598

2598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?