文章目录

前言

同步数字电路中主流还是用寄存器,但是锁存器(Latch)也不容忽视,它既能用作数据存储单元,又能作为时钟控制单元。

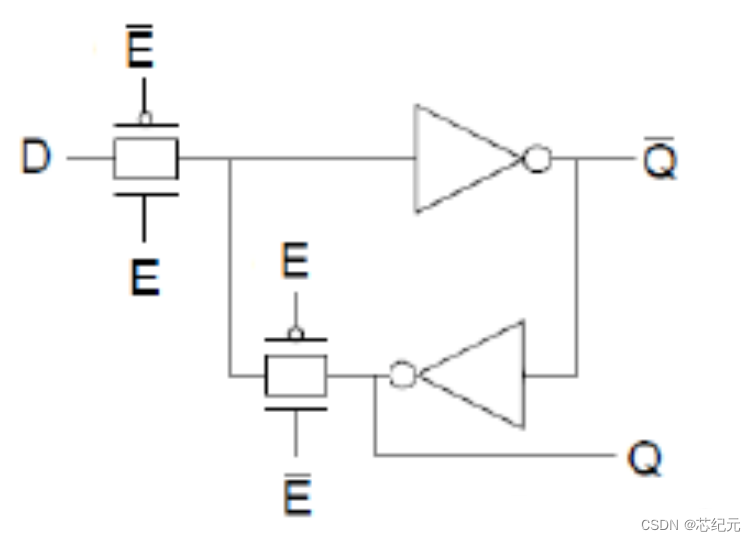

一、Latch功能介绍

D Latch 是一种常用的 Latch。E = 0时,输出状态保持不变,锁存输入信号D;E = 1时,输出随输入状态而改变。因此,D Latch 可以用于存储单比特的数据,设计中使用Latch的好处是相比寄存器的面积更小,功耗更低,可以从后级电路进行time borrowing,更容易满足setup time,然而坏处是STA分析不会那么直接,下面我们就看看引入了Latch的setup/hold Timing Path如何分析。

二、Time Borrowing

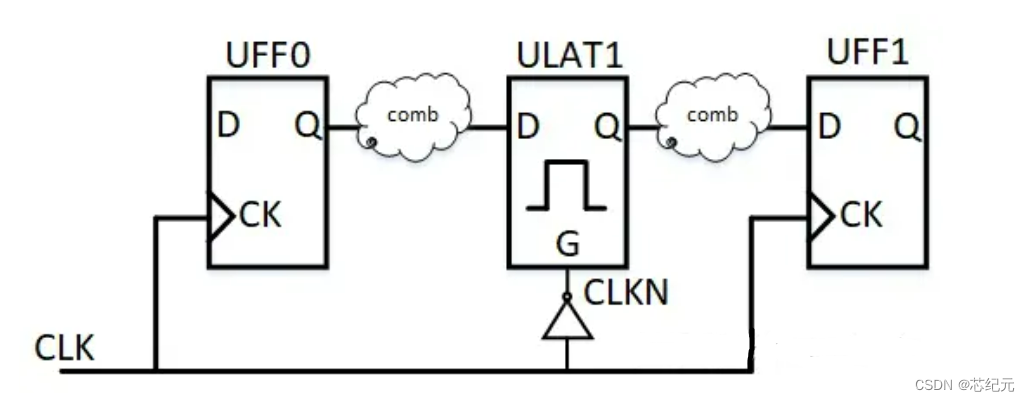

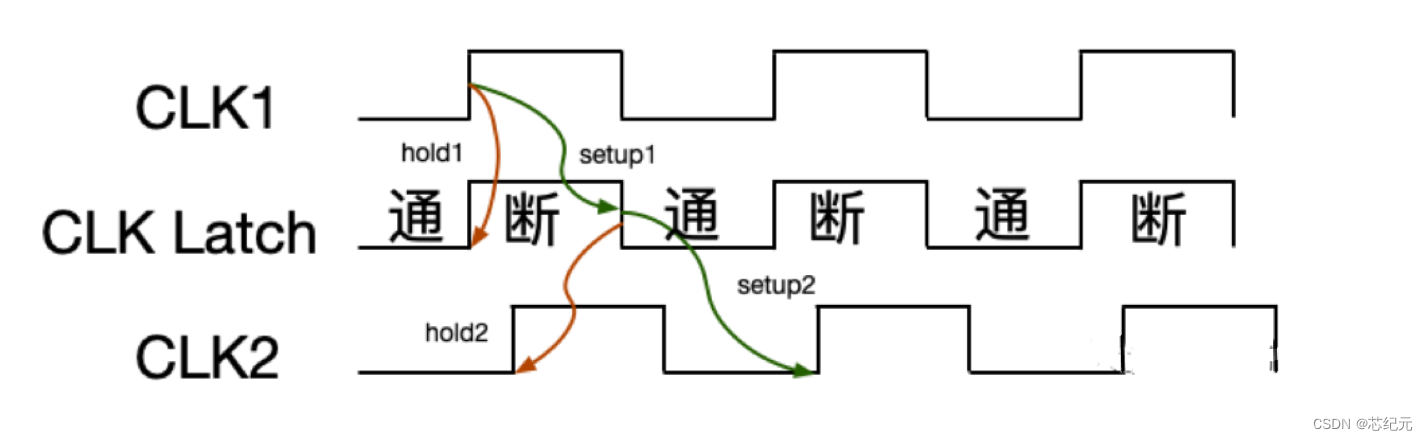

在数字设计中,经常会碰到如下图所示的Path,两个寄存器(UFF0和UFF1)之间存在一个锁存器(ULAT1),这种情况工具会怎么分析path呢?

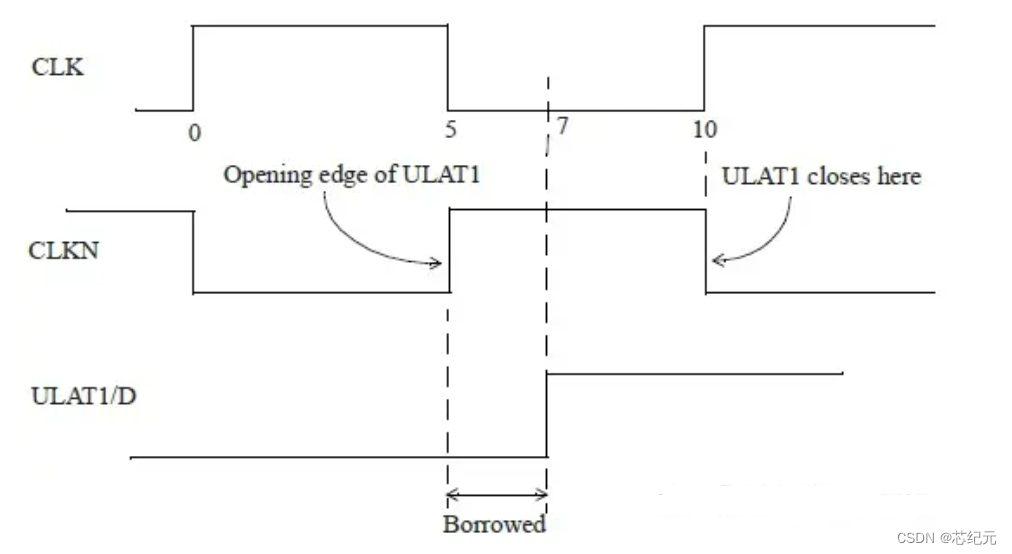

根据Latch的特点,在CLKN为高电平时,ULAT1是transparent,ULAT1/D端的数据能即时地反映在ULAT1/Q端。下图中的情况是,UFF0->ULAT1/D的Path Delay使得ULAT1/D数据在CLKN的上升沿之后才到达,需要从后一级ULAT1->UFF1中进行time borrow,使得原本违例的path满足了要求。

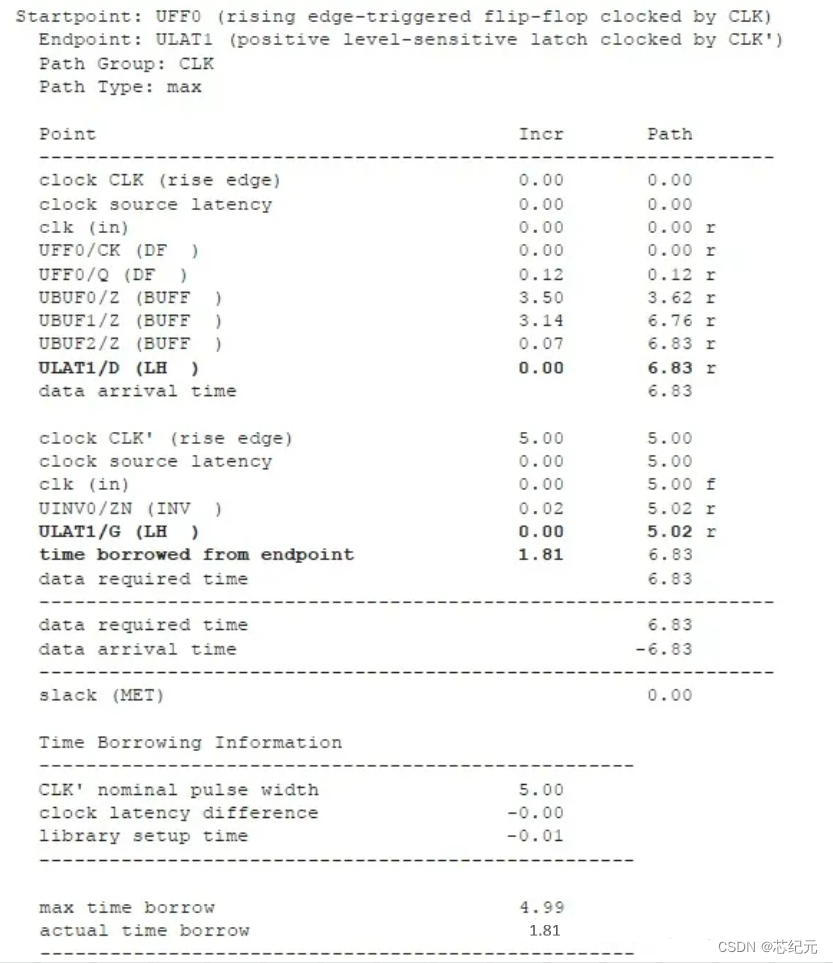

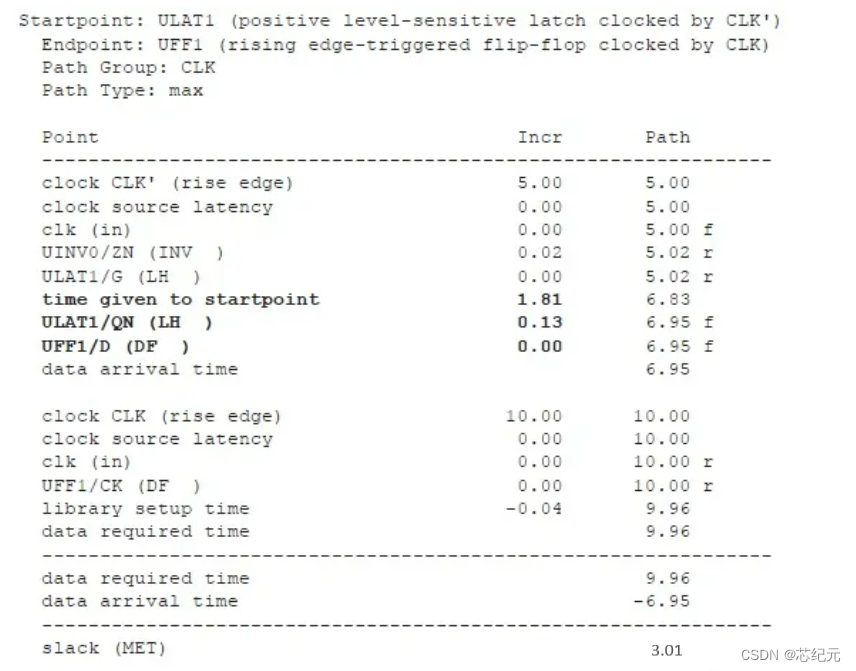

UFF0->ULAT1/D的Path Delay使得ULAT1/D数据在CLKN的上升沿之后才到达,需要从后一级ULAT1->UFF1中借了1.81ns,使ULAT1/D数据在CLKN上升沿到来之前到达,使得原本违例的path满足了要求。而ULAT1->UFF1的timing path即使借出去1.81ns,也能够满足要求,具体的setup timing report如下:

①UFF0 -> ULAT1 setup timing report(从后一级ULAT1->UFF1中借了1.81ns)

②ULAT1 -> UFF1 setup timing report(ULAT1->UFF1的timing path借出去1.81ns给前一级)

三、Lockup Latch in Scan Shift Mode

我们不仅要给功能路径(functional path)close setup/hold timing,还要close scan path setup/hold timing。

在scan shift mode下,scan chain两个flop之间就是直接连接的,而不像functional path中间存在combo logic,再加上scan clock的频率一般也比functional clock的频率要低,所以通常来说setup time是很容易满足的,但是hold time可能会出问题,特别是本来分属于不同的clock domain的两个flop被穿在了一条scan chain下,而clock tree没有做balance的时候,两个flop的clock skew可能会很大,相应的hold time violation也会很大,因为在scan shift mode下,所有的clock是同步的。

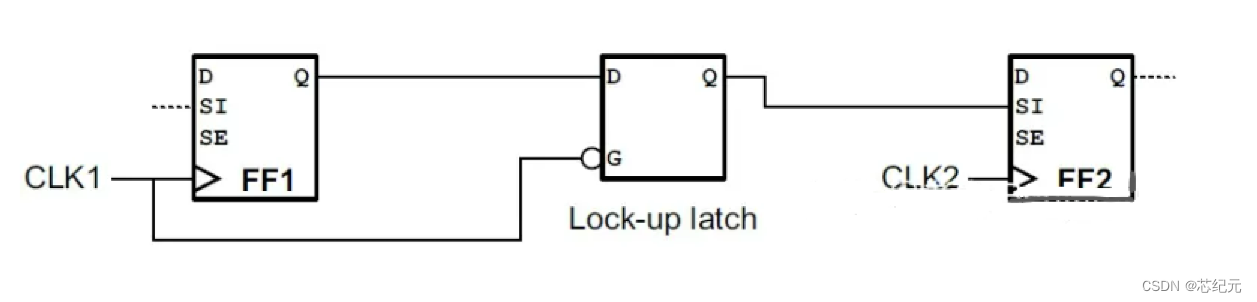

由于CLK1和CLK2为不同的时钟域,很难保证他们同步,假如CLK2相比CLK1有一段不确定的延迟Tskew,可大可小,那么很有可能FF1/CLK1->FF1/Q->FF2/SI这段延时Tdata会比Tskew小,造成hold timing违例。因此,可以在两级寄存器之间加入一个低电平敏感的latch,结构如下图所示:

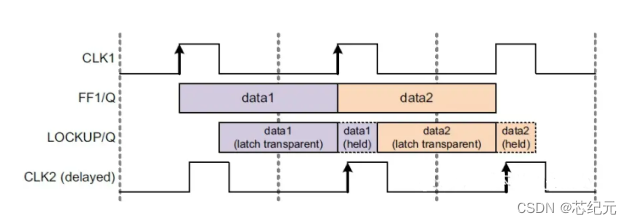

CLK1低电平的时候,Lockup Latch是transparent,CLK1高电平的时候Lockup Latch一直保持上一拍的数据,延长了半个周期,这样即使CLK2有延迟,只要不超过CLK1高电平持续时间,就能保证hold timing没有问题。

另外,为什么不能加高电平敏感的latch, 因为加了之后,CLK1高电平的时候,Lockup Latch是transparent,无法保持上一拍的数据,因此setup仍是一个周期check, hold check时由于Tskew较大导致当前data还没有被capture但下一个data已经到达造成hold timing violation。

lockup latch的主要作用,就是来解决scan shift mode下存在比较大的hold time violation的问题。

四、Clock Gating Check

Latch的另一个应用是作为门控时钟单元(Clock Gating Cell),通过避免部分寄存器不必要的时钟翻转,可以极大地节省电路的动态功耗。设计中使用Latch的好处是,相比寄存器的面积更小,功耗更低,可以从后级电路进行time borrowing,更容易满足setup time。

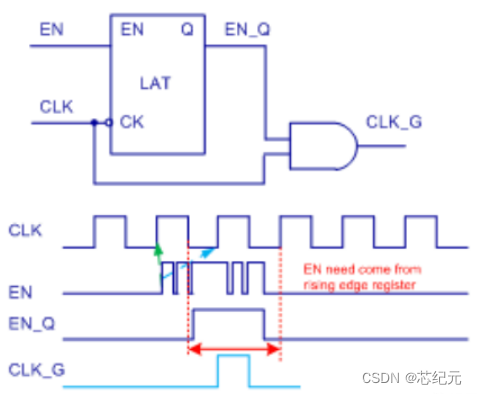

Latch + AND

如下图所示,在AND门前面加入low-active latch。当时钟信号是低电平时,latch处于透明状态,根据输出等于输入;当时钟信号从低电平变为高电平时,latch会读取数据输入端的输入信号,并将其保存在锁存器内部的状态中。由于是低电平有效的latch,因此在时钟高电平期间,即使gating信号存在glitch,也不会影响latch的输出。

因此,EN信号在整个CLK cycle都可以随意toggle, 因为低电平有效的latch,低电平时latch处于透明状态但最终和CLK低电平AND结果为0,高电平时latch锁存输入端信号直至高电平结束。只需要保证将正确的EN信号锁存到latch里面即保证latch的setup/hold timing满足要求即可。

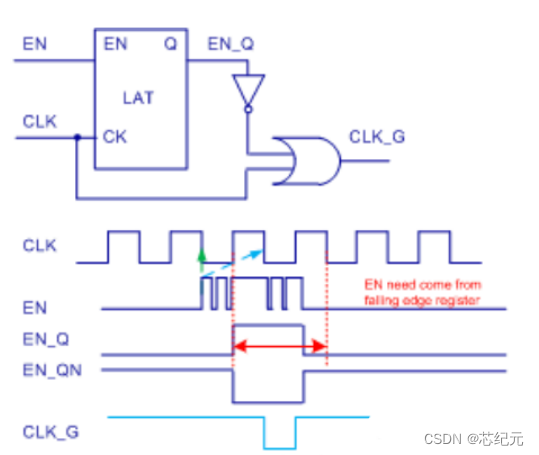

Latch + OR

如下图所示,与latch + AND门不同的是,latch + OR需要使用high-active latch且gating信号来自下降沿触发的寄存器。

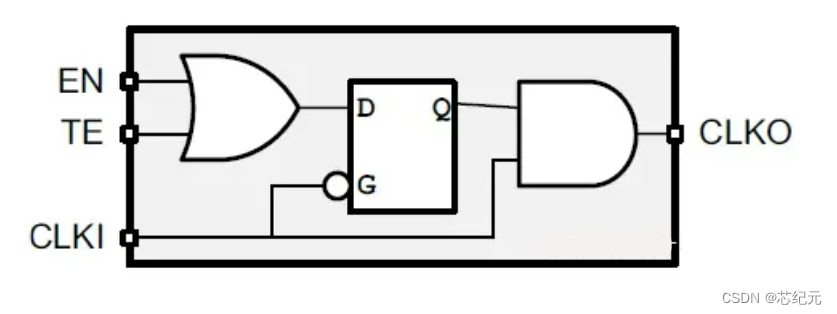

实际应用中,为了避免出现毛刺,会在Latch后面添加一个与门组成一个ICG(Integrated Clock Gating)。

由于ICG是用在clock path上,STA工具默认会要求做CLKI到EN端的clock gating check,目的是保证时钟使能的时序满足要求,所以会存在REG2ICG的path。因为ICG的clock会比REG的clock delay要短,所以天然存在一个skew对setup不利。在设计上,需要保证REG2ICG的数据路径不能太复杂,否则物理实现会存在困难。

总结

因此,对于latch的timing path,一般setup half-cycle check, hold 同沿 check,如果在这种情况下仍有timing violation, 一般setup会time borrow,hold直接insert buffer fix timing violations。

6036

6036

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?