最近学习了GTX的使用,把手册一点点的看还是挺吃力的,特别是众多的端口让人眼花缭乱。但使用起来其实非常简单,这篇文章可以帮助你最快地使用起来GTX,其他GT系列的收发器类似。

前言

使用GT的过程,无非就是关注两个方面。一是数据本身,二是传输数据的速度。最快的用起来的方法是在系统提供的例程上对其进行改动,下面将结合系统自带的例程对其进行介绍。

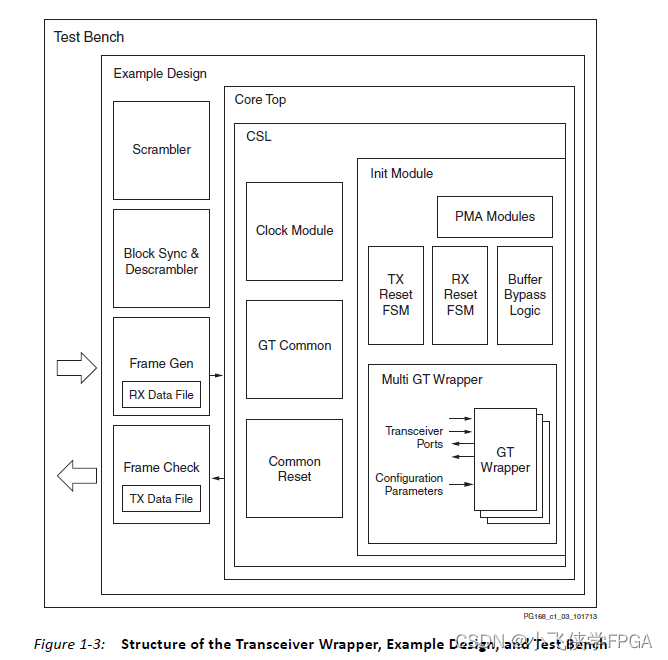

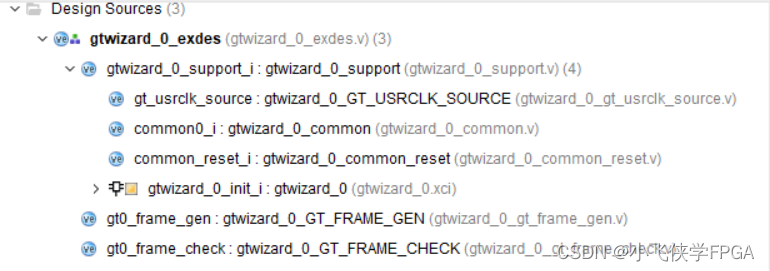

程序结构

CSL部分包括了IP核,以及GT的基本设置(GT Common),时钟模块(Clock Module),复位模块(Common Reset)。可以把这部分看成一个整体,核本身的复位设置还挺麻烦的,这里直接帮我们写好了,不了解具体的内容不影响使用。

Frame Gen是数据发送模块,可以通过这个模块把想要的数据发送给IP核,发送的是并行数据。

Frame Gen是数据检查模块,把从IP输出的数据和原始的数据进行对比。

设置流程

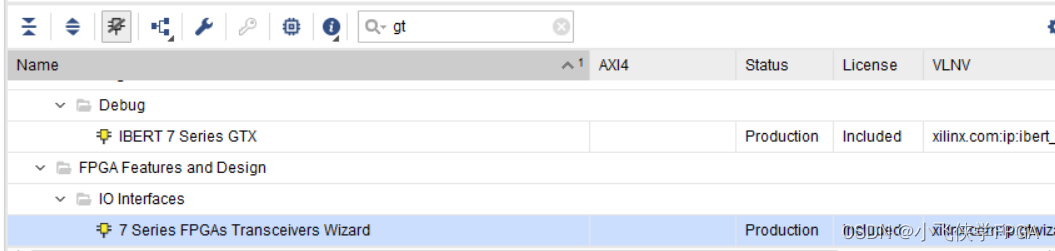

搜索gt就可以找到我们需要的IP核,注意是下面这个,上面的是用来测试gt传输的效率的

点开以后需要设置的参数很多,但其实大部分是不用管的,鉴于本文主要解答传输速度和传输内容的设置,只对以下几个设置进行介绍。

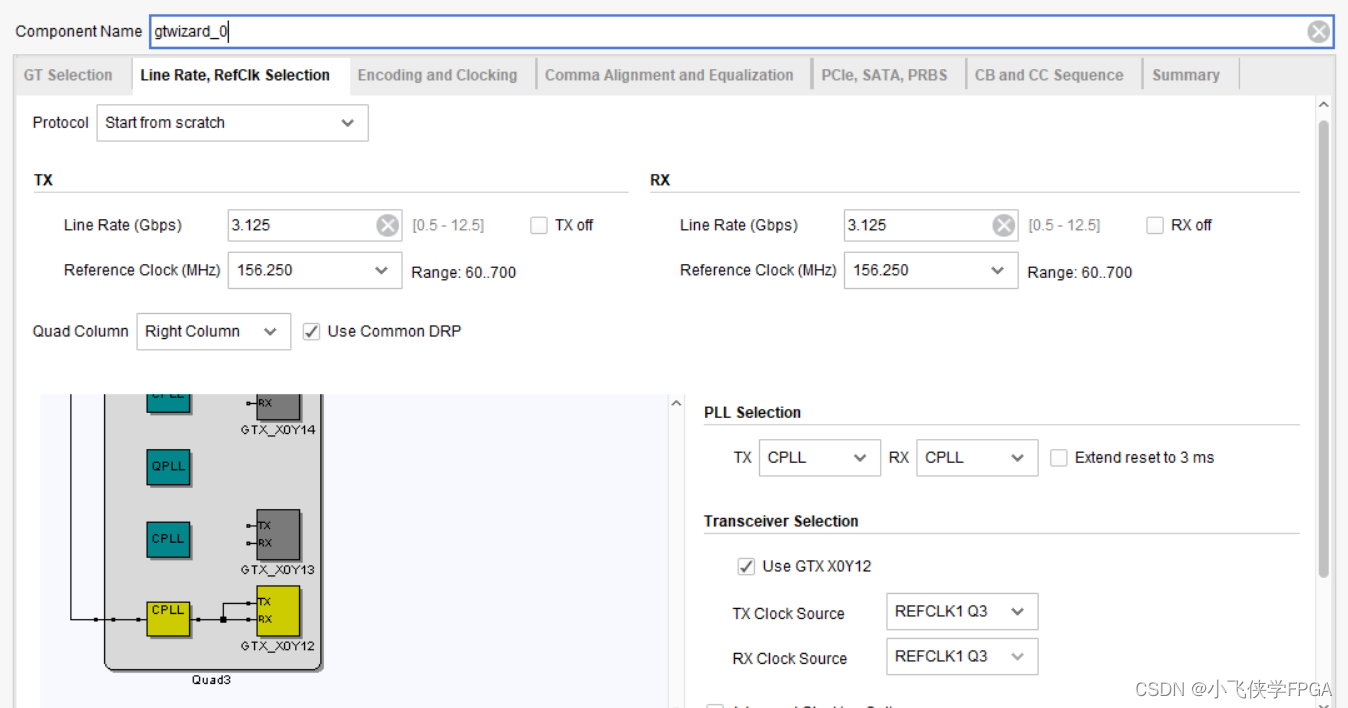

速率设置

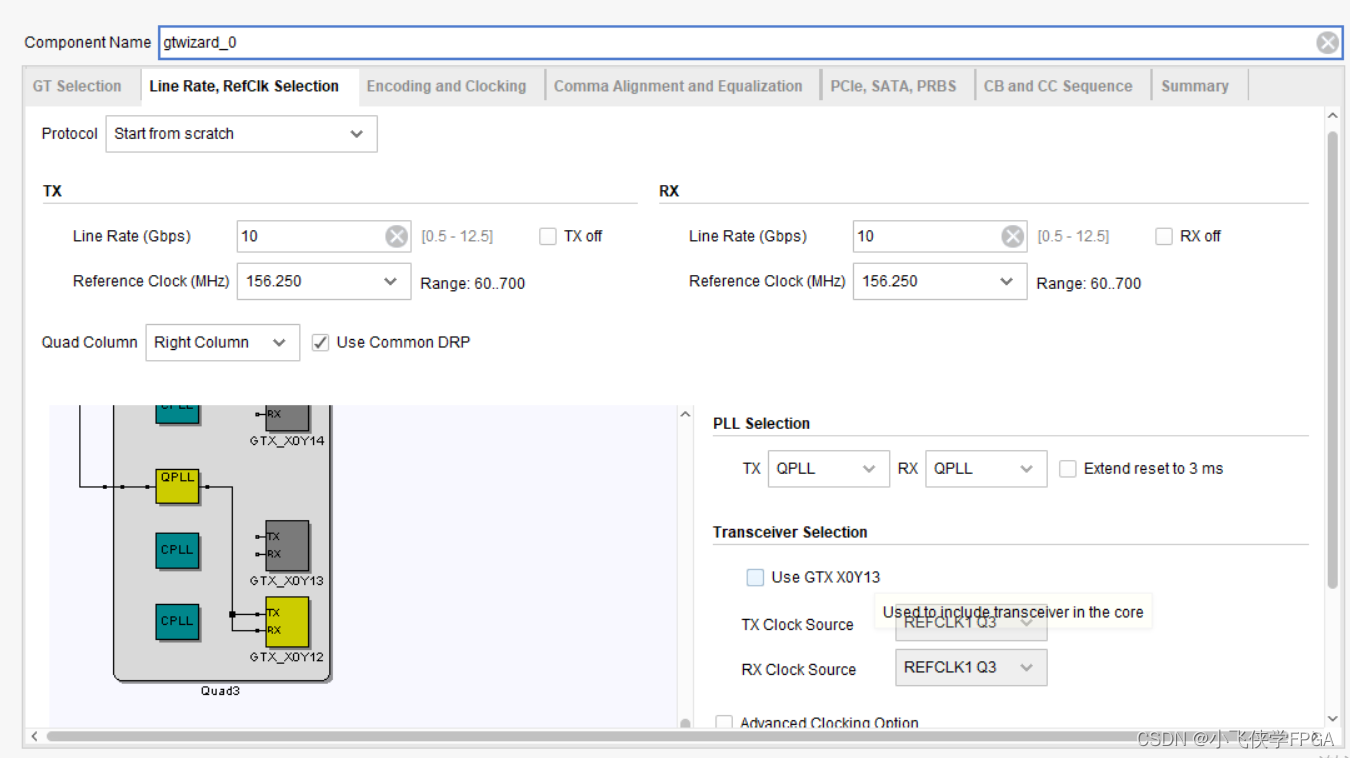

传输速度主要由这里的是图中的Line Rate(Gbps)决定的,当对其进行改变的时候,下面的参考时钟也会随之改变,参考时钟是由系统时钟提供的,这个我们不用管。

当把线速率改变,时钟源也从CPLL换成了QPLL,因为CPLL提供不了这么高的频率。

内容设置

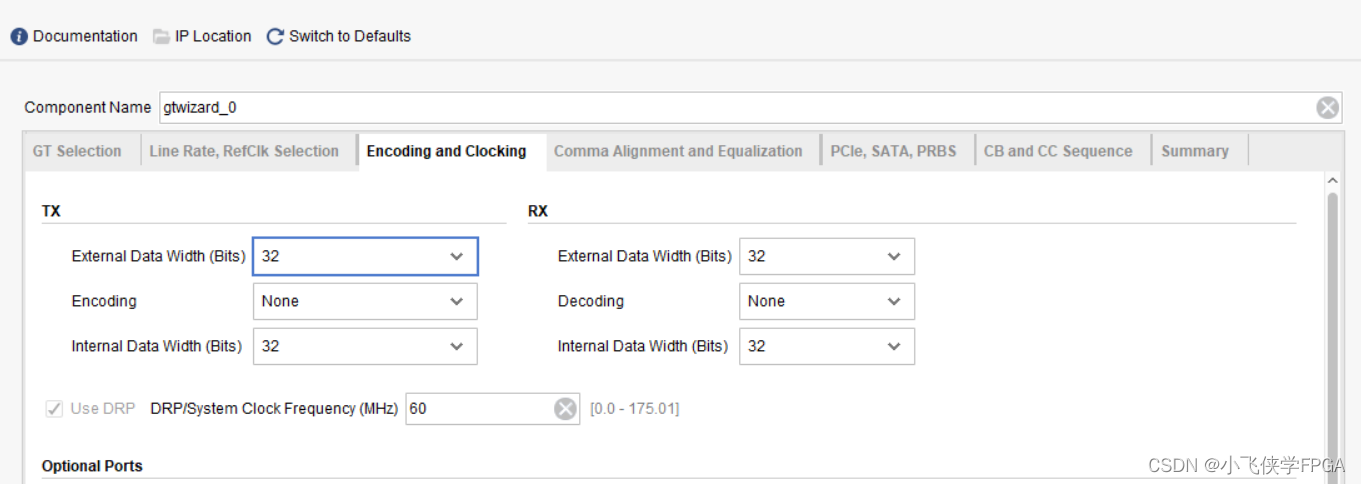

为了尽可能的简化,首先把这个核用起来,设置为不使用编码,内部数据和外部数据传输宽度一致

这样的设计可以让输入给IP核的并行内容不做改动的串行输出。

IP核的设置主要注重这两个方面,其他的地方默认就行。

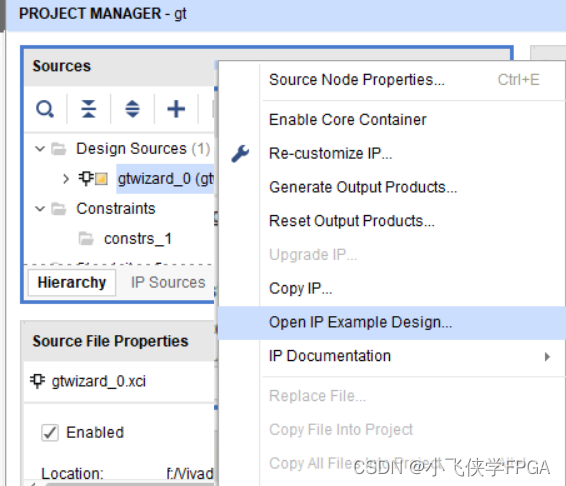

设置完成后,首先打开例程。

support的是包含了核,时钟,复位模块一起的,可以把它理解为一个最小系统。GT_FRAME_GEN是数据输入模块,我们想要改变输入数据就是对其进行修改。GT_FRAME_CHECK是检查模块,不影响我们输出的内容,可以不用管。我们只需要改GT_FRAME_GEN部分内容。

//____________ BRAM Inference Logic _________

assign tx_data_bram_i = tx_data_ram_r[79:16];

assign tx_ctrl_i = tx_data_ram_r[15:8];

initial

begin

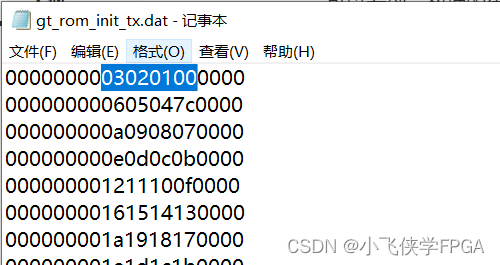

$readmemh("gt_rom_init_tx.dat",rom,0,511);

end

always @(posedge USER_CLK)

tx_data_ram_r <= `DLY rom[read_counter_i];

把GT_FRAME_CHECK程序的最后一部分摘出来,可以看到,它是把文件里面的数据读给了rom,然后每一个时钟来的时候,读取一个数据,把这个数据并行送给GT核。我们想要GT输出什么数据,可以参考这个程序写自己的发生程序,最简单的方法是直接把文件里面的数据改了。

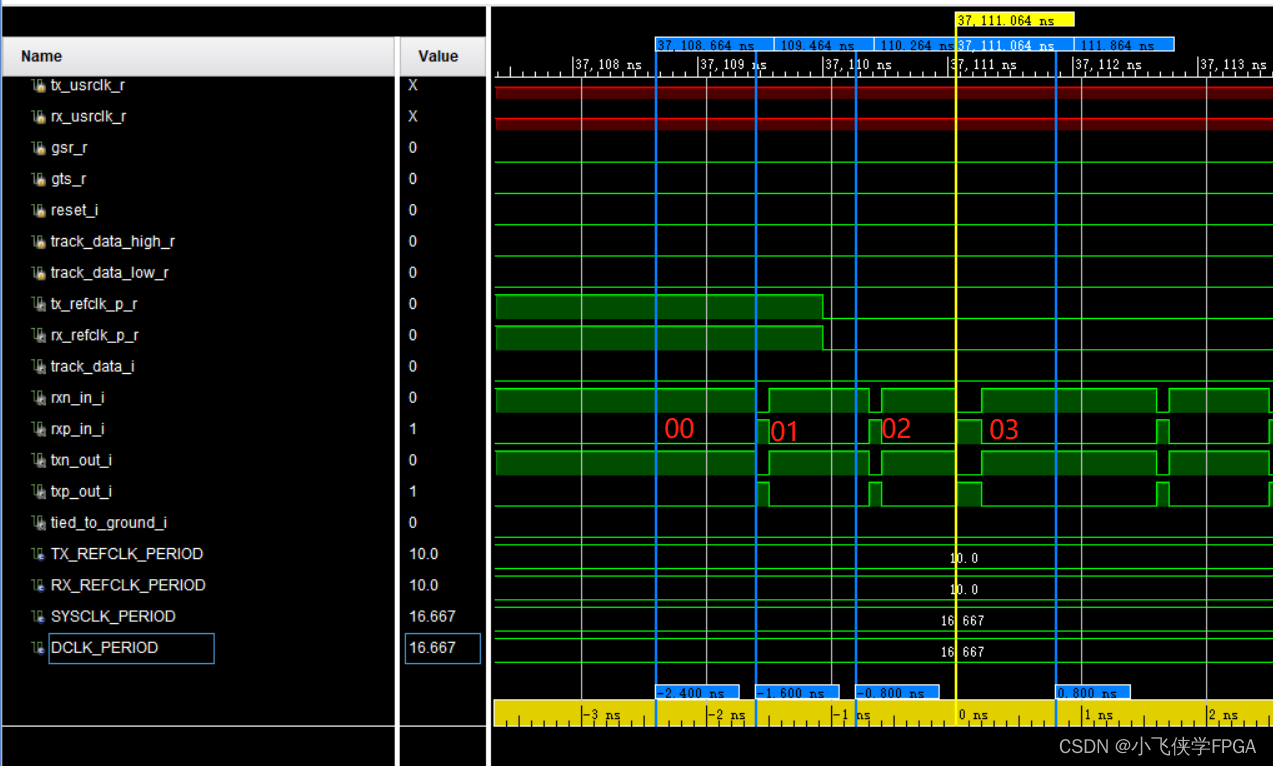

仿真结果

可以看到,数据的传输速率为10G。

第一个数据的内容是00010203

对应着文件里面的数据

至此,我们算把这个IP核简单的用起来了

1574

1574

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?