(没看我之前I2C的原理和代码骗的小伙伴,请先关注浏览观看)既然要通过仿真来验证,就要先明白一点,仿真要达到怎么样的效果才算是验证了设计的正确性,所以这里,仿真的思路也是需要先理清的。

作为一个I2C控制器,其首要目的自然是要能够按照I2C协议进行数据传输,而本实验在设计I2C控制器时,为了让控制器更加的通俗易懂理解,采用了底层传输逻辑和上层读写控制分开的设计方法,所以验证时,主要验证控制器根据Cmd端口不同的命令组合能否正确驱动SCLK和SDA信号产生传输时序。

例如,对于本例来说,验证的时候,最基本的想法就是通过在Cmd端口上给出指定的命令,然后产生G0信号,模块是否能够按照Cmd端口上给出的命令组合依次按照预想传输对应的位或者字段。而且还要验证起始位和停止位的时序是否符合时序标准。进而,既然该模块是一个底层的单次传输模块,设计的时候是希望通过多次控制该模块,每次给出不同的命令和数据,最终实现完整的I2C读写时序控制该模块进行多次传输,查看这种多次传输组合成的I2C传输时序是否符合I2C读写时序。所以总结写来,仿真验证的几个要点如下:

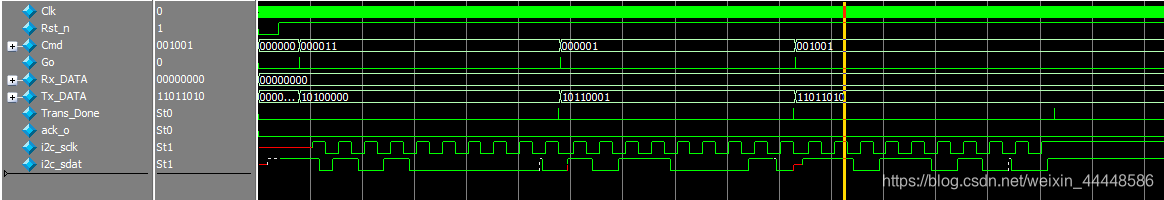

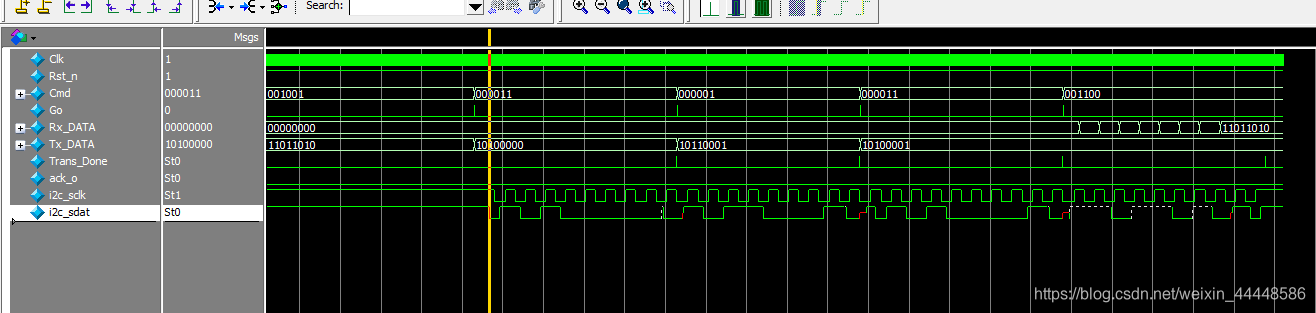

1、在Cmd端口给出某命令组合,查看I2C_SDA和I2C_SCL是否按照预期的时序实现Cmd的端口给出的组合命令。

2、在Cmd端口按照一次完整的I2C读写时序给出每个字段传输时需要的命令组合,查看I2C_SDA和I2C_SCL的波形是否与标准的I2C读写一个字节的时序一致。

采用的仿真模型是M24LC04B,大家可以到MicroChip官网进行下载

写仿真:

EEPROM器件地址A0,EEPROM寄存器地址B1,写数据DA。

读仿真:

EEPROM器件地址A0,EEPROM寄存器地址B0。

具体工程和仿真模型请在源码:

本文详细介绍了如何验证一个基于I2C协议的控制器设计。通过将底层传输逻辑与上层读写控制分开,设计了一个易于理解的控制器,并提供了仿真验证的方法。验证重点包括检查SCLK和SDA信号是否按预期产生传输时序,以及起始位和停止位的时序是否符合标准。作者给出了写和读操作的仿真例子,并提供了仿真模型资源链接,以帮助读者理解和实践I2C控制器的验证过程。

本文详细介绍了如何验证一个基于I2C协议的控制器设计。通过将底层传输逻辑与上层读写控制分开,设计了一个易于理解的控制器,并提供了仿真验证的方法。验证重点包括检查SCLK和SDA信号是否按预期产生传输时序,以及起始位和停止位的时序是否符合标准。作者给出了写和读操作的仿真例子,并提供了仿真模型资源链接,以帮助读者理解和实践I2C控制器的验证过程。

3871

3871

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?