1 AHB设计要点和规则

1.1、HREADYOUT和HREADYIN

很多人包括我自己在第一次接触AHB的时候,会被它的两个HREADY信号搞混,分别是HREADYOUT和HREADY(IN)信号。

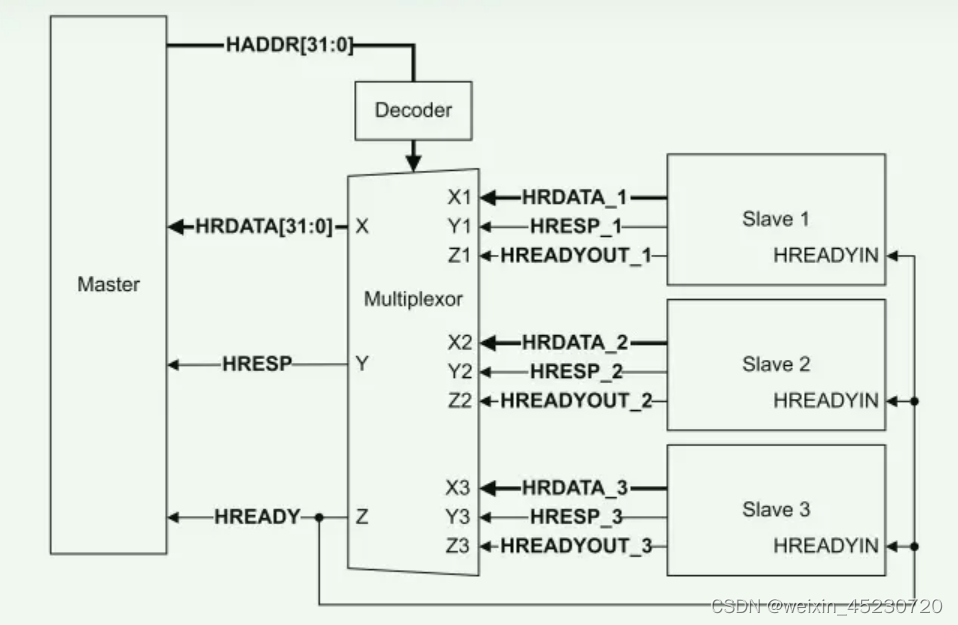

其中HREADYOUT信号是由Slave发出,送给MUX选择器,用来表示Slave是否已经准备进行真正的数据传输(data phase阶段),例如写操作时,Slave是否可以将数据存下来。本质上是Slave对Master的反压信号。

而HREADYIN,由MUX输出返回到所有的Slave,通知各个Slave,是否还有别的SLAVE有未完成的传输。每个Slave在采样地址和控制信号的时候,都要看这个HREADYIN信号是否为1,如果为0的话则代表别的Slave还有未完成的传输,因此不能采样地址和控制信号。

首先我们思考一个问题,HREADYOUT默认的复位值应该是多少?

- 假设都为0,那么HREADY信号自然也为0。这样返回给所有的Slave的HREADYIN信号就为0,则Slave会认为还存在别的transaction还没有结束。则会一直等待,那么整个系统就会不工作了!这也是很多人设计AHB-Slave的时候会犯的错误。

然后我们再思考一下,如果没有HREADYIN信号会怎么样?

- 假设此时有两个Slave,Slave1和Slave2。没有HREADYIN,则对Slave自身而言。没有人去反压它自己,也就意味着只要HSEL选中它的情况下,它都可以接收控制信号。

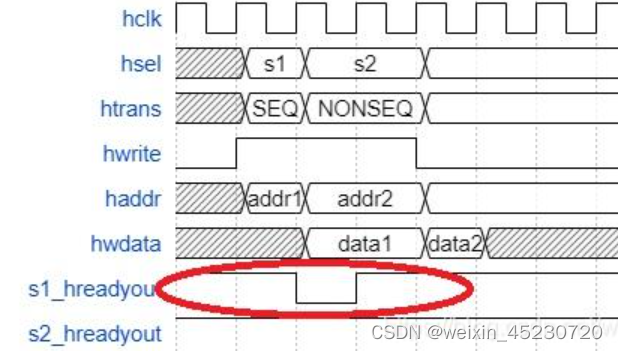

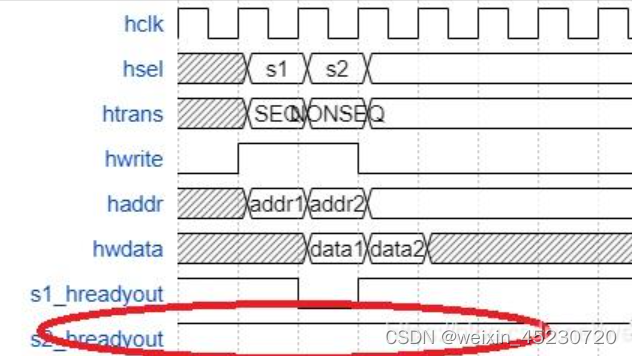

假设在T0->T1这个时间段,S1接收了一笔控制信号(ADDR PHASE)。按理来说T1->T2它应该要返回数据或者将写数据存下来(DATA PHASE),但如果S1不能接收,在T1->T2这个时间段S1的HREADYOUT为0同时T1->T2又进入了新的addr phase,假设此时Master选中的是S2,控制信号什么的都发生了变化。那么请问Master在T2->T3这个阶段应该怎么做?

如果Master是看S1,那么S1的HREADYOUT为0,则MASTER会维持住当前的控制信号。但是T2->T3的时候,实际上选中的是S2,那么S2就会接收两笔控制信号。并且还是一模一样的控制信号,如果都是NONSEQ信号,地址还一样,则直接不符合协议报错。

如果Master是看S2,此时S2的HREADYOUT为1,那么Master会变化控制信号和写数据。那么T2->T3的时候写数据变了,则等到S1的hreadyout拉高的时候,它拿不到正确的数据(此时还是针对S1的DATA PHASE)。

其实核心的逻辑在于,如果没有HREADYIN信号,那么HSEL选中的情况下,Slave就可以接收控制信息和数据信息。这个时候Master无论选择哪个Slave的HREADY,都有可能导致其它的Slave接收到错误的信息。还有一点导致这个原因就是AHB具有pipeline传输,当前的CYCLE有可能既是上一个Slave的data pahse也是下一个Slave的addr phase。

因此如果只靠Slave反压master,选择哪个Slave反压Master就成了问题,这样一来,不管选择哪个Slave都会出问题

1.2、Memory Mapping

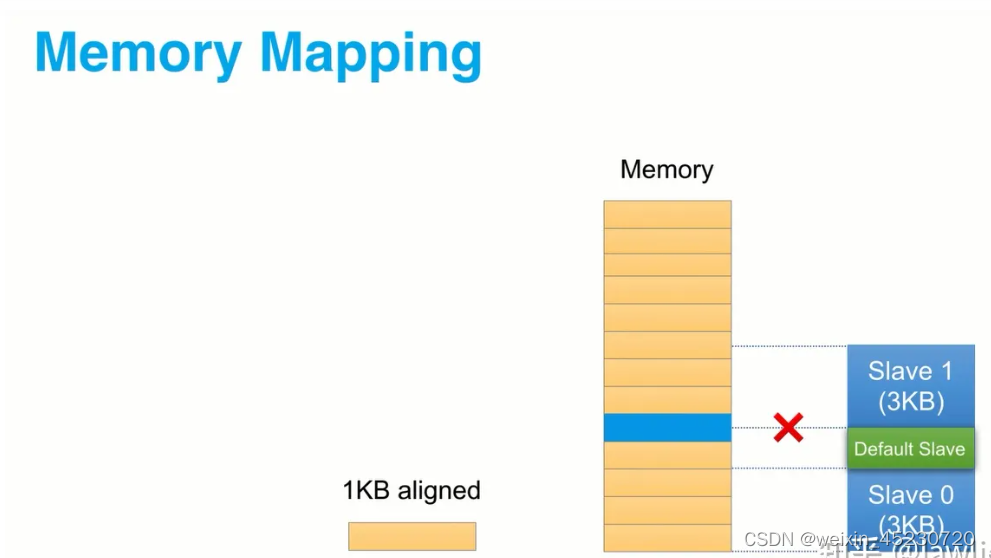

AHB slave最小是按照1KB对齐的,也就是译码的结果,只会看1KB以上的地址。

如果没有做好1KB对齐,这时候HSEL信号会同时选中Slave1和Default Slave。这时候自然就不符合预期了。所以应该按照协议的规则,做好1KB对齐。

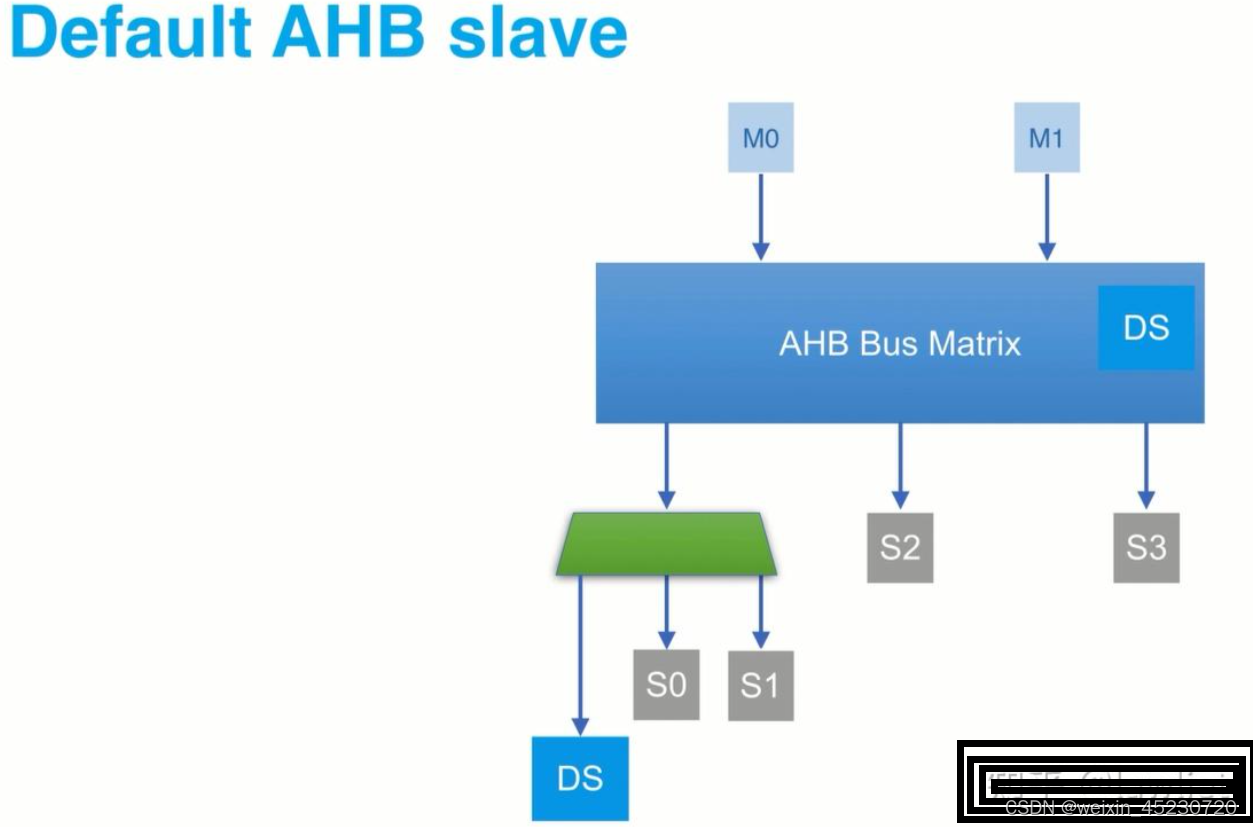

Default Slave是用来干嘛的?我们做Memory Map的时候,自然不可能所有的地址都覆盖掉。我们需要考虑有一个Default Slave,这样访问缺省地址的时候,会有一个符合你需求的Response。如果没有相关逻辑的话,就会有问题,总线会卡住

2 AHB2APB同步桥设计

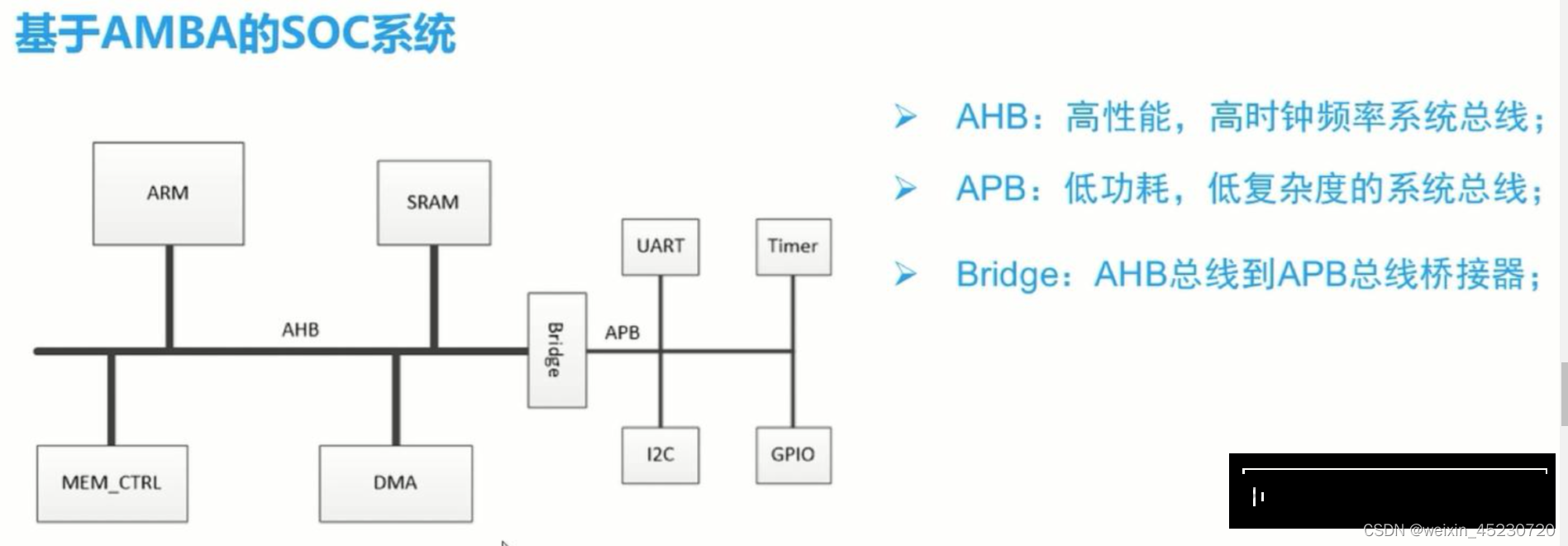

我们再看一下这个典型的基于AMBA的SoC子系统,左右两边分别是AHB和APB子系统。两边子系统的时钟频率通常不一样。所以我们才需要两个子系统,那如何建立二者之间的通信。这个时候就需要AHB2APB转接桥实现协议的转换,实际上在SoC设计当中,转接桥是非常常见的。转接桥的设计很大程度上决定了系统的工作能力,做好转接桥的设计需要对转接桥两端的协议都有充分的理解,此外当时钟频率不一样的时候,还会涉及跨时钟域的知识.

Bridge,顾名思义,桥梁,用于完成两者之间的通信。本篇文章的转接桥是AHB高性能总线到APB总线桥接器,主要完成以下的功能:

- Bridge是APB总线中唯一主机;

- APB的时钟和AHB的时钟是同步时钟;APB的时钟和AHB时钟的分频关系由PCLKEN信号决定;

- 该模块支持输入输出数据寄存或者不寄存,由模块参数控制;

- 该同步桥支持APB总线字节选通信号,保护控制信号;

- 该同步桥支持APB模块的使能信号;

- 该同步桥只支持一个APB从设备,所以只有一个PSEL;

- 对于写传输,驱动数据到APB总线上;对于读传输,驱动APB数据到系统总线上;

2.1 转接桥接口,时序

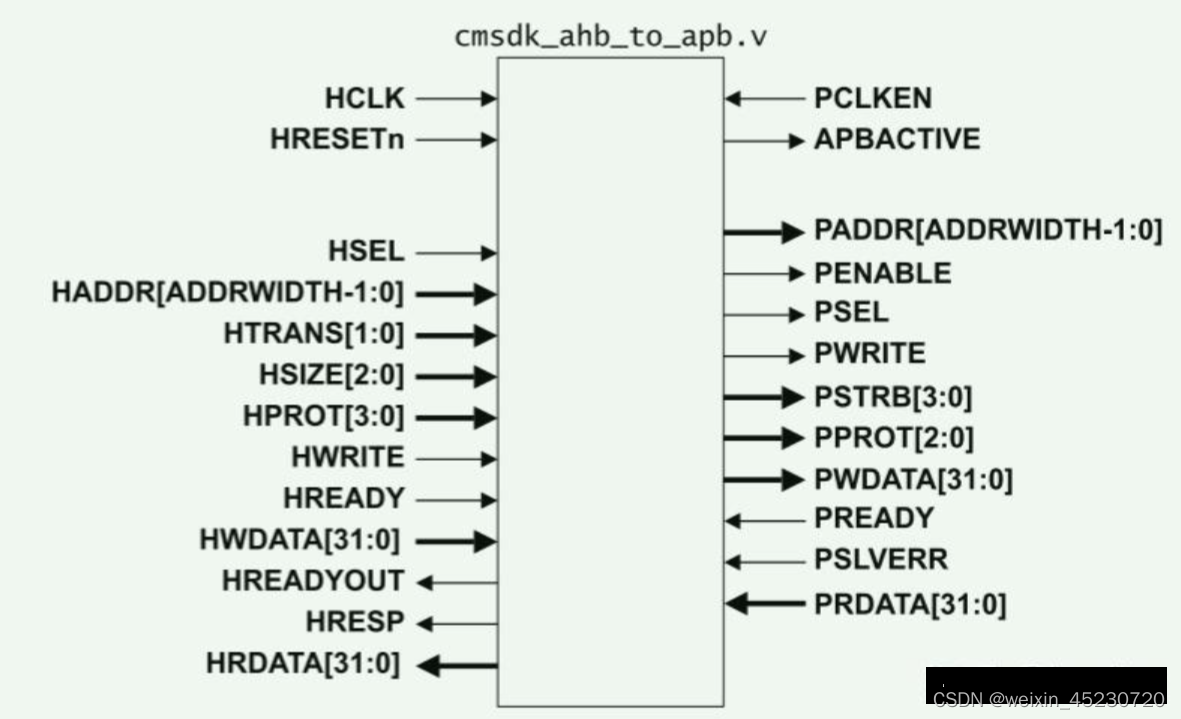

其接口如下图所示,可以看到其完成了AHB协议到APB协议的转换,并且是单对单的,即连接一个AHB主设备、一个APB从设备。

2.2、AHB2APB同步桥的信号接口

2.2.1 系统信号接口

2.2.2 AHB BUS一侧的接口信号(AHB Slave接口信号)

有关AHB的详细协议介绍参考AMBA总线部分,此部分仅介绍模块已有的接口信号

2.2.3 APB BSU一侧的接口信号 (APB Master接口)

2.2.4 特殊型号说明

2.4.1 APBACTIVE信号:同步桥的工作状态信号

APBACTIVE = 1, 说明此时同步桥处于工作状态,有信号在AHB和APB之间传输

APBACTIVE可以用作APB子系统时钟门控信号,供外设做低功耗处理。

2.4.2 PCLKEN信号:(处理PCLK与HCLK之间的关系,需要控制PCLKEN信号)

如果PCLK = HCLK,则PCLKEN 输入1;如果PCLK = 1/2 HCLK,则PCLKEN = PCLK

如果需要HCLK = N * PCLK,那么PCLKEN 需要在PCLK的上升沿的前一拍置位

在不增加逻辑复杂度的情况下,在一定程度上,增加了总线的灵活性,降低了功耗

2.4.3 AHB中的HREADY信号:

作为AHB的从机,从机必须由一个输入ready和一个输出ready信号

HREADY信号: 同步桥的输入信号,外部AHB仲裁器收集各个AHB Slave设备的HREADYout信号,然后做出判断,在送给Slace 端口。表示AHB总线是否READY

HREADYout信号:同步桥的输出信号。代表同步桥是否准备好接收或者发送数据。在同步桥的数据转换中,APB读写操作至少需要两个时钟周期,设计时需要让AHB在合适的时候拉低HREADYout信号,添加合适的等待周期,从而实现AHB到APB的数据转换。

2.4.4 AMBA APB 3.0信号

PREADY

APB Slave通过PREADY信号直接来告诉master,Slave的Ready状态。如果PREADY为高,表示可以接收读写操作,如果PREADY为低,表示Master需要等待

PSLVERR

加入Slave反馈给Master Error 反馈功能

2.4.5 AMBA APB 4.0信号

PSTRB[3:0]

在写操作中,用来指示,byte lane (即多bit字节中哪一个字节是有效的)

在读操作应该改全1,读操作不考虑

PPROT[2:0]

在新版的 APB 4.0协议中,可以采用作为外设访问权限的设置

1. PPROT[0]:0:正常可以访问;1:私有访问,特权级别

2. PPROT[1]:0:安全访问;1:非安全访问

3. PPROT[2]:0:数据;1:指令

3、AHB2APB同步桥的设计参数

定义一些参数,来让代码更加灵活,便于修改

ADDRWIDTH:16, 地址空间,对应64 KB的寻址空间

REGISTER_WDATA: 1, (主要定义AHB到APB在数据传输是否对寄存器需要处理)

优点:AHB2APB的同步桥PWDATA会变成寄存器输出,有利于时序优化

缺点:会增加HWDATA到PWDATA的输出延迟

REGISTER_RDATA: 1 (主要定义APB到AHB输出的读数据做寄存器处理)

优点:AHB2APB的同步桥PRDATA会变成寄存器输出,有利于时序优化

缺点:会增加PRDATA到HRDATA输出延迟

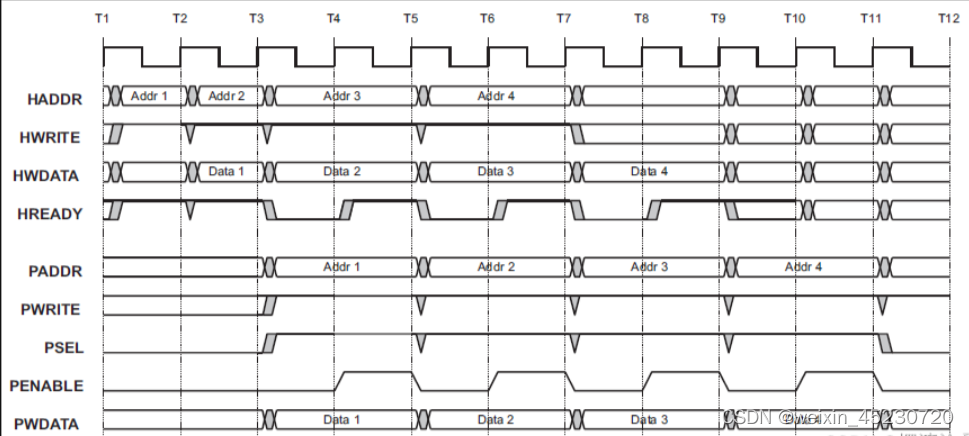

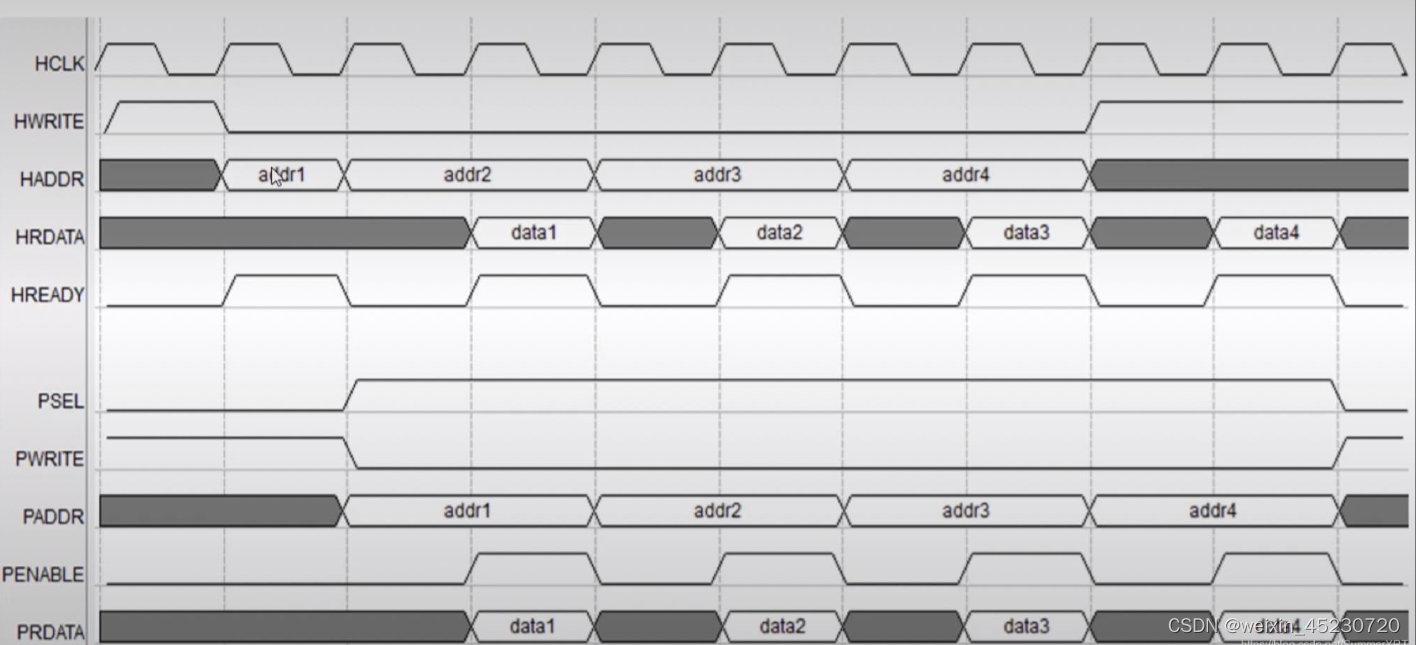

4、AHB2APB同步桥的时序图

4.1 burst写传输:

AHB这一侧,每个一个时钟周期会受到一个HREADY = 0的信号,等待APB将数据写入

4.2 读操作

shuomin

shuomin

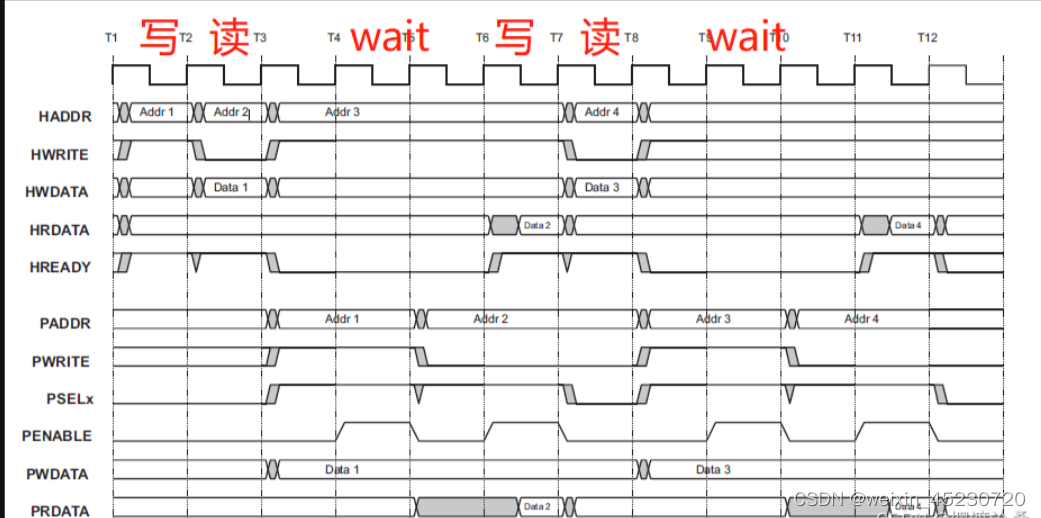

4.3 back-back 传输(写读循环)

不经常出现一个写,接着一个读传输

5,AHB2APB Bridge 的状态机

5.1 首先是第一种情况,

输入、输出不寄存

此状态机:

- 输入(wdata)、输出数据(rdata)均不需要寄存一拍;

- 不考虑 pslverr 情况;

输入输出数据不寄存且不产生错误的情况下。这种情况下其实和之前讲的APB状态机基本是一样的。大家想想看,AHB的通信和APB实际上本来就是差不多的,不过AHB可以支持流水,APB不支持流水。此外AHB可以突发传输,APB不可以突发传输。对于突发上述模块直接没有相应接口,对于输入是流水的情况,实际上会反压前级,只能按照APB的方式进行传输。因此转接桥和APB协议的状态机一样,总共可以分为三个状态:

- IDLE:空闲状态;外设总线默认在此状态;

- ST_APB_TRNF:传输建立状态;在此状态,将PSEL置为1,并保持到ST_APB_TRANF2状态(即对应setup phase)

- ST_APB_TRNF2:传输状态;在此状态。传输完成时,需要将PENABLE置为1;

其状态机如下图所示:

其状态转换的条件如下所示:

- 路径1:当收到AHB的传输请求,apb_select为1,状态从IDLE跳到ST_APB_TRNF,其中apb_select代表着APB Bridge is selected。在状态跳转的这个周期,还需要采样控制信号,用代码注释的话来说,就是Capture transfer information at the end of AHB address phase

- 路径2:当在APB时钟的上升沿(PCLKEN有效的时候),将PENABLE置为1;(如果PCLK和HCLK时钟相同的话,则直接跳就行)。

- 路径3:完成一次传输后,如果紧跟着下一次传输,状态应该从ST_APB_TRNF2跳回ST_APB_TRNF。

- 路径4:如果完成一次传输后,如果后面没有传输,状态从ST_APB_TRNF2跳到ST_IDLE

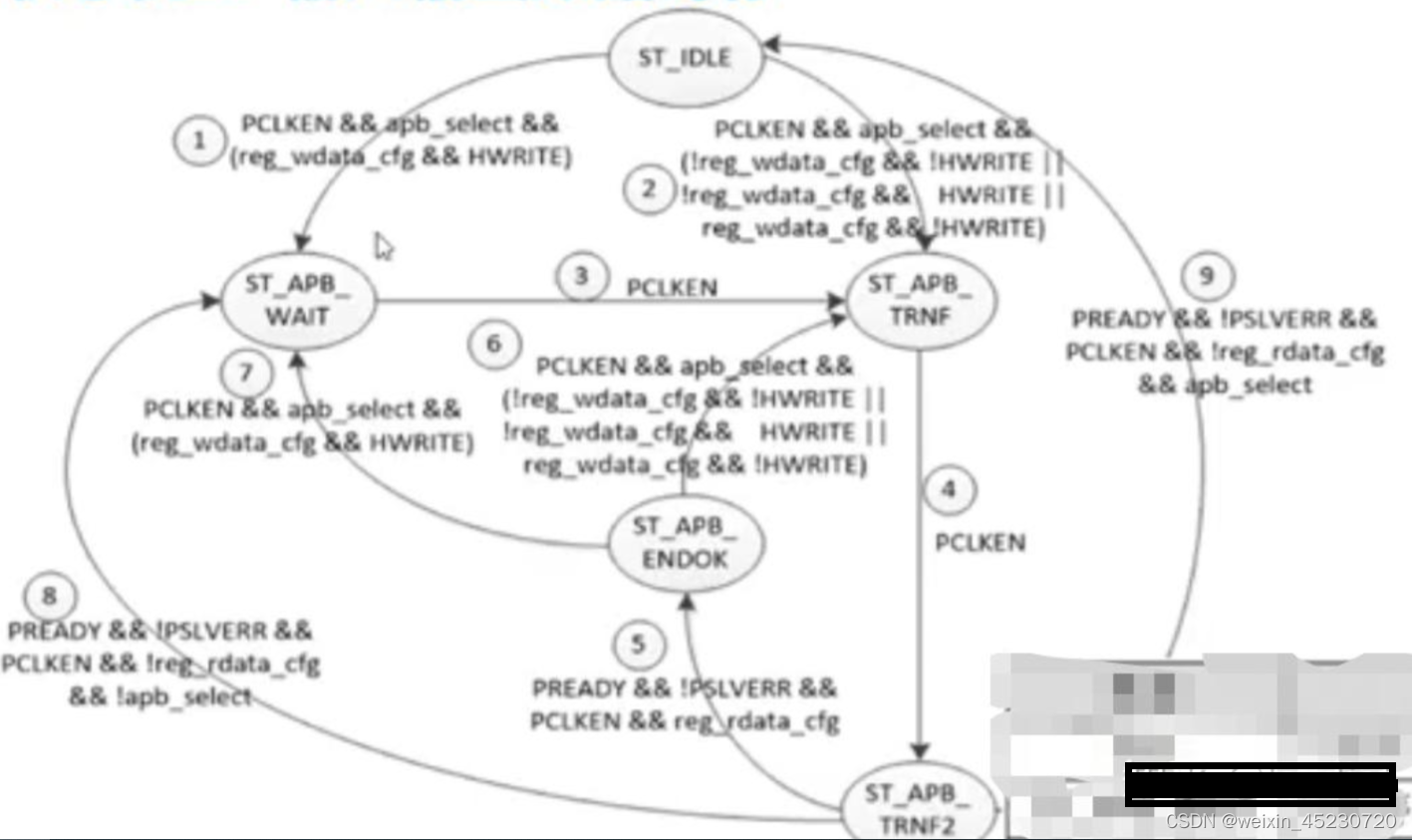

5.2 接下来我们考虑第二种情况,

即输入输出数据需要寄存。

输入、输出数据寄存

此状态机:

- 输入、输出数据均寄存一拍;

- 但不考虑 pslverr 情况;

同时也没有发生错误。(其实大部分情况下都是这种传输方式,因为APB那边很有可能不能够接收数据,因此就需要先将控制信号寄存好)这种情况下,需要增加两个状态,即输入数据需要寄存,输出数据也需要寄存,总共可以分为以下五种状态:

- IDLE:空闲状态;外设总线默认在此状态;

- ST_APB_WAIT:传输等待状态,等待输入数据寄存1拍;

- ST_APB_TRNF:传输建立状态,在此状态,将PSEL置为1,并且保持到ST_APB_TRNF2状态;

- ST_APB_TRNF2:传输状态;在此状态,传输完成的时候,将PENABLE置为1;

- ST_APB_ENDOK:传输结束状态;因为输出寄存1拍,所以传输完成最后1拍需要继续保持传输状态,给出传输信号。

其状态机如下所示:

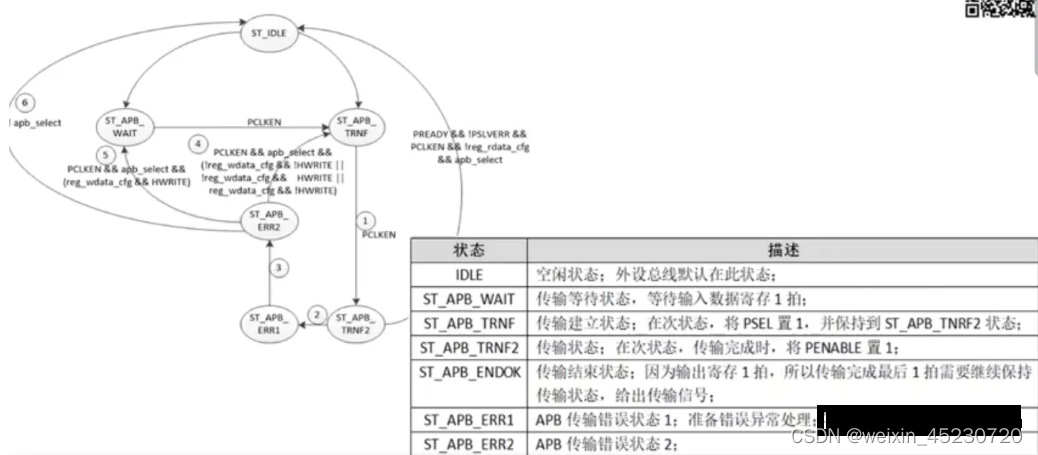

5.3 最后我们考虑第三种情况,

即传输错误的情况。因为这种情况下需要通知AHB主机那边,而AHB的错误响应本身就有两拍,因此这种情况下又需要两个状态,用来准备错误异常处理。这里直接贴图:

5.4 其他的状态

- 读数据寄存,写数据不寄存时,并且存在或不存在pslverr的情况;

- 写数据寄存,读数据不寄存时,并且存在或不存在pslverr的情况

说明注意事项:

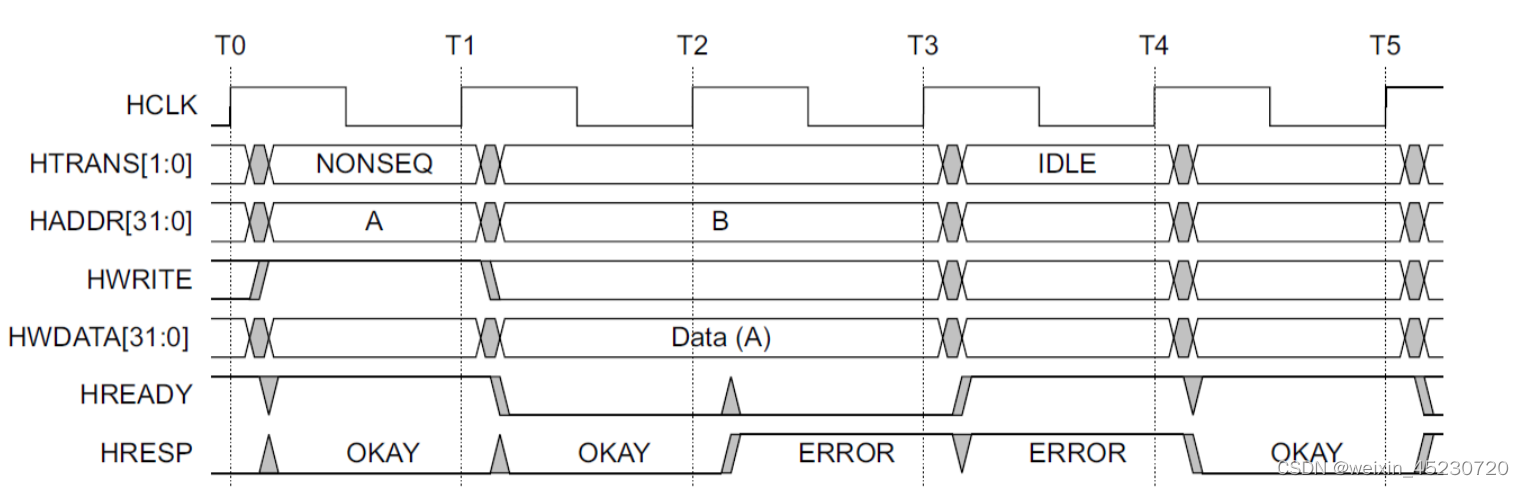

ERROR response

error response拉高的两个周期一定是要发生在HREADY信号上升沿附近。换句话来说,如果要有error response,那就一定要满足HREADY为低的一个周期和为高的一个周期。

跨时钟域的处理

AHB2APB bridge ,典型的SOC中一般AHB子系统的时钟频率在200MHZ,而APB一般在几十KB~几十兆。所以AHB2APB bridge中由高时钟频率向低时钟频率的跨时钟传输需要做处理。

异步FIFO

对于单bit可以通过打两拍或打三拍的方式

握手协议

采用寄存器寄存一拍

SPEC中规定可以将输出数据和输入数据寄存一拍,以此实现高频率传输。尽管增加一拍寄存,使得传输上延迟了一拍。如果设计中的组合逻辑延迟很大,会导致系统频率不能太高,否则会造成时序不满足的情况。当采用寄存器一拍,就会切断过长的组合逻辑的时序路径,可以采用更高的系统时钟频率

6 ,verilog代码参考

参考全网

1487

1487

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?