1 奇偶效验(parity check)

是一种校验代码传输正确性的方法,根据被传输的一组二进制数位中“ 1” 的个数是奇数或者偶数来进行校验。采用奇数校验的称之为奇校验,反之称之为偶校验。采用哪种校验是事先规定的,通常会设置一个奇偶效验位,用它是这组代码中1的个数为奇数或者偶数,若奇校验,接收端,校验“1”的个数是奇数,

偶校验:数据和校验位中“1 ” 的总数为偶数,则数据无误,否则数据有误

奇校验:数据和校验位中“1” 的总数为奇数,则数据无误,否则数据有误。

2 输入数据的校验方法

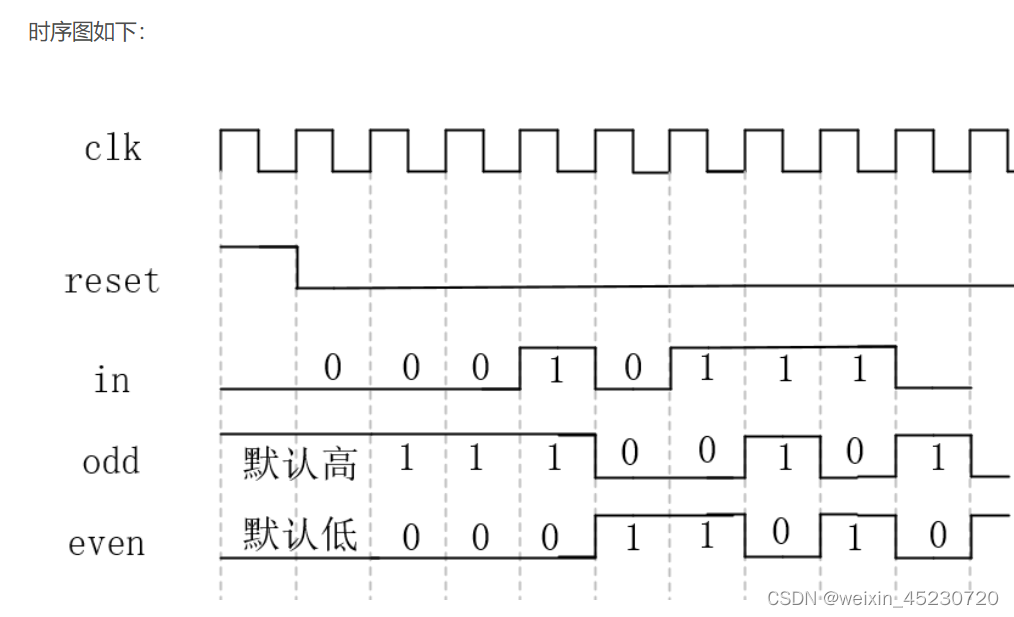

奇校验实现方式:校验位默认为高电平,每检测到1,则状态翻转

偶校验实现方式:校验位默认为低电平,每检测到1,则状态翻转

Verilog实现

module odd_even(

input clk ,

input rst ,

input in ,

output reg odd , // 奇校验

output reg even //偶校验

);

always @(posedge clk ) begin

if(!rst)begin

odd <= 1'b0;

even <= 1'b0 ;

end

else if(in) begin

odd <= ~odd;

even <= ~even ;

end

else

begin

odd <= odd ;

even <= even ;

end

end

endmodule3 输出数据校验方法

偶校验:将输入数据按位异或

奇校验:将输入数据按位异或再取反(与偶校验相反)

module odd_even(

input clk ,

input rst ,

input [7:0] in ,

output reg odd , // 奇校验

output reg even //偶校验

);

always @(posedge clk ) begin

if(!rst)begin

odd <= 1'b0;

even <= 1'b0 ;

end

else begin

odd <= ~^in;

even <= ^in ;

end

end

endmodule总结:

奇偶校验属于一种比较简单的校验方法,效率比较低,没办法纠错和改正。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?