从零开始的FPGA学习(2)

第二个任务:用三八译码器实现一位全加器

基础任务和提高任务

(1)基础任务:设计一个带有使能端的三八译码器,要求使能端输入由三个,一个高电平输入有效,两个低电平输入有效,输入端是高电平输入有效,输出端是低电平输出有效,即74LS138,拨码开关作为输入,发光二极管作为输出。

(2)提高任务:在基础任务的基础上,输出用一位数码管显示输出是第几位。

首先第一步:我们需要实现一个三八译码器

什么是三八译码器?数电的知识,稍微复习一下。

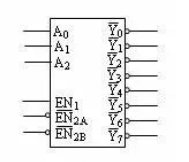

下图便是一个常见的三八译码器,和基础任务相对应其中A0,A1,A2三个输入端,Y0-7为八位输出端,EN1,EN2A,EN2B为三位使能端后两个端口和八位输出低电平有效(既:为 0 时有效)

***三八译码器真值表:***

三八译码器源文件

接下来实现三八译码器

1.源文件:(包括提高任务中的输出数码管)

module Decoders(A,E1,E2_low,E3_low,Y_low,sem);

input [2:0] A; //3位输入

input E1; //高电平有效使能端

input E2_low; //低电平有效使能端

input E3_low; //低电平有效使能端

output reg[7:0] Y_low; //8位输出,低电平有效

output reg[6:0] sem; //一位数码管显示输出是第几位 7段数码管

//在always模块中的被赋值变量均为寄存器类型!

always @ (A or E1 or E2_low or E3_low) //行为语句模块,敏感信号

begin

if(E1 && ~E2_low && ~E3_low) //使能输入有效

case(A)

3'b000 : Y_low = 8'b11111110;

3'b001 : Y_low = 8'b11111101;

3'b010 : Y_low = 8'b11111011;

3'b011 : Y_low = 8'b11110111;

3'b100 : Y_low = 8'b11101111;

3'b101 : Y_low = 8'b11011111;

3'b110 : Y_low = 8'b10111111;

3'b111 : Y_low = 8'b01111111;

default : Y_low = 8'b11111111;

endcase //case模块结束

else //使能端无效情况

Y_low = 8'b11111111;

end //if模块结束

always @ (A or E1 or E2_low or E3_low) //7段数码管显示哪一位输出

begin

if(E1 && ~E2_low && ~E3_low)

case(A)

3'b000 : sem = 7'b0111111;

3'b001 : sem = 7'b0000110;

3'b010 : sem = 7'b1011011;

3'b011 : sem = 7'b1001111;

3'b100 : sem = 7'b1100110;

3'b101 : sem = 7'b1101101;

3'b110 : sem = 7'b1111101;

3'b111 : sem = 7'b0000111;

default

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?