一、三八译码器

1、三八译码器简介

38译码器是一种数字逻辑电路,用于将3位二进制输入编码为8位输出。它的作用是将特定的输入模式映射到相应的输出。在数字电路设计和信息处理中,38译码器是一个常见且有用的组件,可以帮助实现数据的解码和选择性输出。

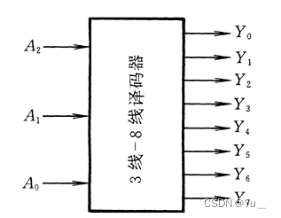

2、三八译码器结构及其真值表

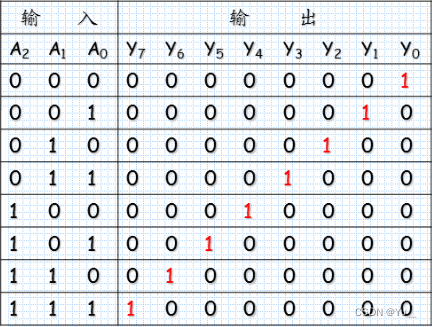

真值表:

3-8译码器由三个输入引脚和八个输出引脚组成。输入引脚是A0、A1和A2,它们可以是0或1。输出引脚是YO到Y7,它们中的一个会被激活,其它的则处于非激活状态。当输入引脚的二进制值为000时,输出引脚YO会被激活。当输入引脚的二进制值为001时,输出引脚Y1会被激活,以此类推,直到输入引脚的二进制值为111时,输出引脚Y7会被激活。

3、Verilog代码

if-else版本:

module decoder3_8(

input wire a,b,c,

output reg [7:0] out

);

always@(*)

if({a, b, c}==3'b000)

out=8'b0000_0001;

else if( {a, b, c} ==3'b001)

out=8'b0000_0010;

else if( {a, b, c} ==3'b010)

out=8'b0000_0100;

else if( {a, b, c} ==3'b011)

out=8'b0000_1000;

else if( {a, b, c} ==3'b100)

out=8'b0001_0000;

else if( {a, b, c} ==3'b101)

out=8'b0010_0000;

else if( {a, b, c} ==3'b110)

out=8'b0100_0000;

else if( {a, b, c} ==3'b111)

out=8'b1000_0000;

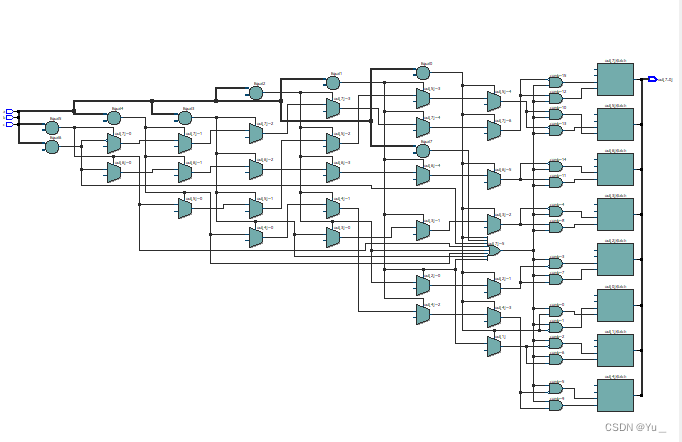

endmodule其RTL图如下:

case版本:

module decoder3_8(

input wire a,b,c,

output reg [7:0] out

);

always@(*)

case({a,b,c})

3'b000: out=8'b0000_0001;

3'b001: out=8'b0000_0010;

3'b010: out=8'b0000_0100;

3'b011: out=8'b0000_1000;

3'b100: out=8'b0001_0000;

3'b101: out=8'b0010_0000;

3'b110: out=8'b0100_0000;

3'b111: out=8'b1000_0000;

endcase

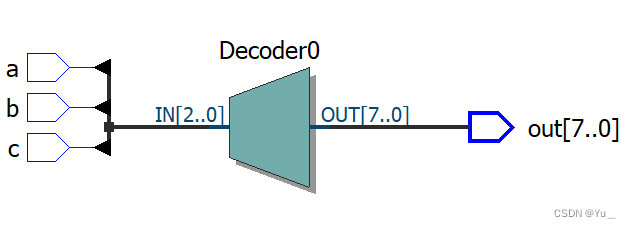

endmodule其RTL图:

二、全加器

1、一位全加器

(1)简介

全加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器。

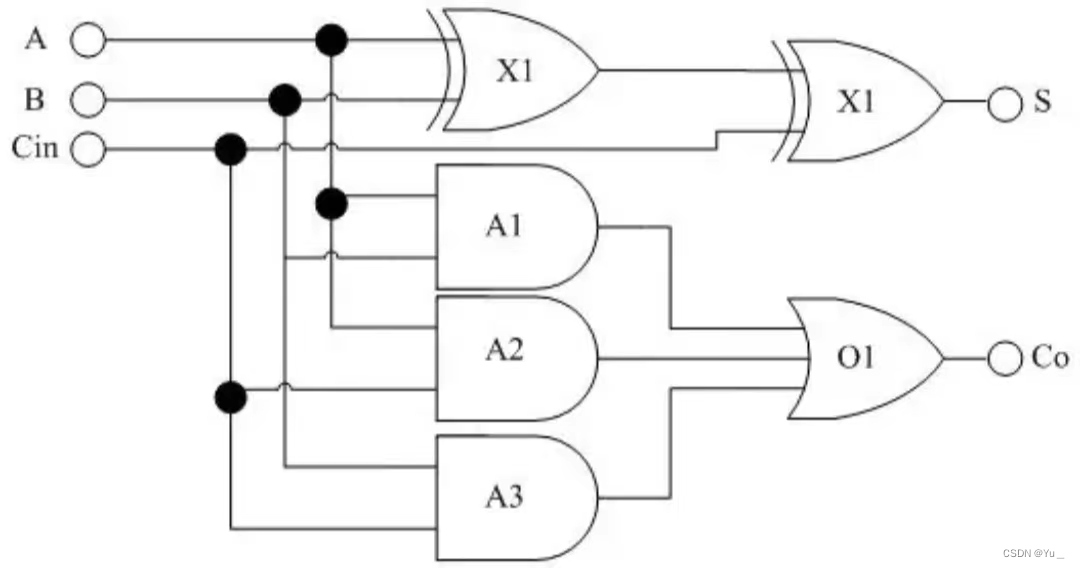

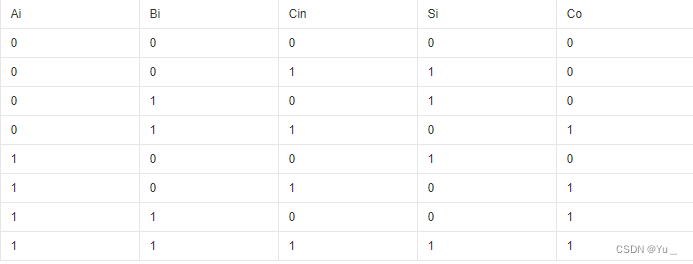

其结构图如下:

一位全加器的逻辑表达式为

S=A⊕B⊕Cin

Co=Cin(A⊕B)+AB

其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;

Verilog代码:

module adder_1bit(

input a,b,cin,

output wire f,cout

);

assign f=a^b^cin;

assign cout=(a&b)|(a&cin)|(b&cin);

endmodule

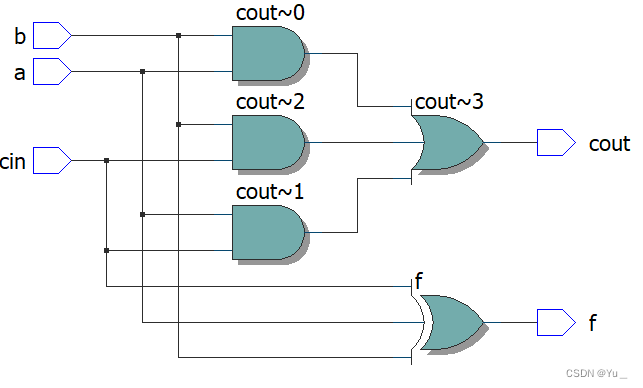

RTL图:

2、四位全加器

Verilog代码:

module A4bit(

input a,b,cin,

output wire f,cout

);

assign f=a^b^cin;

assign cout=(a&b)|(a&cin)|(b&cin);

endmodule

module _4add(

input [3:0] a,b,

input cin,

output [3:0] c,

output out

);

wire [3:1] tem;

one_add (a[0],b[0],cin,c[0],tem[1]),

(a[1],b[1],tem[1],c[1],tem[2]),

(a[2],b[2],tem[2],c[2],tem[3]),

(a[3],b[3],tem[3],c[3],out);

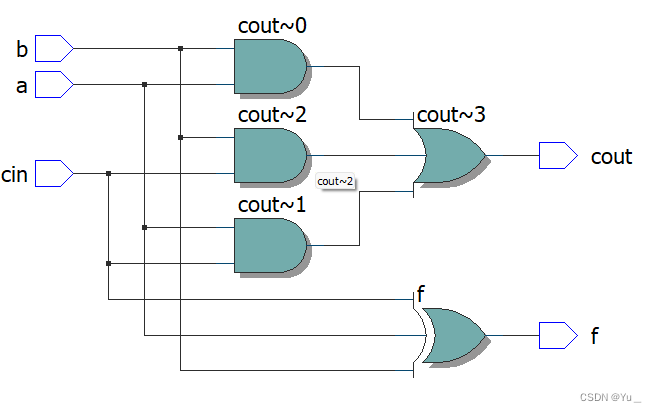

endmoduleRTL图:

3、八位全加器

Verilog代码:

module A8bit(

input a,b,cin,

output wire f,cout

);

assign f=a^b^cin;

assign cout=(a&b)|(a&cin)|(b&cin);

endmodule

module _8add(

input [7:0] a,b,

input cin,

output [7:0] c,

output out

);

wire [7:1] tem;

one_add (a[0],b[0],cin,c[0],tem[1]),

(a[1],b[1],tem[1],c[1],tem[2]),

(a[2],b[2],tem[2],c[2],tem[3]),

(a[3],b[3],tem[3],c[3],tem[4]),

(a[4],b[4],tem[4],c[4],tem[5]),

(a[5],b[5],tem[5],c[5],tem[6]),

(a[6],b[6],tem[6],c[6],tem[7]),

(a[7],b[7],tem[7],c[7],out);

endmodule

因不明原因,RTL图与上述四位全加器RTL图相同,若有大佬知道,欢迎指出原因,谢谢。

5887

5887

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?