内容包含时序逻辑电路(序列发生器)的FPGA实现

前言

用FPGA生成序列11001,用灯的闪烁的为生成的信号

一、画图

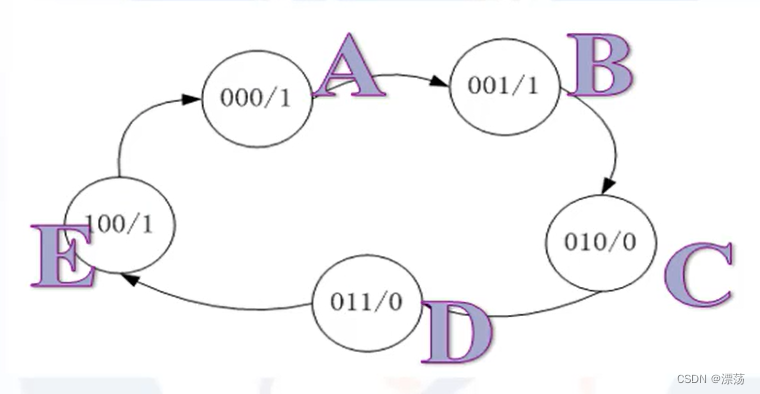

1 绘制状态图

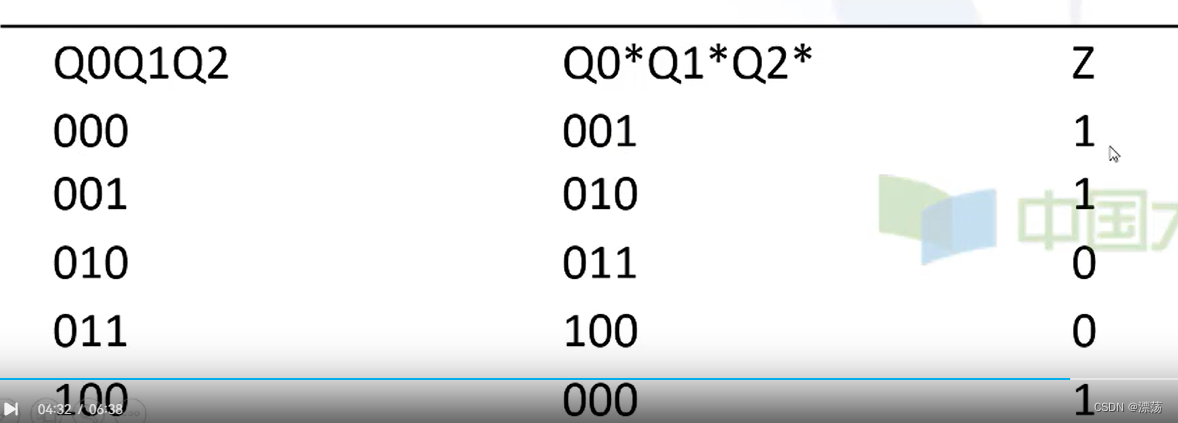

2 绘制状态转移表

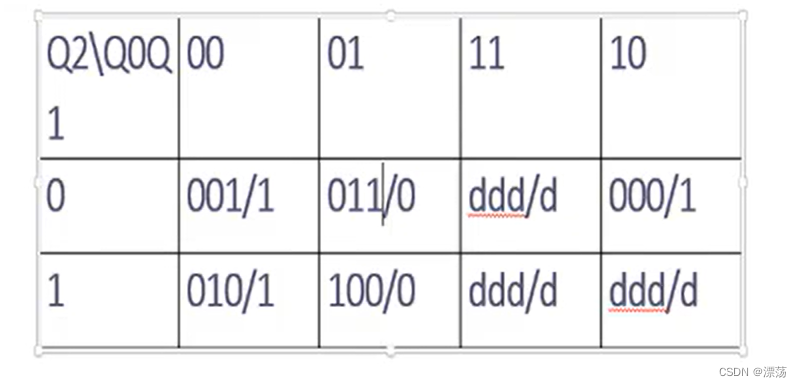

3 绘制次态卡诺图

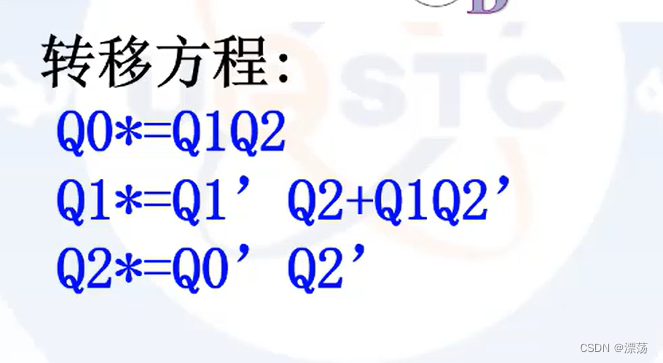

4 得到转移方程

次态卡诺图画法参照:https://blog.csdn.net/zhendianluli/article/details/127132215

二、fpga设计、仿真、约束

1.设计代码

代码如下(示例):

module v_seq11001(

input clk,

output led

);

reg [31:0]clk_cnt=0;

reg clk_div=0;

reg q0=0;

reg q1=0;

reg q2=0;

wire led=0;

always@(posedge clk) begin

/* system clk is 50M, it uses 1HZ */

if (clk_cnt==25) begin

clk_div=~clk_div;

clk_cnt=0;

end

else begin

clk_cnt=clk_cnt+1;

end

end

assign led=~q1;

always@ (posedge clk_div) begin

q0<=q1&q2;

q1<=~q1&q2|q1&~q2;

q2<=~q0&~q2;

end

endmodule

进行时钟分频,主频50MHz,分频之后1MHz

2.仿真代码

代码如下(示例):

module sim_seq;

reg clk;

wire led;

v_seq11001 u1 (clk,led);

initial begin

clk=1;

end

always #10 clk=~clk;

endmodule

3.约束代码

代码如下(示例):

## clk

set_property PACKAGE_PIN D4 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

## LED

set_property PACKAGE_PIN P9 [get_ports led]

set_property IOSTANDARD LVCMOS33 [get_ports led]

endmodule

总结

提示:这里对文章进行总结:

例如:以上就是今天要讲的内容,本文仅仅简单介绍了pandas的使用,而pandas提供了大量能使我们快速便捷地处理数据的函数和方法。

4328

4328

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?