原理图

-

工程保存路径及名称不能含有中文

-

Cadence17.4打开低版本.brd文件提示The design was last saved using version 15 and must be updated using DC Doct

解决:https://blog.csdn.net/xiangkui0555/article/details/113760343

-

修改原理图color、grid等参数

解决:Options-preferences

-

设置原理图整体页面Fonts、tittle block等参数

解决:Options-Design Template

-

放置管脚后框选-右键-Edit Pins在表中修改管脚属性

-

homogeneous类型元件原理图创建,Ctrl+N切换下一个部分

-

homogeneous类型元件在原理图中使用时需要添加属性来标记哪些是一组,如下

-

cadence软件自带的原理图库一般是这个路径:

安装路径\Cadence\Cadence_SPB\tools\capture\library

-

旋转元件方向快捷键:R

-

画悬空wire:在悬空位置双击;画非直角wire:按住Shift

-

w快捷键画wire;j快捷键画电气连接节点

-

在同一个原理图内相距较远的连接线可用相同的名称表示连接关系

-

总线画法Place bus——Place net alias(ED[0..31])——Place bus Entry(F4快捷键)

-

页面之间互联用 Place Off-Page Connector(名称一样表示连接)

-

浏览所有parts、nets、offpage connector、DRC makers

选中xxx.dsn文件,Edit-browse

parts:检查元件名称和值

nets:检查网络 尤其是电源

offpage connector:检查页面之间连接关系

DRC makers:定位错误

-

搜索:Ctrl+F(flat net 比net更直观)

-

批量替换、更新原件:在Design Cache中选中元件右键replace cache、update cache

-

清除原理图中已经删除的元件缓存:Design Cache右键Cleanup Cache

-

选择多个元件:按住Ctrl点选/直接框选

-

不带连接关系移动原件:按住Alt键点选拖动

-

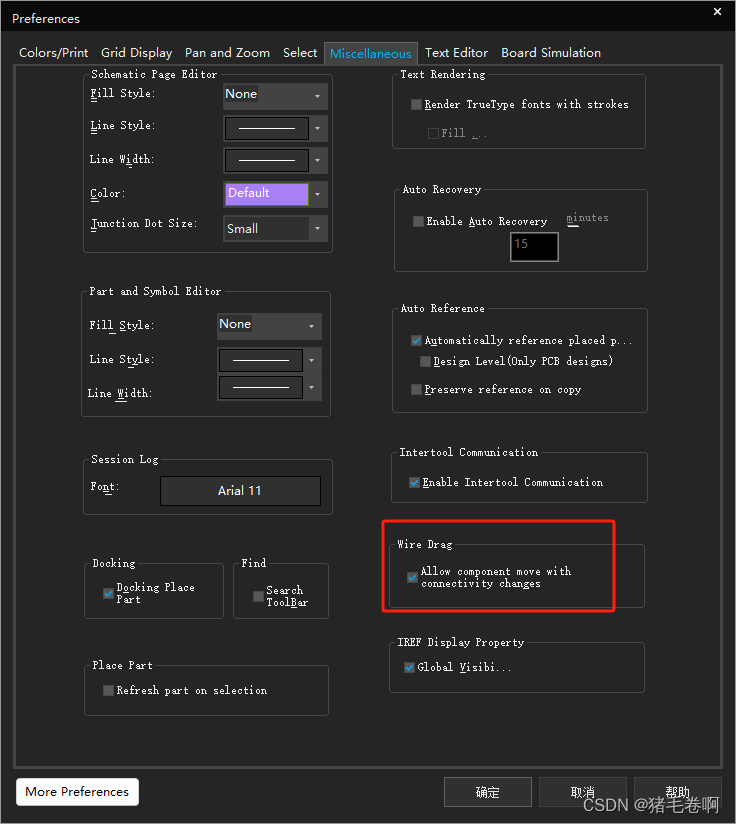

移动元件和wire建立连接是勾选下图选项

-

元件镜像:快捷键H左右/V上下

-

拷贝、粘贴、删除同Windows;快速复制:按住Ctrl点选拖动

-

放置文本换行:按住Ctrl+Enter

-

放置无电气连接的图形:如下图

-

为单个元件添加FootPrint属性:

-

双击在package properties中键入

-

在元件库中为元件添加属性,然后在Design Cache中replace

-

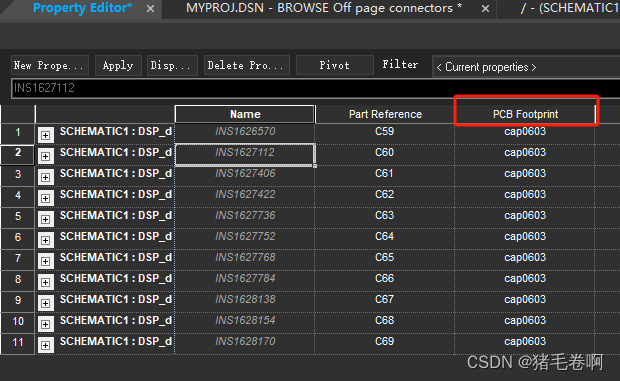

批量为元件添加FootPrint属性:

批量选择元件,右键Edit Properties,点选下图位置统一修改

-

元件属性竖排显示:点击左上角方框右键点击Pivot

-

查看当前原理图页面中所有元件属性:点选原理图名称,右键Edit Object Properties(工程文件也一样)

-

生成网表

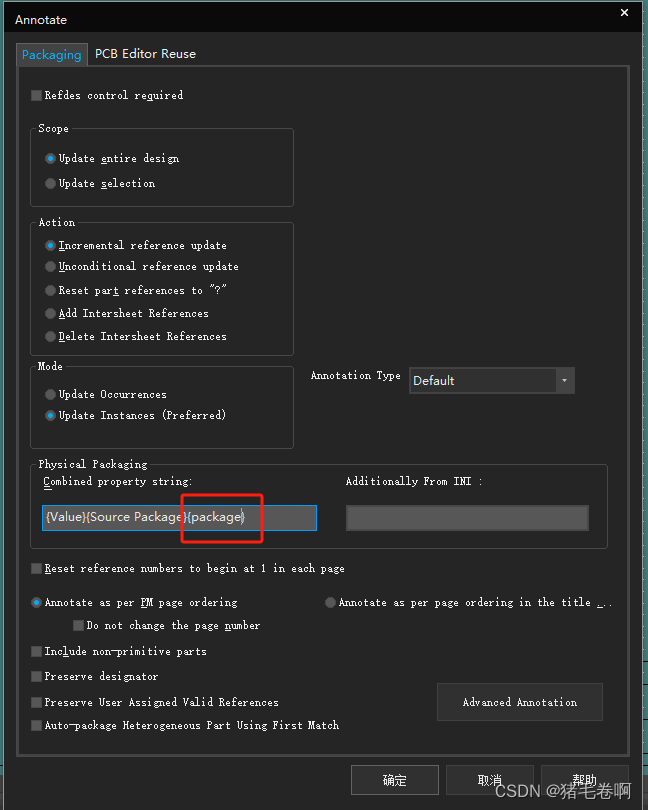

- Tools-Annotate-Reset part references to"?(Scope-designUpdate entire)

- Tools-Annotate-Unconditionsl reference update(Scope-designUpdate entire)

- 通篇检查DRC(点击下图图标)

4.Tools-create netlist

-

生成元件清单

方法一:点选.dsn文件,Report——Cis bill of materials——Standard

方法二:Tools——Bill of materials(区别:会把相同值的放在一起并显示个数)

-

打印出图

快捷键:Ctrl+P

PCB

-

PCBM LP VIEWER (10.5)资源:

链接:https://pan.baidu.com/s/12wE7czTKzuzcOGjqDvnQLQ?pwd=bnlx

提取码:bnlx

-

smd焊盘制作

1.打开Padstack Editor

2. File-new填写焊盘名称、保存路径、焊盘类型

3.在左下角把单位Unit改成Millimeter

Start:SMD、Rectangle

Design Layers:Width、Height

Mask Layers:SOLDERMASK TOP(阻焊层)比正常长宽大0.1

PASTEMASK TOP(加焊层)

4.保存,退出Padstack Editor

-

Layout-Pins不出现Options对话框

解决:View-Windows-勾选show All

-

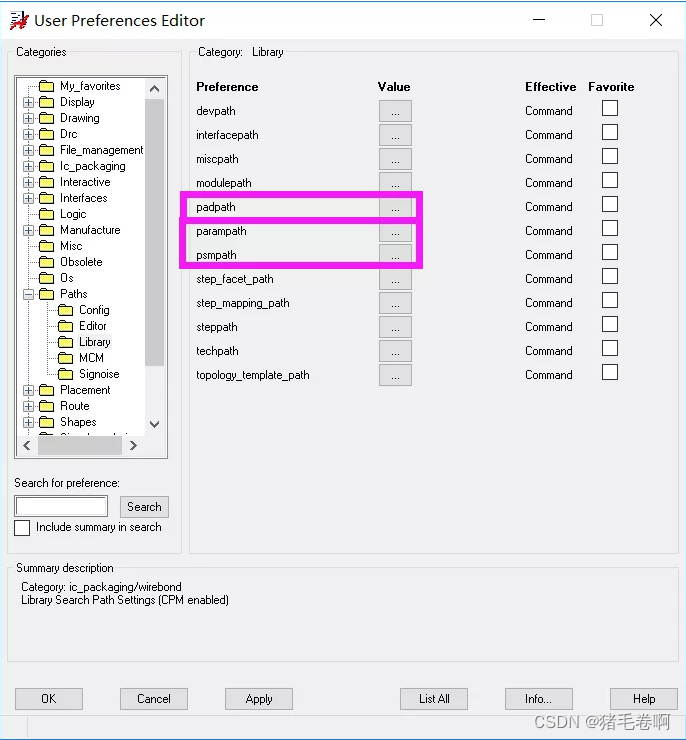

找不到自己的封装

解决:Setup-Preferences,设置下图方框中的路径为保存封装的路径,并检查保存的封装文件后缀是否为.pad

-

design parameter editor中的extents参数设置无效

解决:设置方式先把视野放大,再输入

2989

2989

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?