文章目录

- 概要

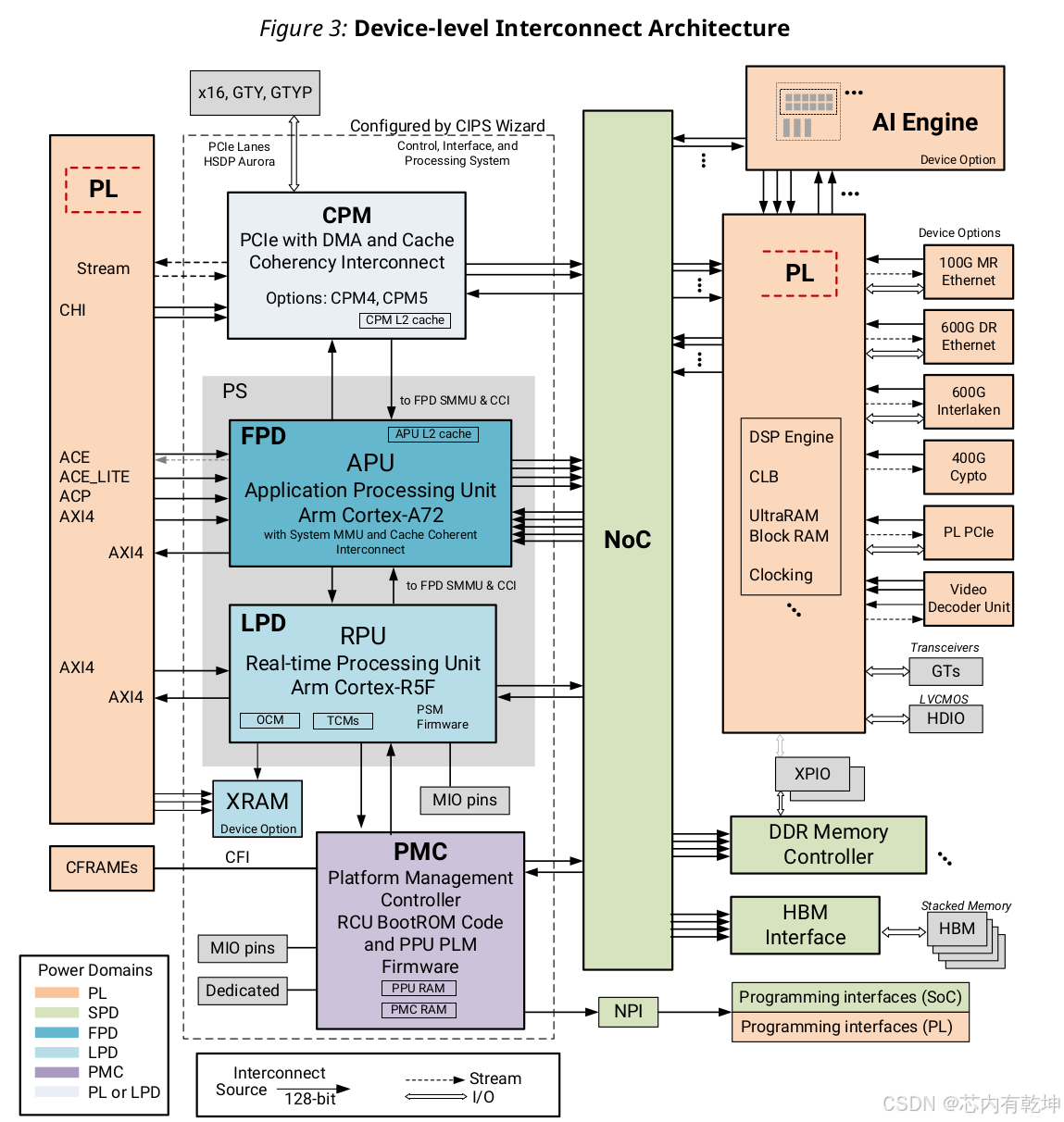

- 整体架构

- 专有名词解释

- IP配置

- 总结

概要

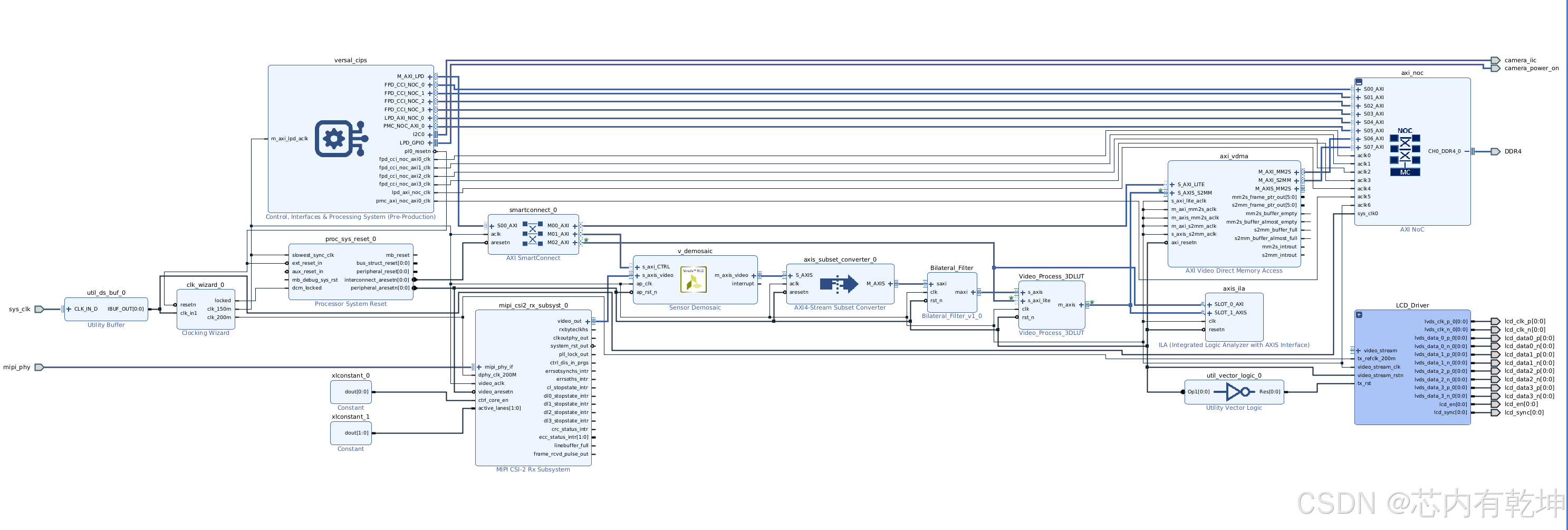

此demo工程基于Alinx的V100板卡(xcve2302-sfva784-1LP-e-S)搭建,使用AN5020摄像头模组(sensor型号:OmniVision (OS05A20)采集RAW10格式的视频图像,经过MIPI(4 lane)接口给到Versal,在PL端进行视频处理后通过LVDS接口(4lane,7:1)输出到AN7000显示屏(7寸LCD屏、1280*720)实时显示。

Versal ACAP芯片架构与软件开发环境均与之前的器件有所不同,通过此demo重点需要掌握:1)、Versal ACAP的架构;2)、CIPS的配置与使用方法;3)、NoC的配置与使用方法、4)、SDK软件使用方法。

整体架构流程

技术名词解释

CIPS:Control,Interfaces & Processor System

PMC:Platform Management Controller

PS:Processor System

NoC:Network on Chip

IP配置

-

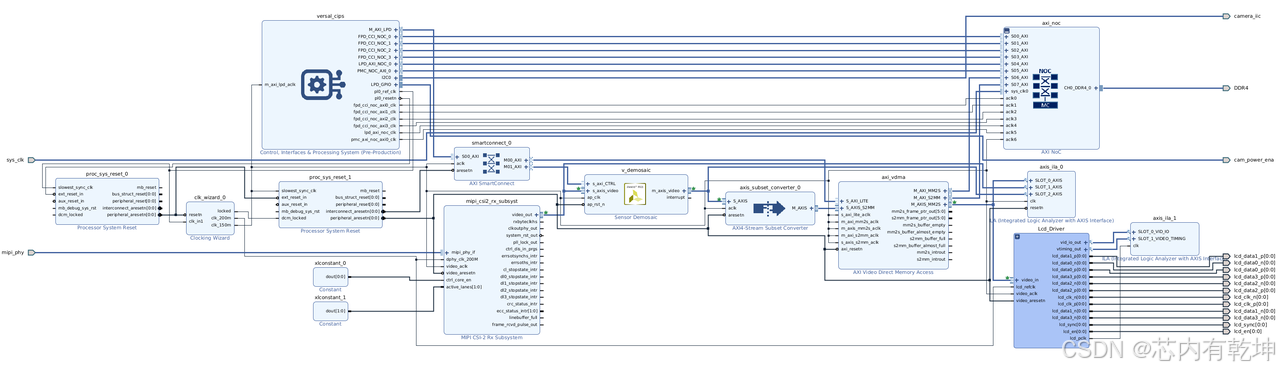

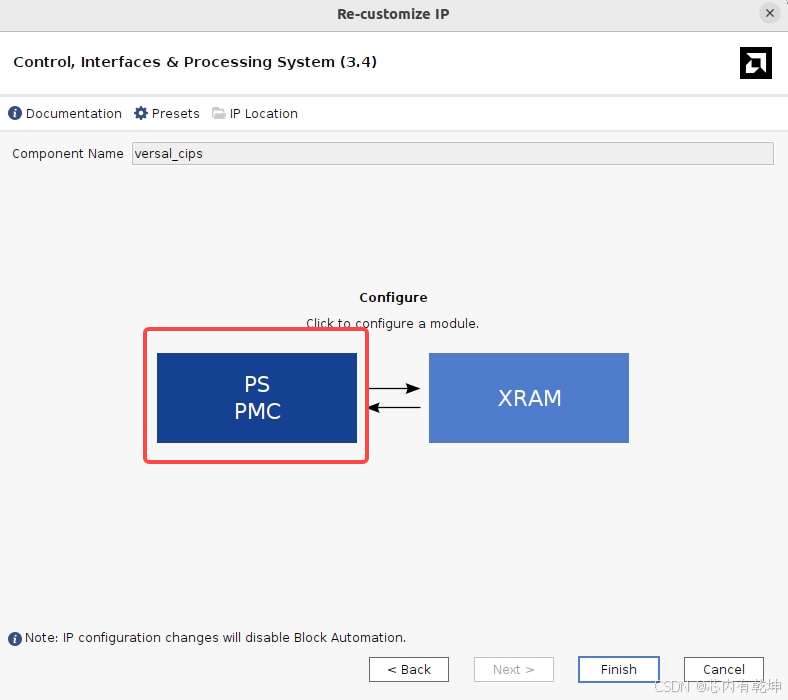

demo使用PS+PL的架构实现,因此,需要使用CIPS(Control,Interface & Processing System),PS的作用主要是初始化摄像头寄存器以及VDMA、Sensor Demosaic的寄存器;

-

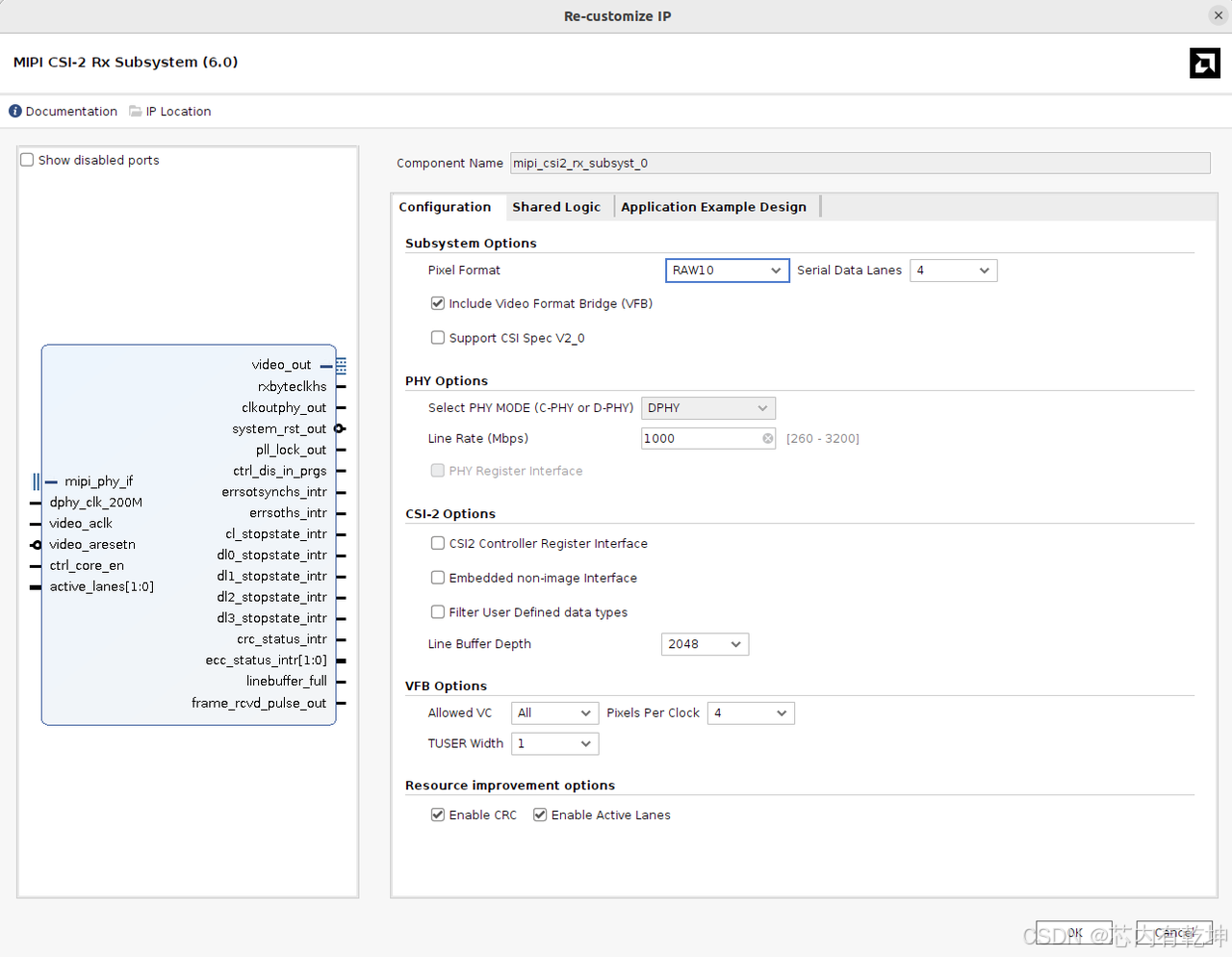

摄像头通过4个lane的MIPI接口输出RAW格式的像素,因此,需要通过MIPI CSI-2 Rx Subsystem接收串行像素bit流,恢复成4个RAW10bit像素;

-

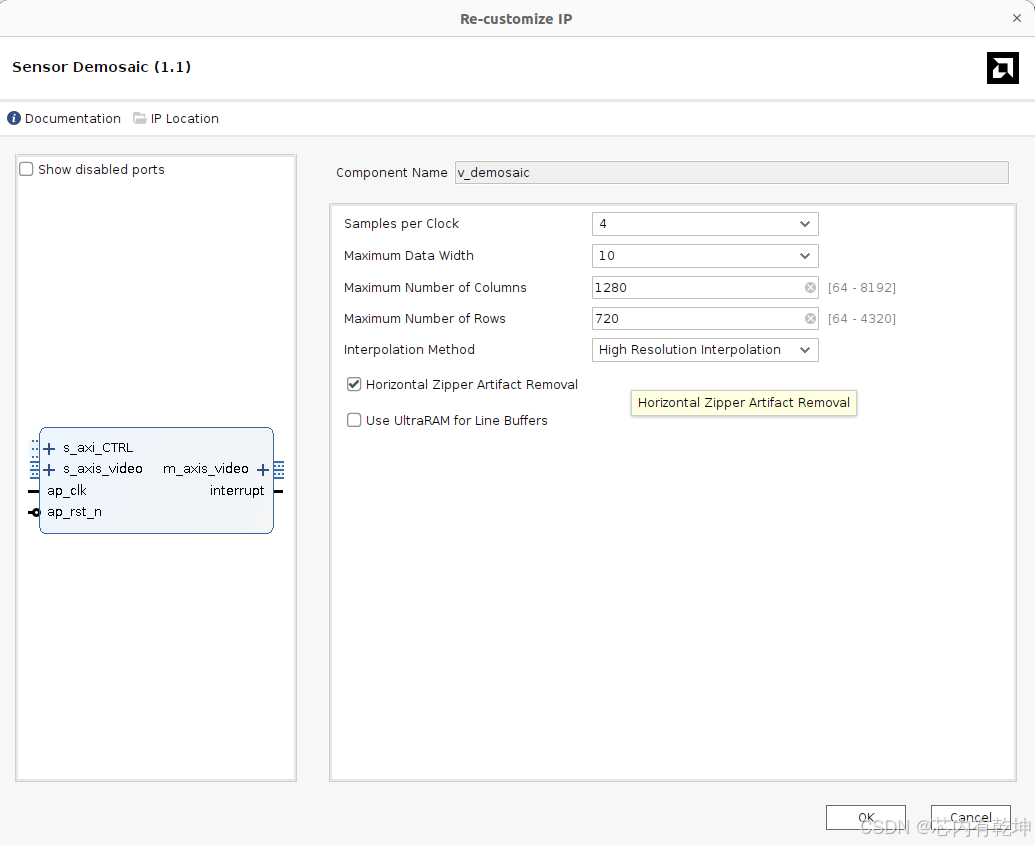

使用Sensor Demosaic将RAW格式数据转为RGB格式数据,插值出每个像素的R、G、B分量;

-

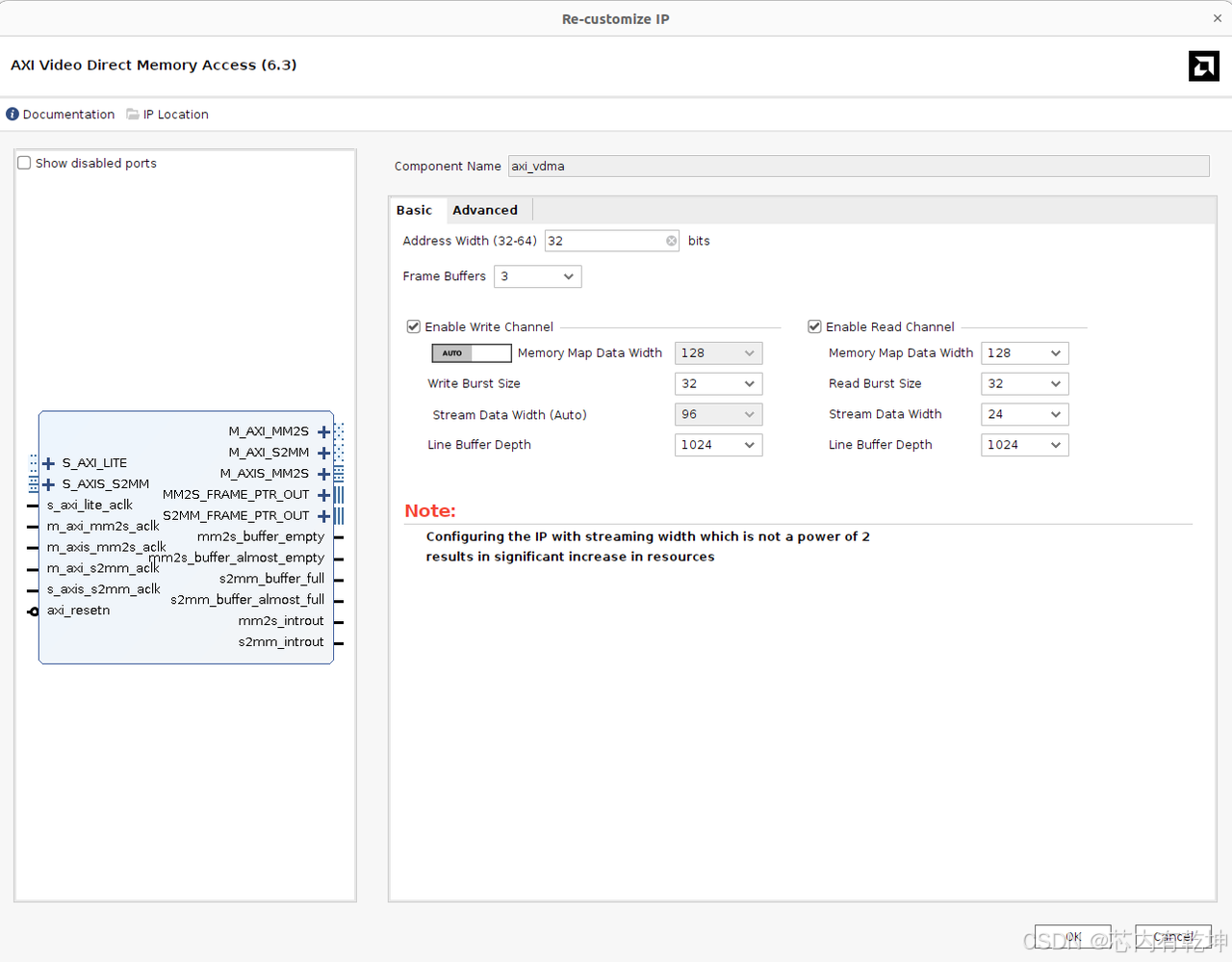

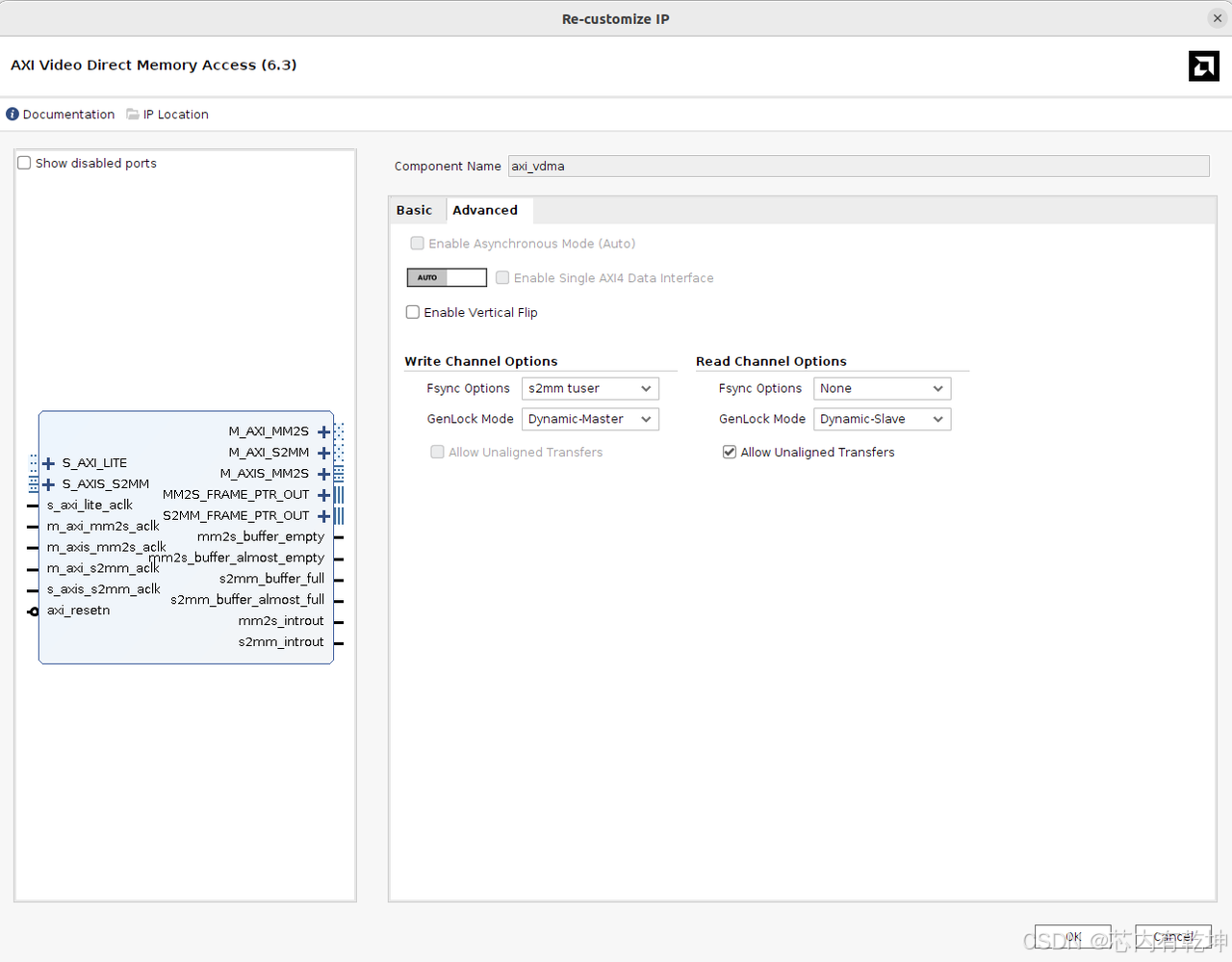

通过VDMA将RGB像素缓存到DDR存储器,因此需要使用VDMA和NoC,为什么必须要使用NoC呢?这是由Versal设备的架构决定的,无论PS还是PL访问DDR存储器都需要通过NoC实现;

-

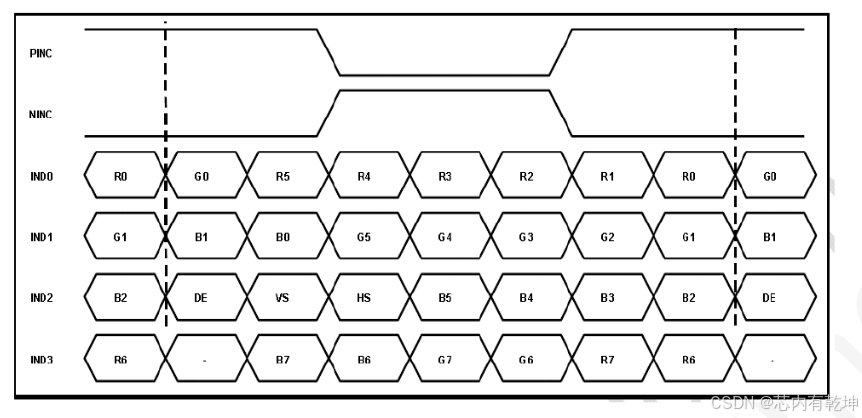

LCD屏幕是LVDS接口,需要通过Video Timing Controller和AXI4-Stream to Video Out产生显示时序,以及LVDS 7:1串化电路(Advanced IO Wizard)将显示时序信息通过4个LVDS lane发送至显示屏。

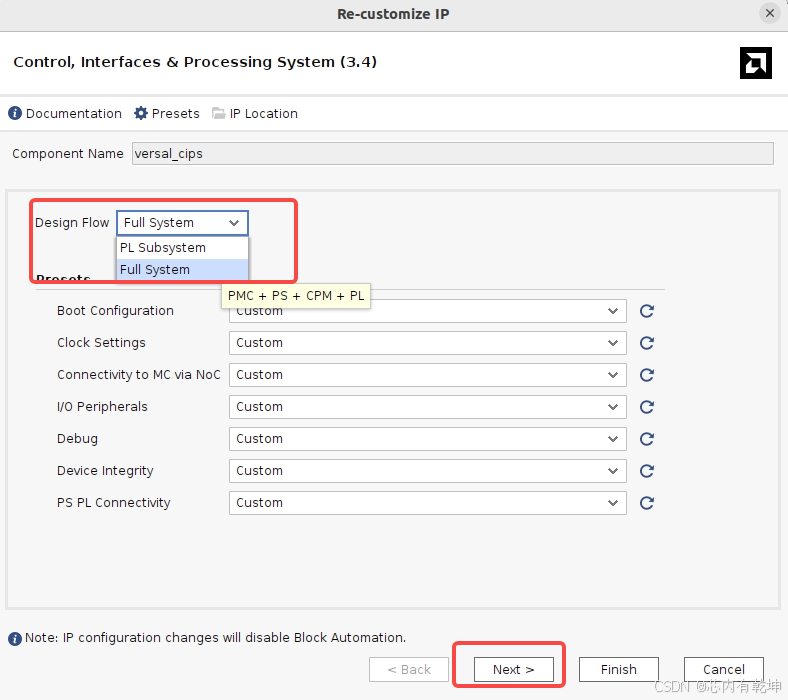

CIPS配置

PL与PS都使用,所以选择Full System;如果只是用PL端的逻辑资源则选择PL Subsystem。接下来是配置PMC,有几项是必须配置的。

-

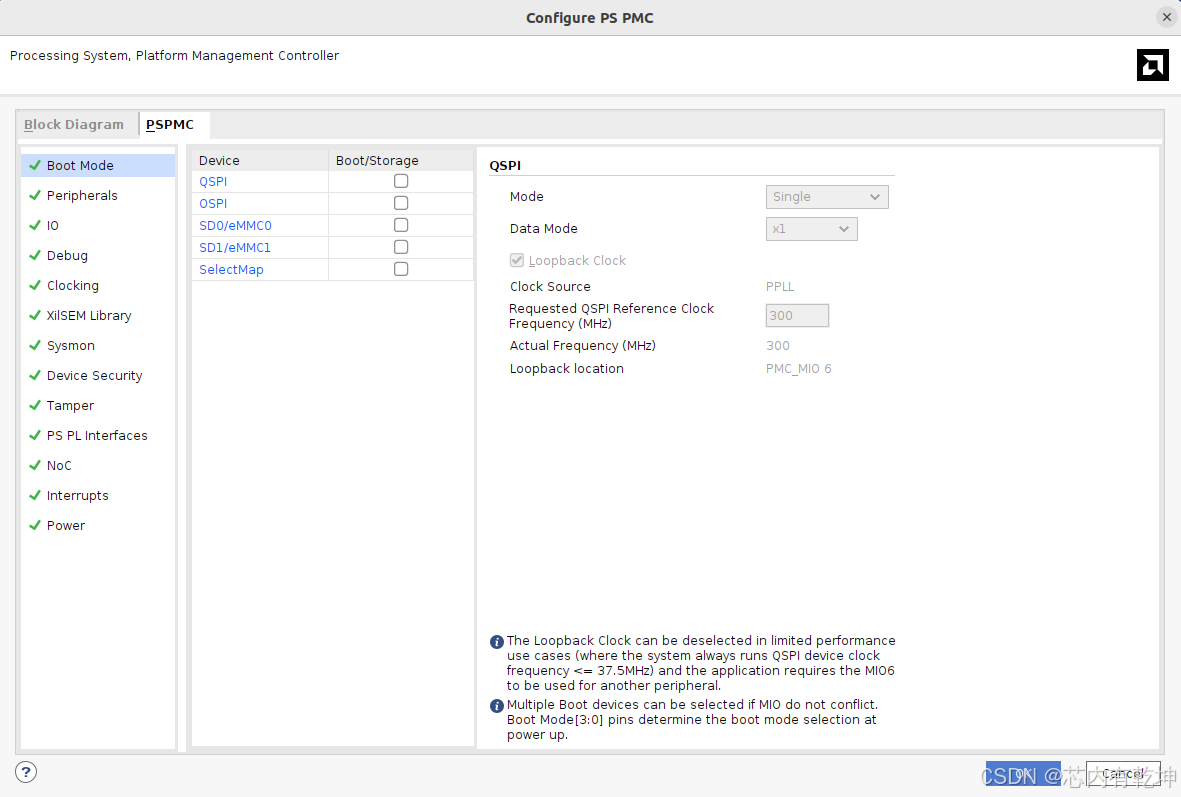

Boot Mode:这个跟我们使用的配置模式有关,例如:直接从JTAG下载启动,则可以不用勾选就行;如果选择使用从SD卡启动,则勾选相应的SD0或SD1选项即可。这里我们选择使用JTAG配置,方便debug,因此,可以不勾选任何一个。提示:具体使用哪种配置模式需要根据硬件板卡确定;例如:V100的SD卡是连接的SD1控制器,因此,如果要使用SD卡启动模式需要配置SD1/eMMC1。

-

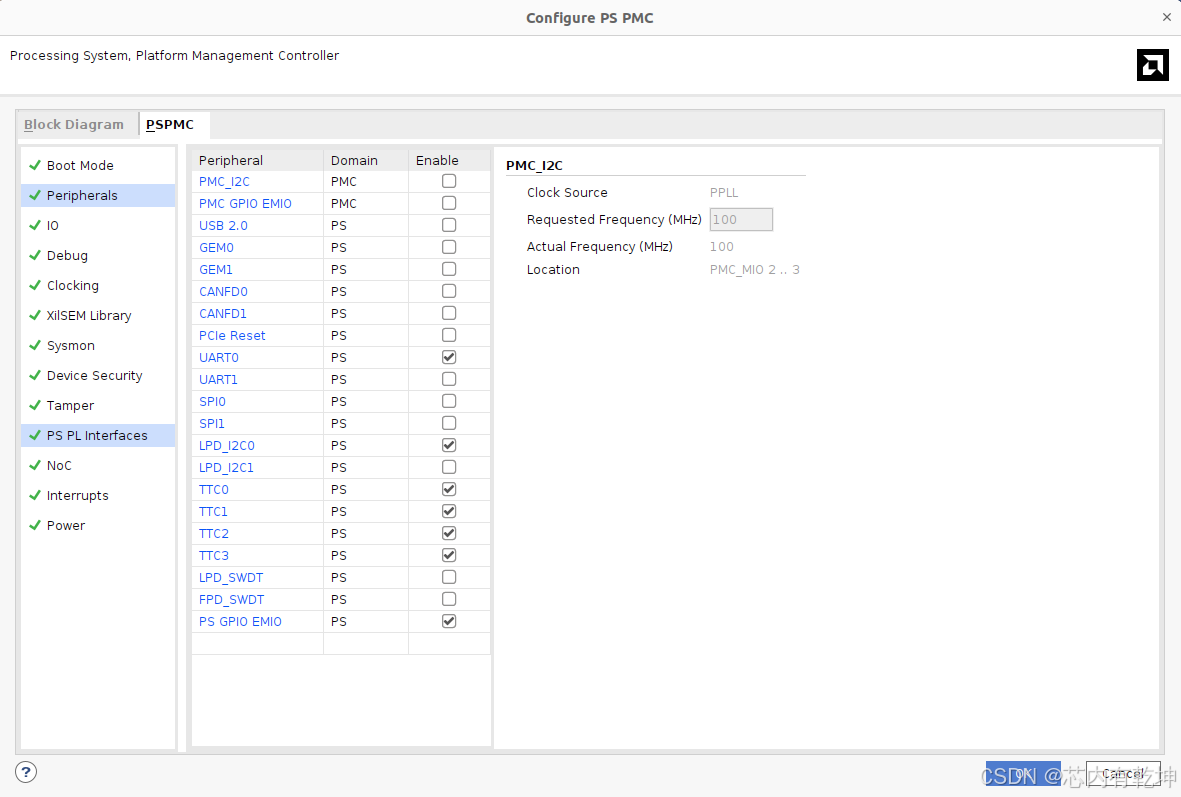

Peripherals:这里主要是配置PS端的外设控制器,根据项目需求选择相应的外设控制器即可,但并不是所有的外设控制器都可以勾选,这个跟MIO引脚数量有关,有些外设是复用的相同的MIO引脚。所以,如果项目中需要使用多个相同的外设而PS的MIO数量不足以支持时,需要考虑其他方法,比如:利用PL端的引脚实现相应的功能。在这个项目中,需要使用PS端的1个IIC控制器(共有2个)作为Master配置摄像头寄存器、一个UART控制器(共有2个)用于PS端调试、一个GPIO引脚用于摄像头模组上电开关;

-

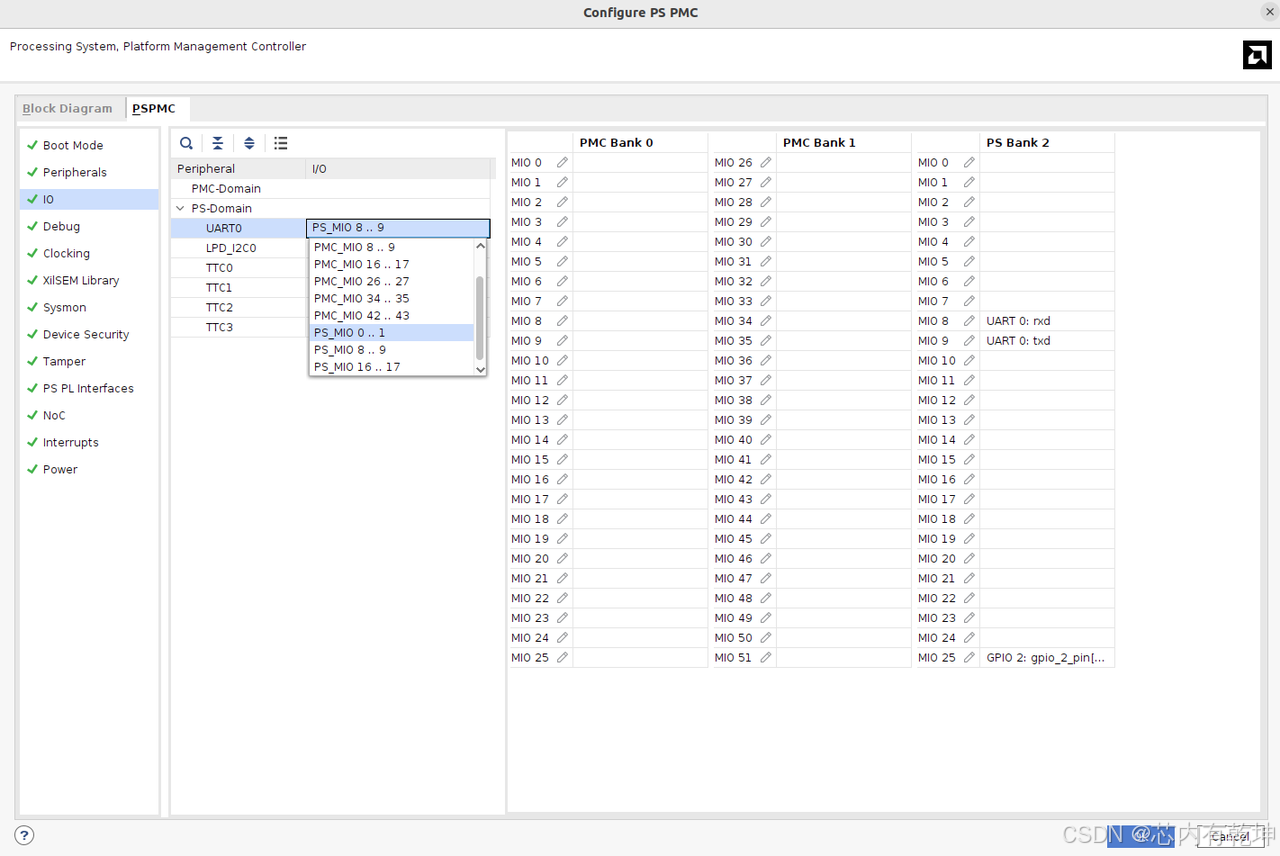

IO:配置对应的外设控制器连接到哪些MIO(PS MIO或PMC MIO)或EMIO;具体如何选择需要根据硬件PCB设计选择,例如:在V100开发板上,PS端的UART控制器引脚连接到PS_MIO16..17,故UART0的IO选择PS_MIO16..17;而摄像头的IIC引脚连接在PL端,故LPD_I2C0的IO选择EMIO,当然,在PL端用逻辑实现摄像头寄存器配置也是可以的。

-

PS PL Interface:配置PL与PS之间的总线连接,PS向PL提供一个reset信号以及AXI-Master Lite总线;reset信号用于复位PL端逻辑;AXI-Master Lite用于配置IP核寄存器;

-

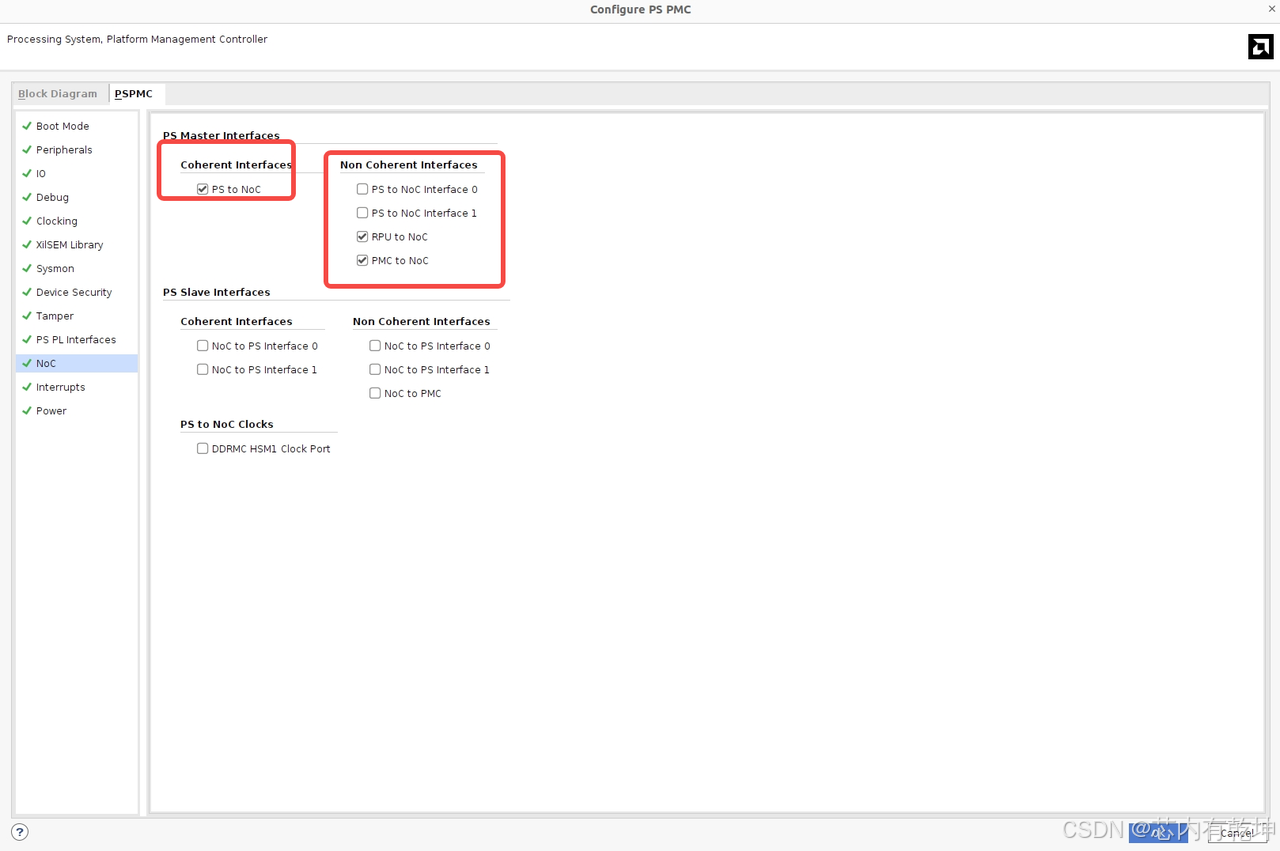

NoC:PS需要通过NoC实现对外部DDR4存储器的访问,所以需要使能PS到NoC之间的接口连接;

-

其它配置在这里保持默认状态即可。

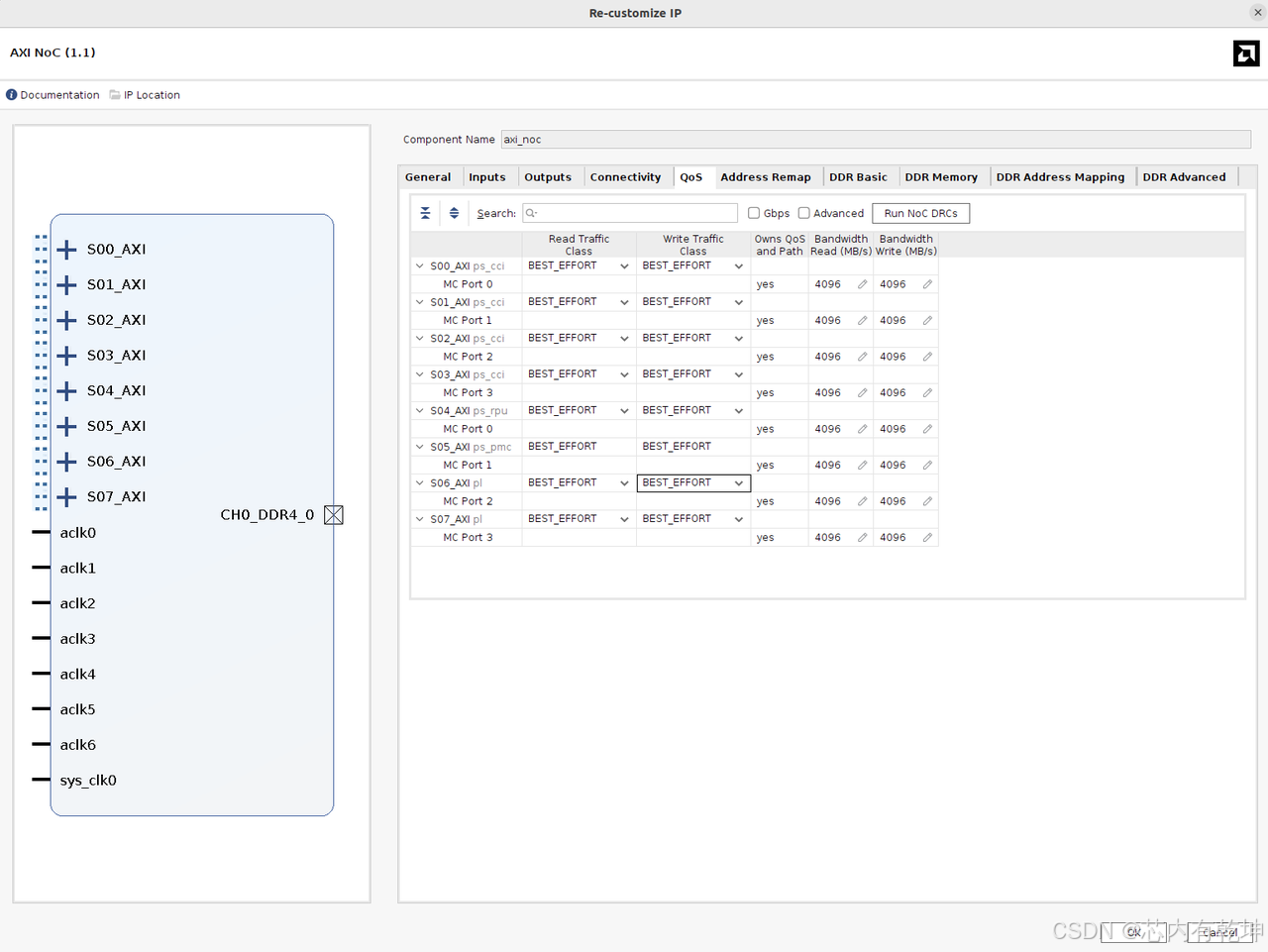

NoC配置

NoC的配置比较重要,因为PS和PL对DDR4存储器的访问都是通过NoC实现的。

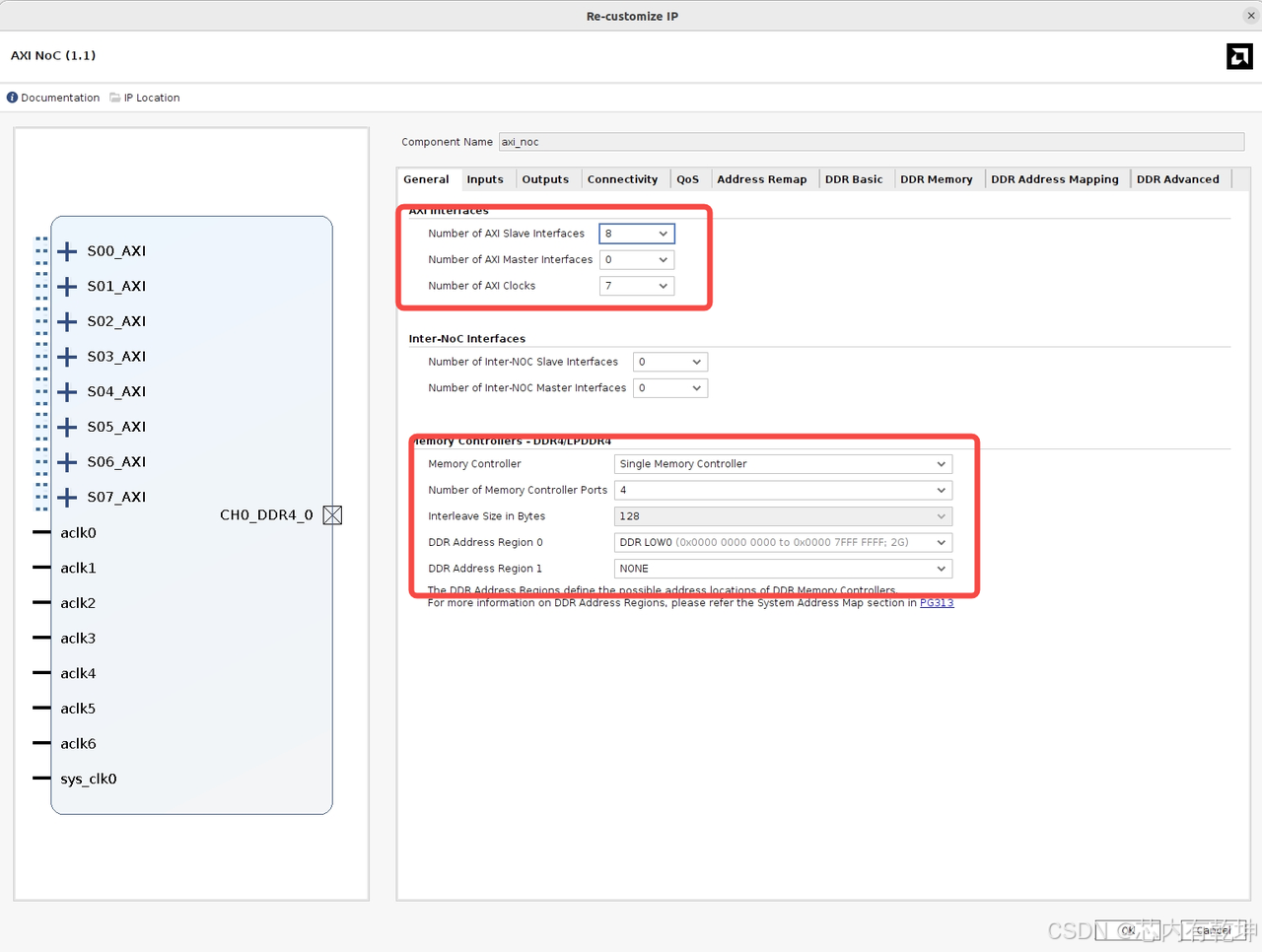

General:AXI Slave一共配置8个,其中4个用于PS Cache Coherent Interface(缓存一致性接口)和DDR存储器控制器的连接,1个用于LPD和DDR4的连接,1个用于PMC和DDR4的连接,2个用于VDMA和DDR4的连接(S2MM、MM2S);时钟配置7个即可,VDMA的两个AXI Slave接口共用一个时钟即可;Memory Controller配置为"Single Memory Controller"、Number of Memory Controller Port配置为4个,可以支持1、2、4个DDR存储器控制器接口,这里配置为4,有利于充分发挥DDR访问效率,实际上小一些应该也是可以的,因为在这个demo中视频带宽不超过250MB/S,这个流量对NoC来说是小意思;

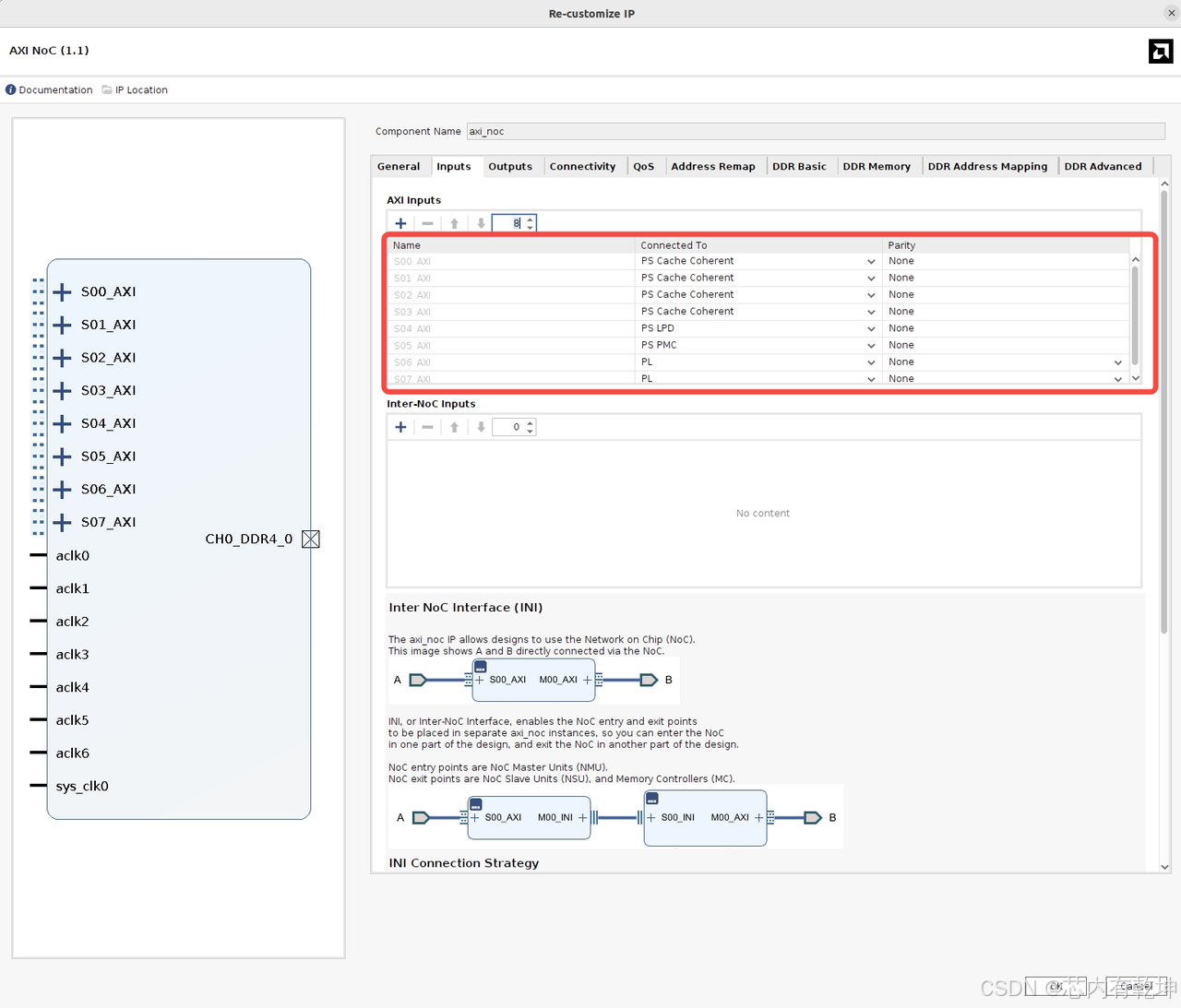

Inputs:配置NoC和外部的连接关系,根据前面提到的那样,在Connected To下选择每一个AXI接口连接到哪里。

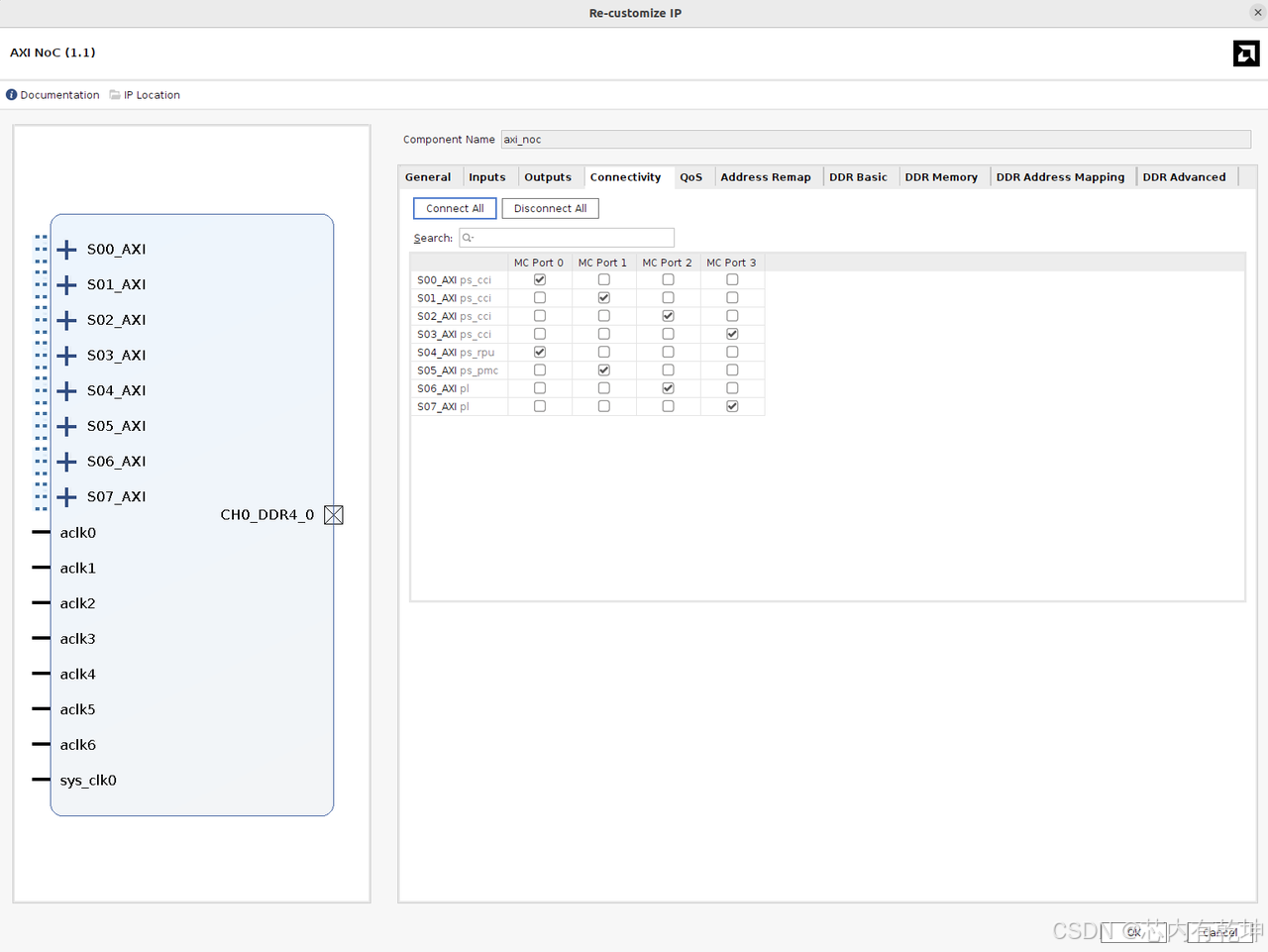

Connectivity:这里主要是分配8个AXI Slave总线和4个DDR4 Controller Port的连接关系,这里就平均分配吧;

QoS:这里是配置DDR4 Controller的服务质量(性能和带宽),可以配置大一点;

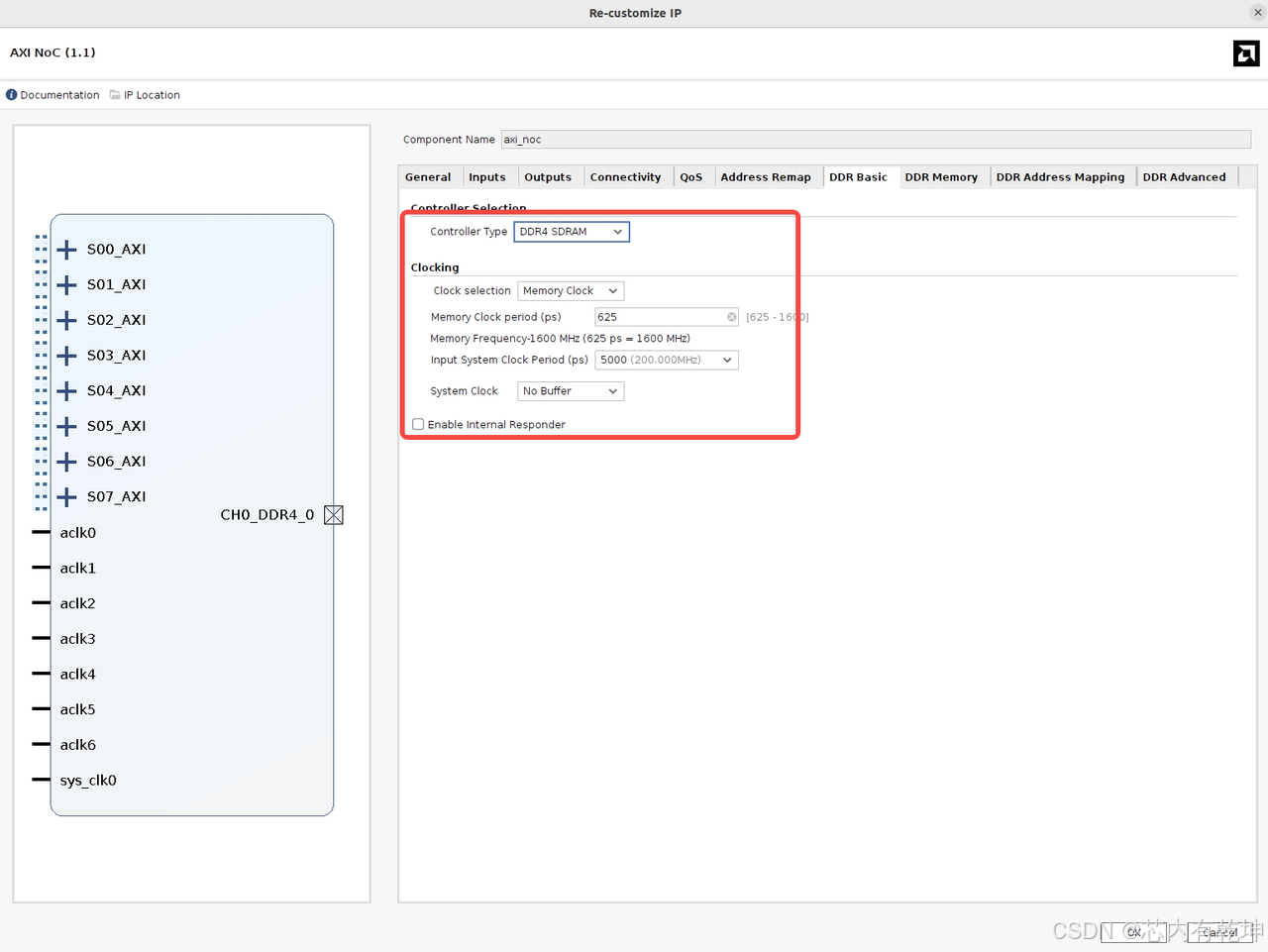

DDR Basic:根据带宽需求设置DDR4存储器时钟频率即可,系统时钟频率可以由外部晶振提供差分时钟(Differential),也可以由内部提供(No Buffer);

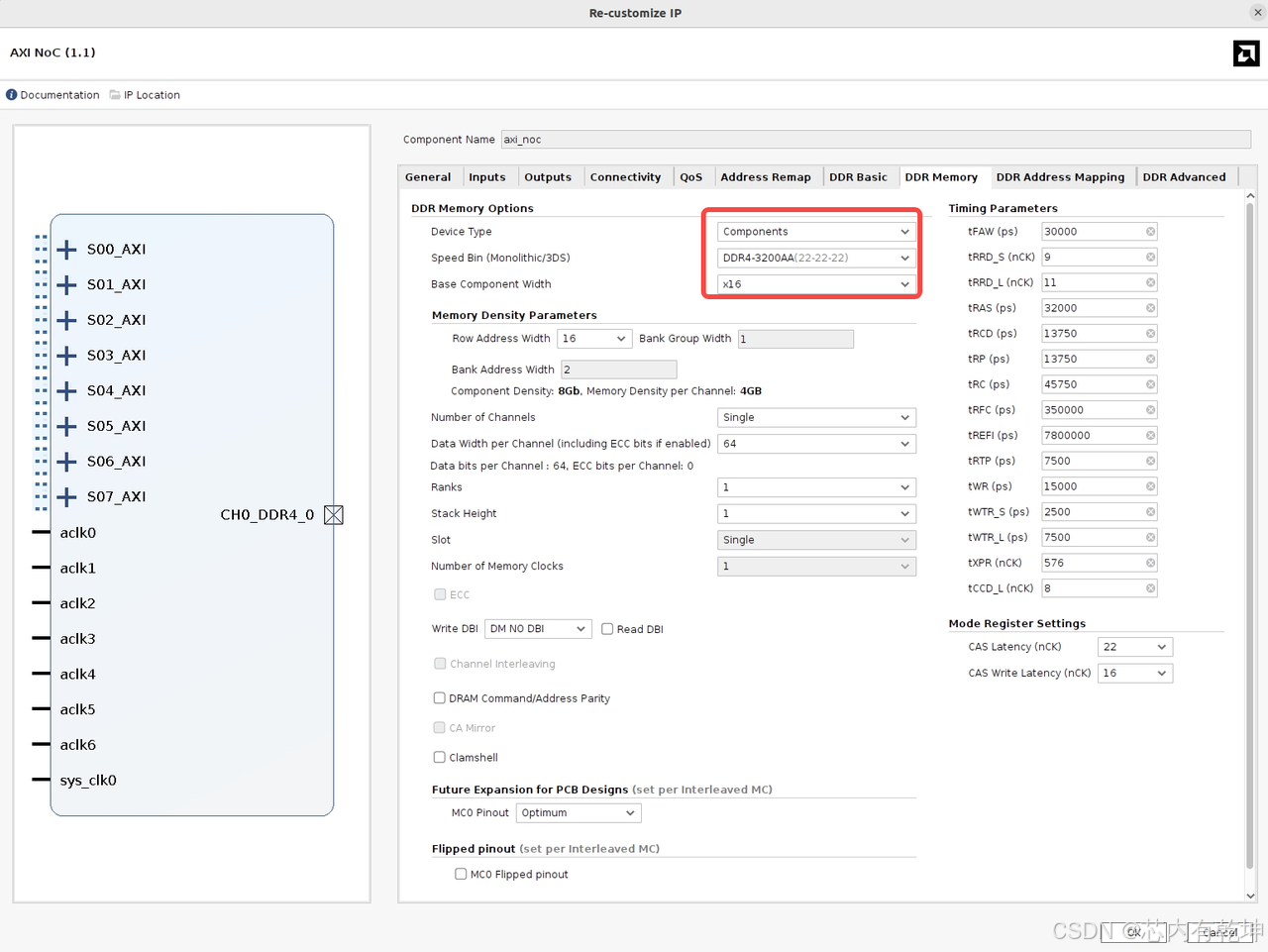

DDR Memory:根据硬件板卡上的DDR4存储器的型号与数据总线位宽配置即可。

其它配置保持默认。

MIPI CSI-2 Rx Subsystem配置

摄像头使用4lane MIPI 接口输出RAW10bit格式的图像数据,因此,按照上面的配置即可,需要注意的是,Lane Rate不能配置小了,需要根据摄像头输出视频的分辨率和帧率(带宽)配置,太小的话带宽跟不上,这里设置为每个lane 1000Mbps的线速率足够了。

demosaic配置

VDMA配置

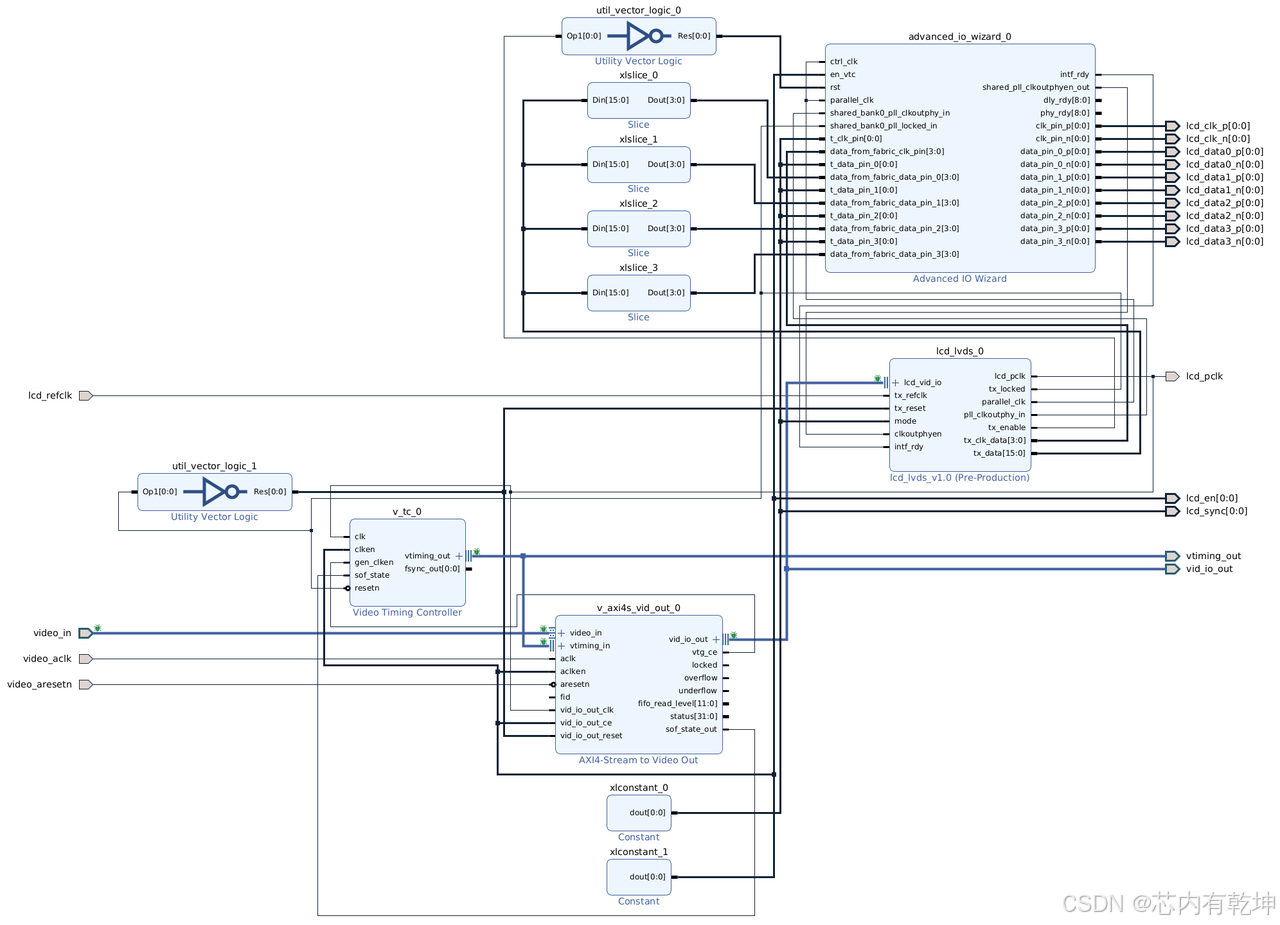

LCD驱动设计

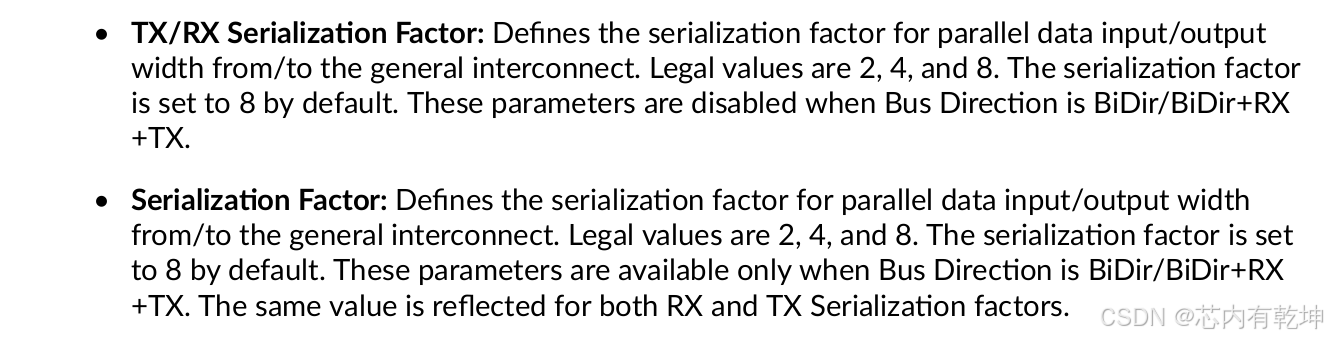

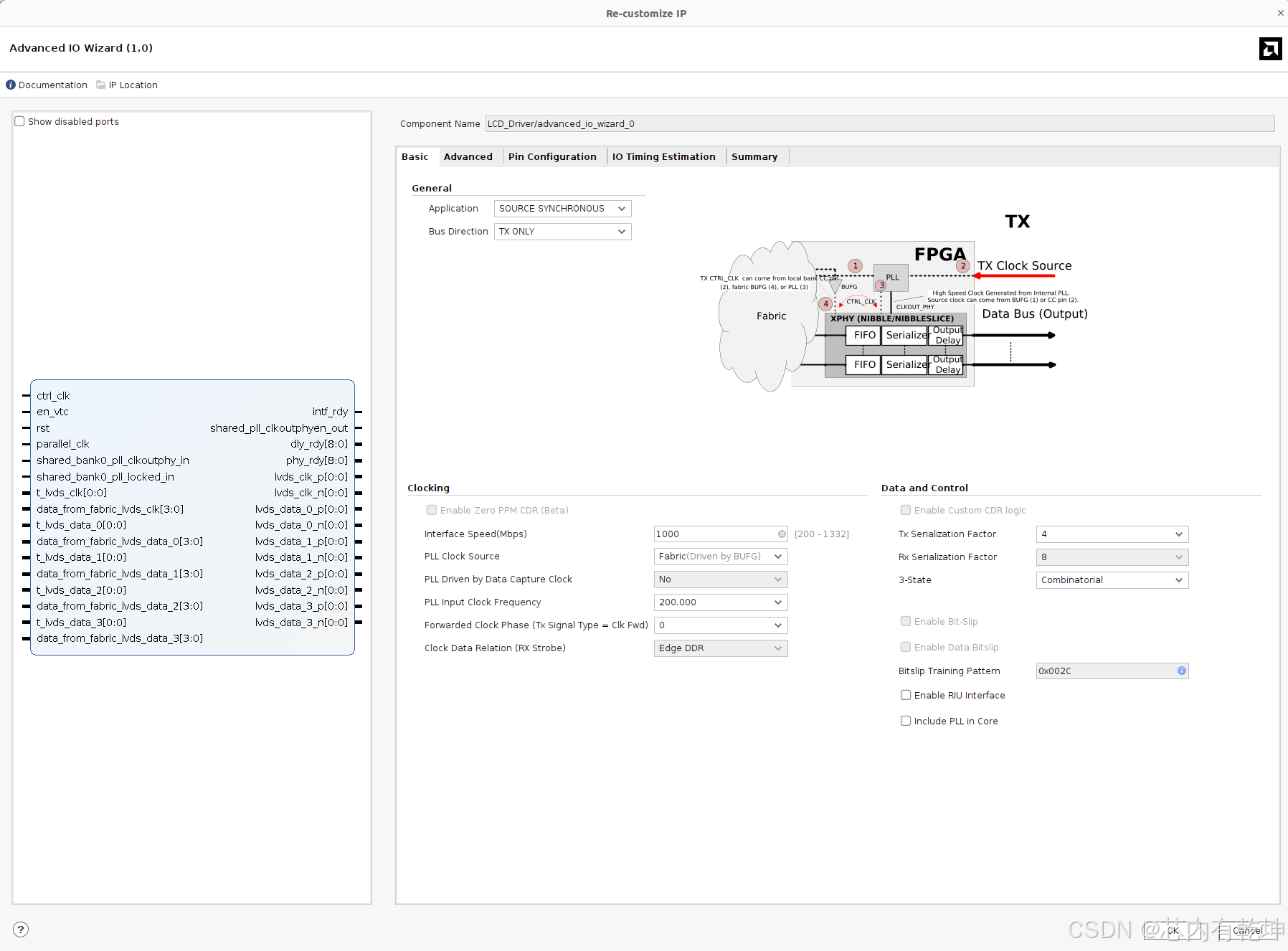

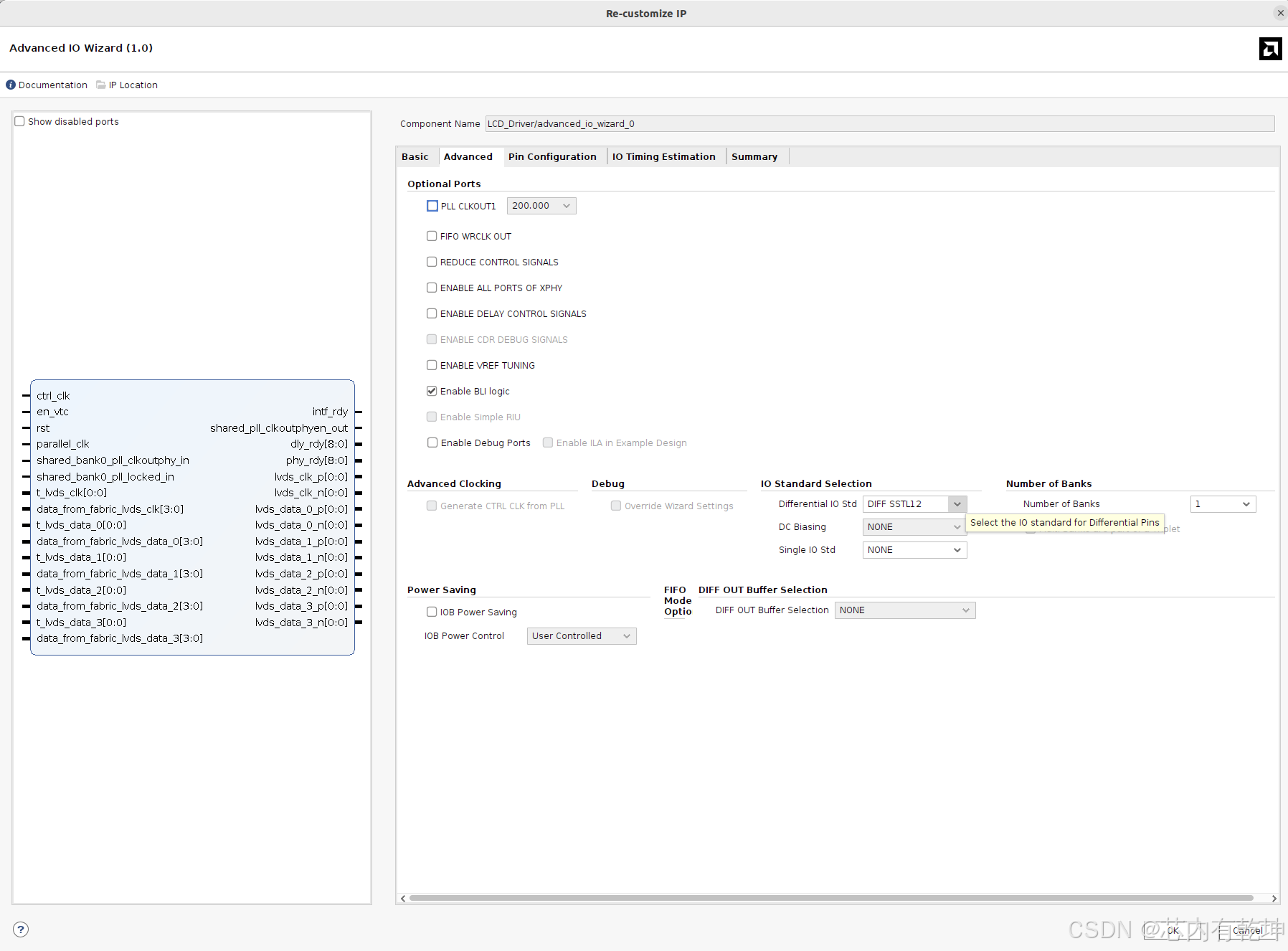

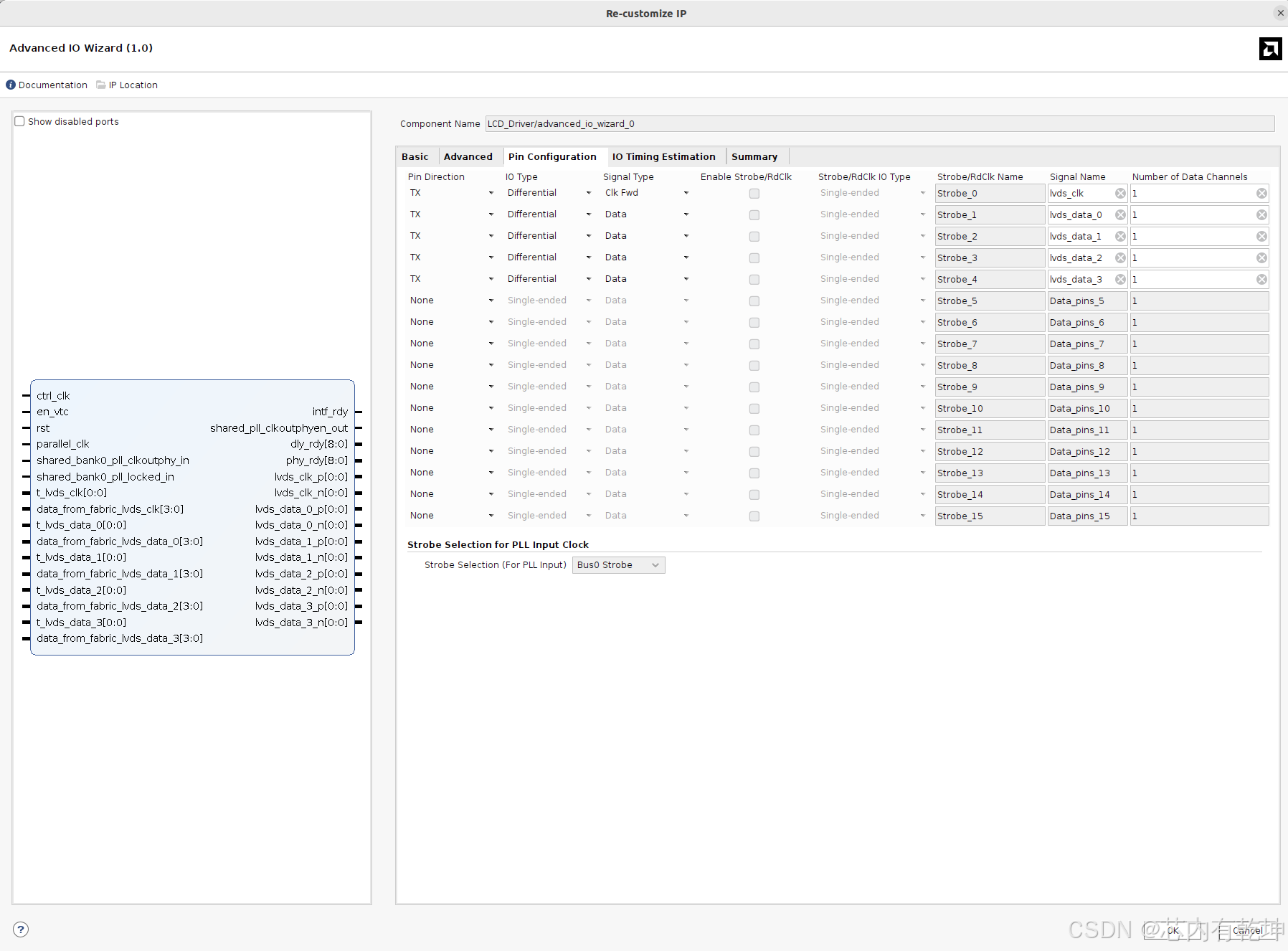

在驱动LCD屏幕时,需要将每个RGB888像素的24bit数据、HSYC、VSYNC、DE以及1bit 0,共28bit信息映射到4个LVDS lane上,在每个源同步差分时钟周期内每个lane串行传输7bit,难点在于如何实现7:1的串化。Versal器件集成了SelectIO资源,而且比之前器件的SelectIO资源性能更优秀,因此称之为Advanced IO;Advanced IO可以支持高速源同步传输,可以使用Advanced IO Wizard IP核实现LVDS发送的功能。但是,不幸的是,Advanced IO Wizard只能实现串化因子为2、4、8的情况,因此,官方提供了一个变速箱,巧妙地利用时钟占空比将7biti数据变为2个4bit数据,再经过Advanced IO Wizara实现4:1串化。

Advanced IO配置

总结

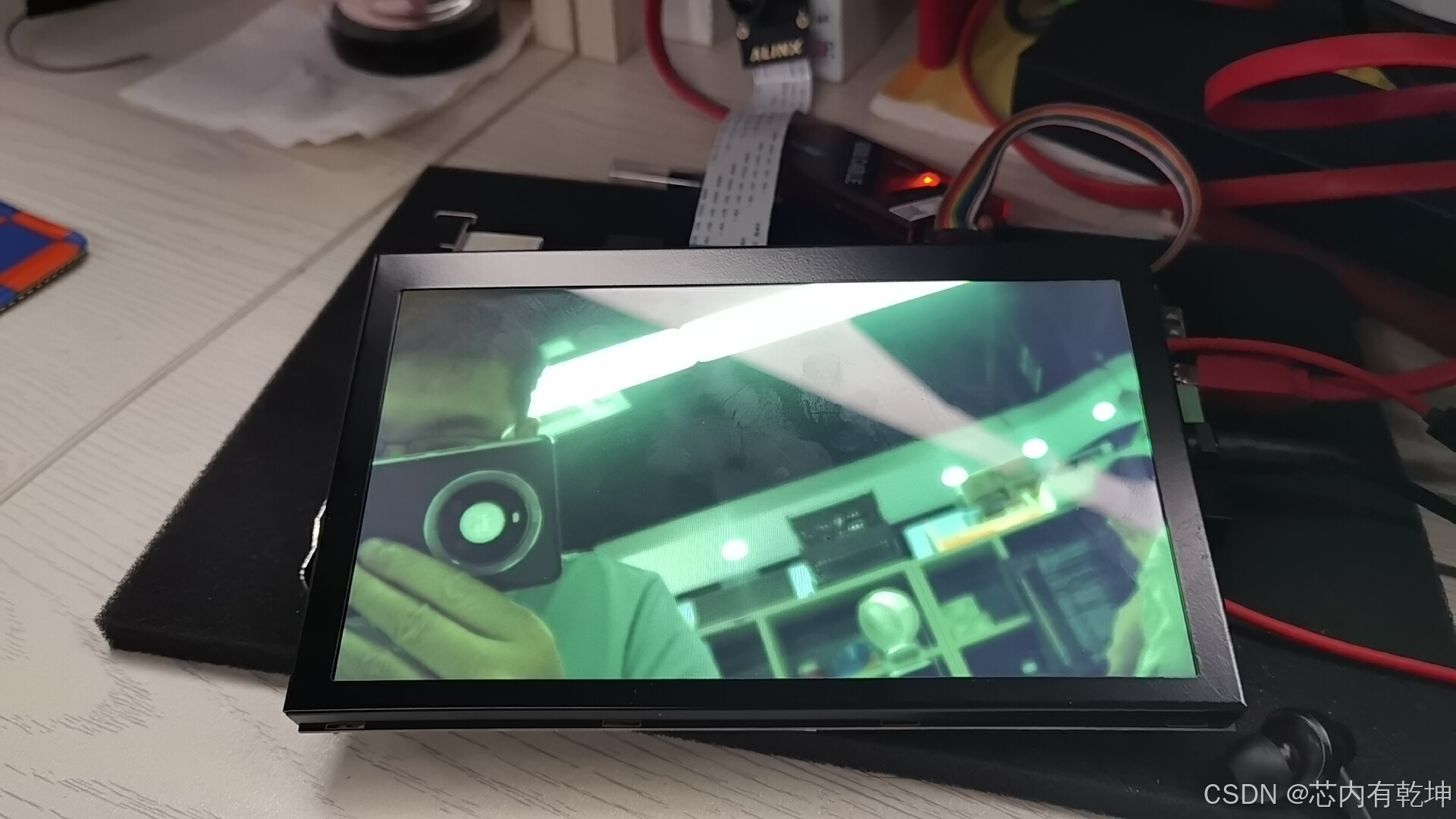

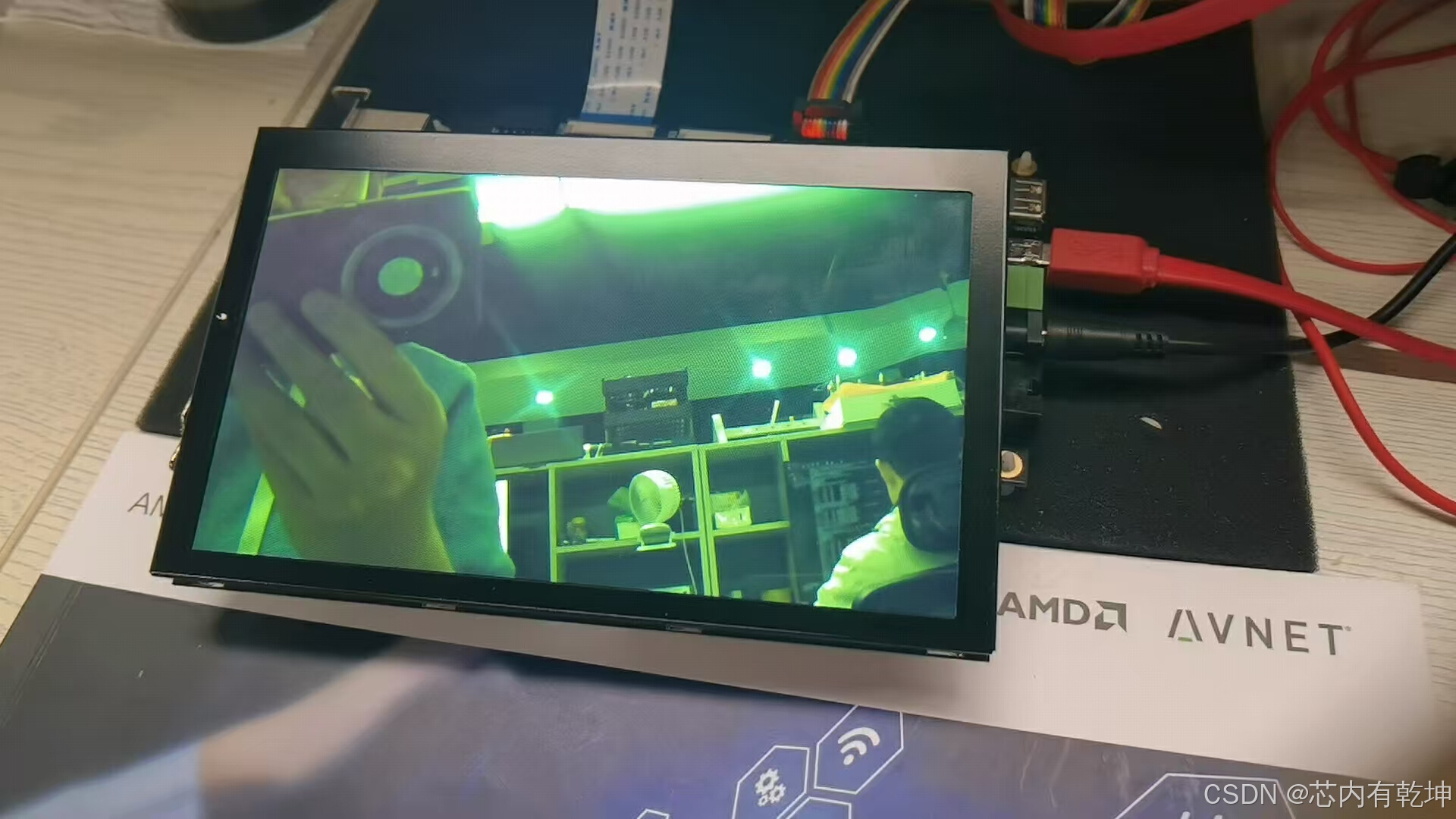

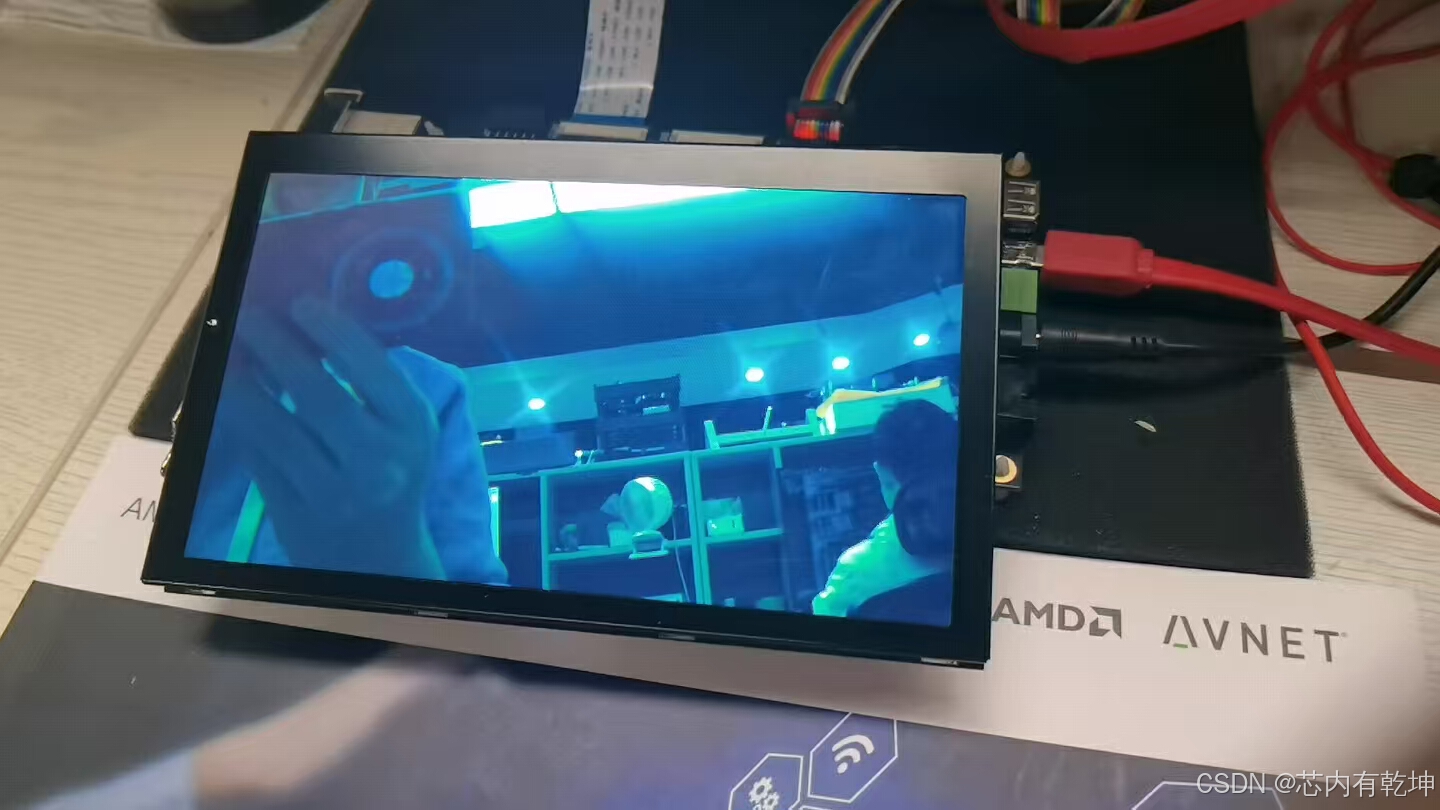

Vitis部分主要是编写PS IIC控制器初始化函数、摄像头寄存器配置函数、VDMA配置函数、demosaic配置函数,比较简单,不再赘述。最终实现出来的效果看上去颜色偏绿,猜测是因为摄像头色彩校准参数配置不合适,不过这不是重点,所以没有深入研究。

展望

最后,在显示通路中集成了去噪算法(双边滤波)和调色算法(3D-LUT)。

后续,还会进一步研究AI引擎的开发和使用,到时候再继续更新吧。敬请期待。

479

479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?