1. DUT——router功能概述

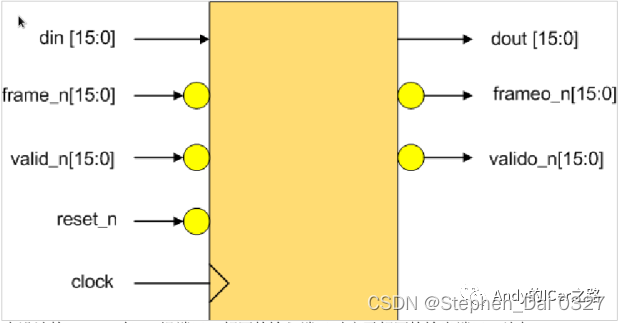

1.1管脚图

以router(路由器)为例

1.2输入输出信号

左边是输入:16位的din(数据输入)、16位的frame_n(数据帧有效,低电平有效)、16位的valid_n(有效信号,低电平有效)、reset_n(低电平复位)和clock(时钟)

右边是输出:16位的dout(数据输出)、16位的dout(数据输出)、16位的frameo_n(数据帧输出有效)、16位的valido_n(输出有效信号,低电平有效)

1.3模块功能

16个输入的通道,选一个通道作为输入通道,同样的,16个输出的通道,也是选一个通道作为输出通道,数据是一bit一bit地传输。

例如,选择din[7]为数据的输入通道,所以frame_n[7]和valid_n[7]就是控制信号;选择dout[3]为数据的输出通道,所以frameo_n[3]和valido_n[3]就是控制信号。因此数据会从7号输入通道输入,然后从3号通道输出,路由器的功能就是这么简单。

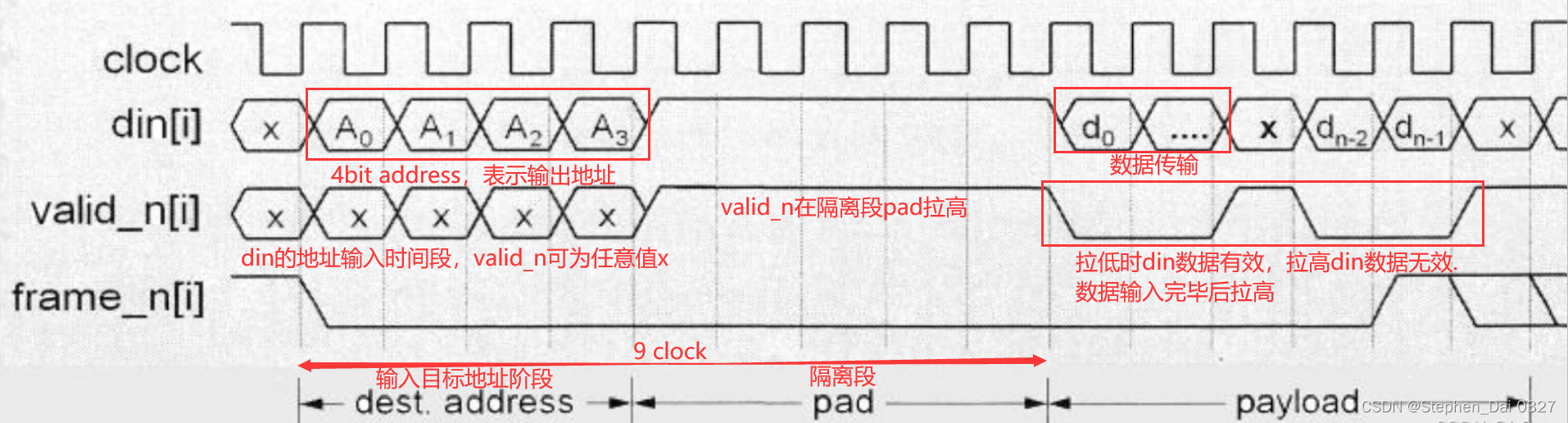

1.4输入信号协议

din信号

1.din[i]中的i表示从哪路输入,din中的第一段4bit的数据表示输出地址(低位开始),从哪路输出

2.地址传输完毕后拉高进入隔离段

3.隔离段结束后开始传输数据(低位开始)

frame_n信号

1.下降沿指示packet的第一位数据

2.上升沿指示packet的最后一位数据

valid_n信号

1.其在din的地址输入时间段可为任意值x

2.在隔离段pad拉高

3.其拉低时表示数据有效,因此在payload段若其拉高,则din数据无效

4.数据输入完毕后拉高

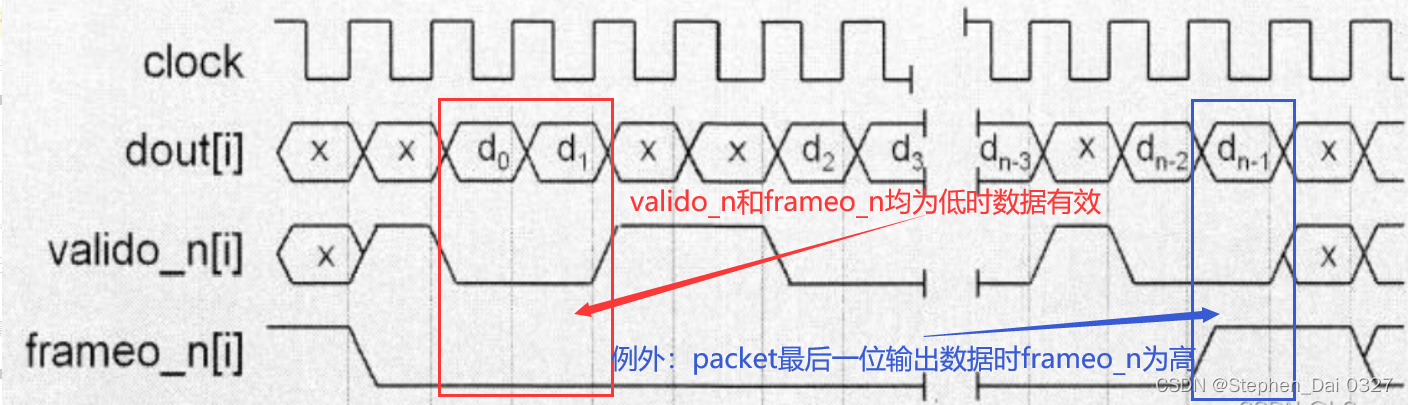

1.5输出信号协议

输出信号时序图如上,比较简单,当valido_n和frameo_n均为低时数据有效,除了packet最后一位输出数据时frameo_n为高 。

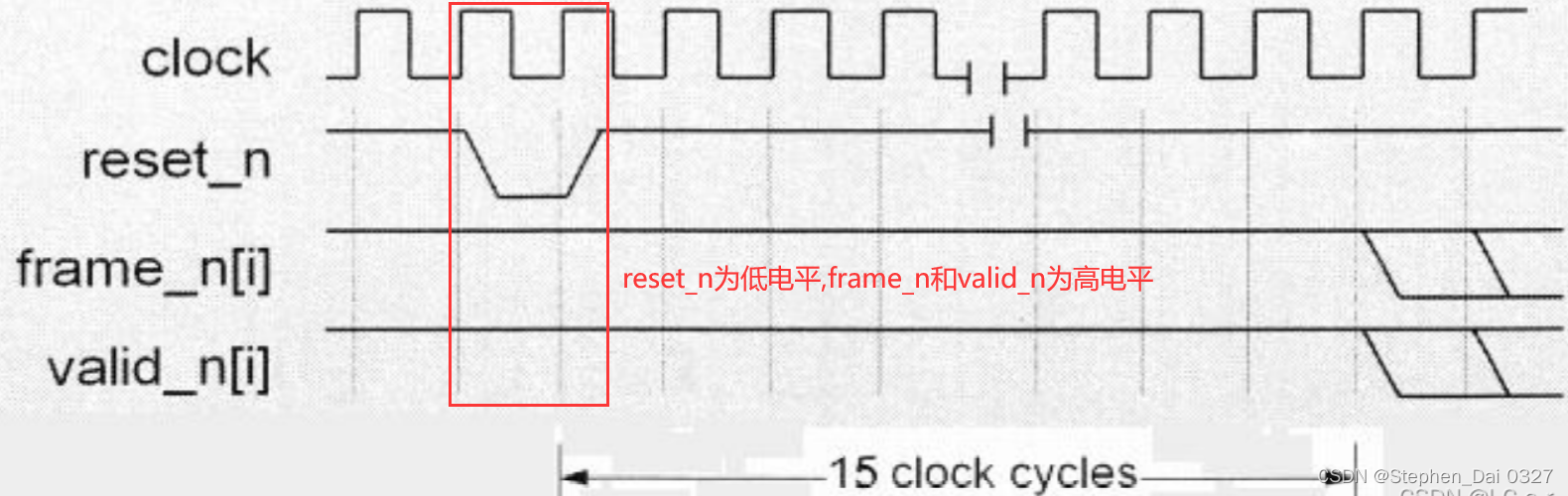

1.6复位信号协议

以上为其复位协议时序图,有以下几点需要注意:

1.复位时,reset_n为低电平,frame_n和valid_n为高电平

2.有效复位至少保持1个clk

3.复位后至少等待15个时钟周期后才可以发送数据

2. 实验代码

2.1 router代码

DUT:router代码如下:

// control pins:

// input: reset_n - active low reset

// input: clock - master clock input

// input port pins:

// input: frame_n - must be active during whole input packet

// input: valid_n - valid data input

// input: di - the data input

// output: busy_n - tells input that connection is busy

// output port pins:

// output: do - the data output

// output: valido_n - tells output device that "do" contain valid data

// output: frameo_n - active during the whole output packet

// frame format:

//

// Frame start must look like this:

//

// frame_n: | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ...

// di: | X | A0 | A1 | A2 | A3 | 1 | X | X | X | D0 | ...

// valid_n: | X | X | X | X | X | X | 1 | 1 | 1 | 0/1 | ...

//

// note1: frame_n must deasserted at least one cycle between packets.

// note2: address data does not have to wait for busy_n = 1.

// note3: di must wait for busy_n = 1.

// note4: a di is taken by the chip if: busy_n == 1 && valid_n == 0

// note5: frame_n must be deasserted with the last data bit in the frame.

// note6: once connection is successfully made, busy_n is guaranteed to

// stay inactive until to the end of the current frame.

module router

(

reset_n,

clock,

frame_n,

valid_n,

din,

dout,

busy_n,

valido_n,

frameo_n

);

input reset_n, clock;

input [15:0] din, frame_n, valid_n;

output [15:0] dout, valido_n, busy_n, frameo_n;

wire reset;

wire [15:0] arb0, arb1, arb2, arb3, arb4, arb5, arb6, arb7;

wire [15:0] di;

wire [15:0] arb8, arb9, arb10, arb11, arb12, arb13, arb14, arb15;

wire [15:0] arb_head, okstep;

tri0 [15:0] doint;

tri1 [15:0] valdoint_n, frameoint_n;

reg [15:0] dout, valido_n, frameo_n;

reg [3:0] arb_head_num;

assign di = din;

assign reset = ~reset_n;

assign arb_head = 1 << arb_head_num;

rtslice rts0(reset,clock,frame_n[0],valid_n[0],di[0],

arb0,arb1,arb_head[0],okstep[0],

doint,busy_n[0],valdoint_n,frameoint_n);

rtslice rts1(reset,clock,frame_n[1],valid_n[1],di[1],

arb1,arb2,arb_head[1],okstep[1],

doint,busy_n[1],valdoint_n,frameoint_n);

rtslice rts2(reset,clock,frame_n[2],valid_n[2],di[2],

arb2,arb3,arb_head[2],okstep[2],

doint,busy_n[2],valdoint_n,frameoint_n);

rtslice rts3(reset,clock,frame_n[3],valid_n[3],di[3],

arb3,arb4,arb_head[3],okstep[3],

doint,busy_n[3],valdoint_n,frameoint_n);

rtslice rts4(reset,clock,frame_n[4],valid_n[4],di[4],

arb4,arb5,arb_head[4],okstep[4],

doint,busy_n[4],valdoint_n,frameoint_n);

rtslice rts5(reset,clock,frame_n[5],valid_n[5],di[5],

arb5,arb6,arb_head[5],okstep[5],

doint,busy_n[5],valdoint_n,frameoint_n);

rtslice rts6(reset,clock,frame_n[6],valid_n[6],di[6],

arb6,arb7,arb_head[6],okstep[6],

doint,busy_n[6],valdoint_n,frameoint_n);

rtslice rts7(reset,clock,frame_n[7],valid_n[7],di[7],

arb7,arb8,arb_head[7],okstep[7],

doint,busy_n[7],valdoint_n,frameoint_n);

rtslice rts8(reset,clock,frame_n[8],valid_n[8],di[8],

arb8,a

本文详细介绍了路由器的模块功能,包括输入输出信号、复位协议以及输入输出信号协议。代码部分展示了路由器模块(DUT)和子模块(rtslice)的Verilog实现,用于处理16个输入通道和16个输出通道的数据传输。在实验代码中,路由器通过din接收16位数据,根据frame_n和valid_n信号进行操作,并通过dout输出数据。复位信号协议确保了正确初始化和数据传输。

本文详细介绍了路由器的模块功能,包括输入输出信号、复位协议以及输入输出信号协议。代码部分展示了路由器模块(DUT)和子模块(rtslice)的Verilog实现,用于处理16个输入通道和16个输出通道的数据传输。在实验代码中,路由器通过din接收16位数据,根据frame_n和valid_n信号进行操作,并通过dout输出数据。复位信号协议确保了正确初始化和数据传输。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

912

912

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?