如果我写的文章对你能有些许帮助,说明我做的事还算有点意义,欢迎留个赞哦~

有问题恳请指出,也欢迎探讨qq815506713

1. 起因

我写下这篇专栏一方面是因近来学了riscv处理器,希望能写点笔记留存一下;另一方面也是应好友邓之邀,出一个不那么复杂便于初学者学习的小白教程。从开始学习RISCV处理器的时候我花了不少时间去找参考资料,但要么结构过于复杂不便于初学者理解,要么就是没有对照的结构图。所以,打算写一个更偏向于从零开始的小白教程,从指令集开始,再一步一步搭建RISCV处理器核,最后根据搭建的架构图再去写代码。

2. 建议

- 本项目RISCV处理器的设计参考《计算机组成与设计:硬件软件接口 RISC-V版》一书,如果时间充足的话非常建议先阅读该书前四章再来学习;

- 代码可在

gitee下载(没开源了,可有偿提供),在看代码之前,推荐先看本教程专栏,搭配食用效果更佳。 - 代码的使用方法详见工程文件中的README

3. 关于项目

- 本项目用verilog语言实现了一个具有五级流水线的简单RISCV处理器核,实现RV32I指令集并验证了指令实现的正确性。项目文件里面包含所有的设计和测试文件以及完整的makefile脚本,可以“开箱即用”。

- 本项目RISCV处理器的设计参考《计算机组成与设计:硬件软件接口 RISC-V版》一书,如果时间充足的话非常建议先阅读该书前四章再来学习;测试部分使用官方的指令集txt文件测试。目前实现的架构相对简单,现在分享出来一是为了当个阶段笔记记录,一是为了给同样想了解RISCV处理器的初学者一个参考。由于笔者也是新手一枚,水平实在有限,如有错误,望指正!咨询相关问题,欢迎联系!

3.1 优点

- 实现的RISCV处理器核比较基础,对初学小白相对友好;

- 项目文件里面包含所有的设计、测试、脚本文件以及完整的Makefile脚本,可以“开箱即用”;

- 教程专栏里面有RISCV处理器核的搭建过程以及最终的架构图,可以给代码提供参考;

- 代码具有详细的注释;

3.2 缺点

- 实现的RISCV处理器核比较基础,例如中断、

cache缓存(已填坑)等暂未实现; - 目前只测试了各指令的执行,测试方法待完善;

#todo 部分store指令有点问题

3.3 RISCV处理器核规格

本项目实现的RISCV处理器核特点如下:

- 具有五级流水线;

- 实现RV32I指令集(除fence、ecall、ebreak);

- 能够处理流水线冒险与前递;

- 使用官方指令集测试文件进行测试;

- 包含Makefile脚本,开箱即用

- L1 Data Cache规格如下:

- Size : 1KB

- Associative :2-way

- Replacement policy : LRU

- Cache line size : 32 Bytes

- Write hit policy : write back

- Write miss policy : write allocate

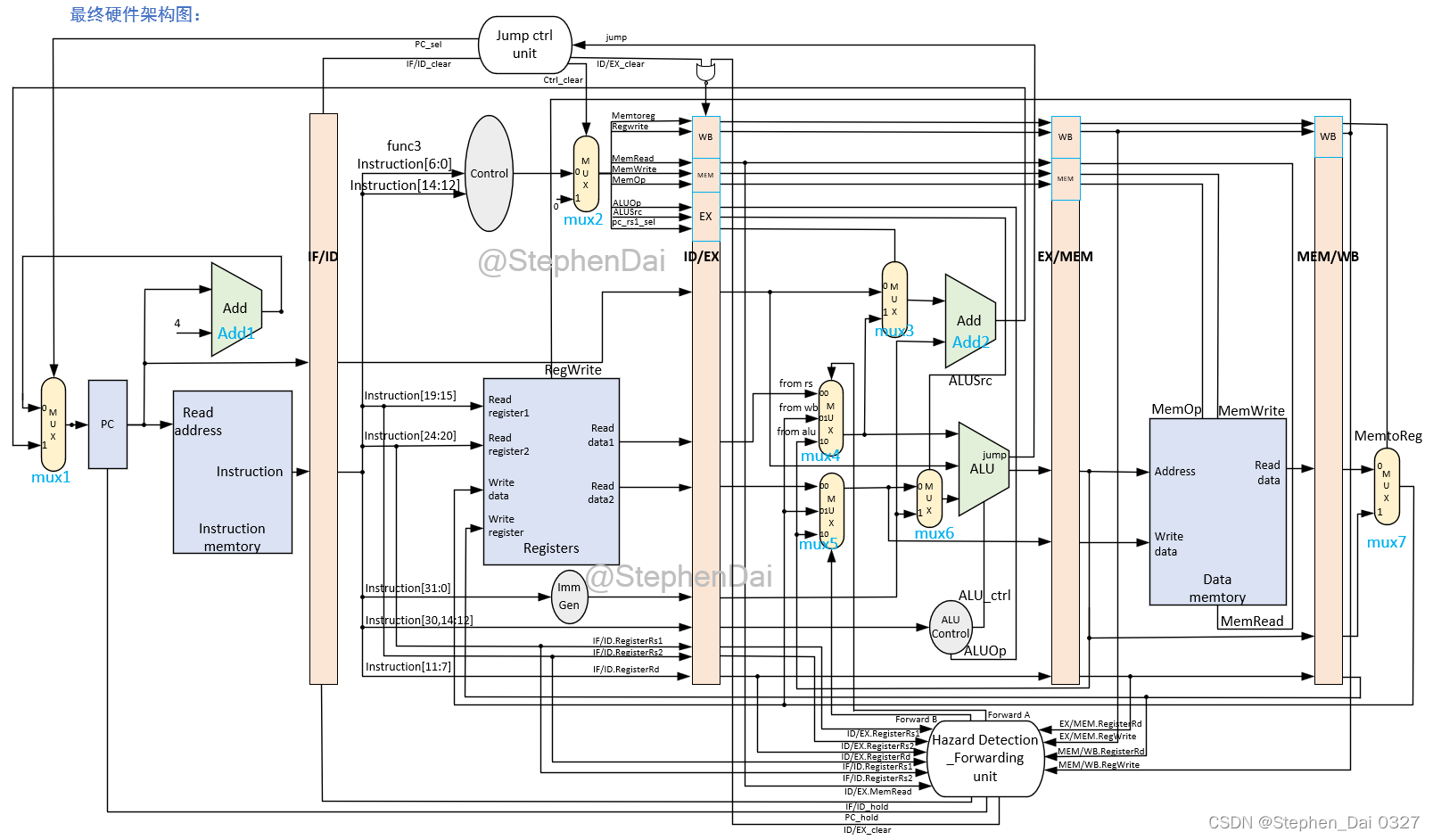

3.4 硬件架构图

3.5 项目文件层次

RISCV_V1_20230831

├── doc

│ └── riscv-spec-20191213.pdf

├── Makefile

├── pic

│ ├── Hardware_Architecture.png

│ ├── RISCV_assembly_instructions.jpg

│ └── RV32I_Base_Instruction_Set.jpg

├── README.txt

├── rtl

│ ├── chip

│ │ └── riscv_soc.v

│ ├── riscv_core

│ │ ├── alu_add.v

│ │ ├── alu_ctrl.v

│ │ ├── alu_ex.v

│ │ ├── defines.v

│ │ ├── dff.v

│ │ ├── ex_mem.v

│ │ ├── Hazard_Detection_Forwarding_unit.v

│ │ ├── id_ex.v

│ │ ├── if_id.v

│ │ ├── imm_gen.v

│ │ ├── jump_ctrl_unit.v

│ │ ├── main_ctrl.v

│ │ ├── mem_wb.v

│ │ ├── mux2.v

│ │ ├── mux3.v

│ │ ├── or_gate.v

│ │ ├── pc.v

│ │ ├── regs.v

│ │ └── riscv_core.v

│ └── wrap

│ ├── dram.v

│ ├── dual_ram.v

│ └── iram.v

├── script

│ ├── count.pl

│ └── report.pl

├── sim

│ ├── filelist.f

│ ├── insts.txt

│ └── wave_rcfiles

└── tb

├── generated

│ ├── ...

├── my_inst_txt

│ ├── blt_inst_test.txt

│ ├── bne_inst_test.txt

│ ├── ex_mem_risk.txt

│ ├── ex_risk.txt

│ ├── jal_inst_test.txt

│ ├── load_use_risk.txt

│ └── mem_risk.txt

├── inst_txt

│ ├── ...

└── riscv_soc_tb.v

13 directories, 323 files

4. 后续计划

增加中断

增加cache缓存 (已填坑)

完善处理器的测试,跑个回归测试…

使用编译器运行c语言代码

5. 文章链接

从零开始写riscv处理器(一)指令集

从零开始写riscv处理器(二)简单数据通路

从零开始写riscv处理器(三)全部指令数据通路

从零开始写riscv处理器(四)流水线结构

从零开始写riscv处理器(五)数据冒险:停顿与前递

从零开始写riscv处理器(六)控制冒险:流水线冲刷

从零开始写riscv处理器(七)cache基础

从零开始写riscv处理器(八)cache进阶

未完待续…

参考资源:

《计算机组成与设计:硬件软件接口 RISC-V版》

3000

3000

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?