引言

一、电源纹波的测量方法

1.带宽限制:开启 20MHz 带宽限制

2. 耦合方式:选择交流 AC 耦合

3. ms/格、mv/格设置

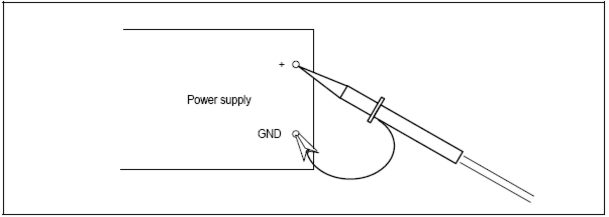

4. 探头设置:取消探头地线夹(使用接地弹簧) 、选择×1档

二、纹波要求

1.Vo≤3.3V时

Vp-p<60mV。

2.Vo>3.3V且≤5V时

Vp-p<100mV(无动态负载),Vp-p<250mV(有动态负载,如功放,电机等)。

3.Vo>5V且≤12V时

Vp-p<600mV(无动态负载),Vp-p<1200mV(有动态负载,如功放,电机等)。

4.Vo>12V时

Vp-p<600mV(无动态负载),Vp-p<1500mV(有动态负载,如功放,电机等)。

三、纹波抑制

1.增大输出电容

增大输出电容容量也就是增大了电源系统所存储的能量,当负载在加载过程中需要大电流提供时,电源平面上较大的电容即可为负载提供瞬时所需的能量,使得电压波动不大。但是电容的选择也是很重要的,对于小电流电源平面(负载电流3A这种)可能增加些许陶瓷电容即可达到较好的需求,但是对于大电流电源平面(负载电流上百A这种),所增加的电容容量就会变得很大,此时ESR就变成了考虑对象。通常负载是低压大电流的,一般选择大容量低ESR的高分子铝电解电容,而不选择铝液体电解电容。

2.提高芯片的开关频率

提高高频纹波频率,有利于抑制输出高频纹波,但是过大的开关频率容易造成EMI辐射超标,因此开关频率最好还是选择一个合适的值。

3.增大输出电感

根据开关电源的公式,电感内电流波动大小和电感值成反比,输出纹波和输出电容值成反比。所以加大电感值可以减小输出电源的纹波。

4.优化反馈环路设计

增加前馈电容、选择带有COT控制模式的芯片。

5.优化PCB布局布线

DCDC输出纹波大小是电源平面系统性的问题,在绝大多数情况下通过以上1-4措施理论上可以减小输出的纹波,但是也要注意PCB的布局与布线,比如:功率环路尽量小;功率电感与芯片放置同一层;芯片地、输入地、输出地三者要靠近;去耦滤波电容靠近芯片;反馈走线尽量短且远离其他干扰信号线等。

6.使用LDO供电

在DC-DC后串联一个LDO,衰减开关模式电源产生的电压纹波(利用LDO的高PSRR来降低输出电压纹波)。

影响PSRR变量:

| 参数 | PSRR | ||

| 低频 (<1kHz) | 中频 (1kHz – 100kHz) | 高频 (>100kHz) | |

| VIN – VOUT | +++ | +++ | ++ |

| 输出电容器(COUT) | 没有效果 | + | +++ |

| 降噪电容器(CNR) | +++ | + | 没有效果 |

| 前馈电容(CFF) | ++ | +++ | + |

| PCB布局 | + | + | +++ |

3515

3515

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?