相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

哪些库是需要的?

在线负载模式(wire load mode)下,Design Compiler使用逻辑库(包括目标库和链接库)、符号库和综合库(又称DesignWare库)。

在拓扑模式(topographical mode)下,Design Compiler除上述库外,还使用物理库。

逻辑库

逻辑库由半导体供应商维护和分发,包含每个单元的特性和功能信息,例如单元名称、引脚名称、面积、时序弧和引脚负载。它们还定义了设计规则约束(如线网的最大转换时间)等条件。此外,逻辑库还指定特定工艺技术的工作条件和线负载模型(只用于线负载模式)。

Design Compiler支持使用非线性延迟模型(NLDM)和复合电流源模型(CCS),或同时使用两者。Design Compiler会根据逻辑库的内容自动选择使用的时序模型。如果库同时包含NLDM和CCS模型,Design Compiler会使用CCS模型。在逻辑综合和预布线优化期间,工具可能不会使用所有的CCS数据以节省运行时间。

Design Compiler需要逻辑库是.db格式。通常情况下,半导体供应商会提供.db格式的逻辑库。如果只有逻辑库的源代码(例如.lib格式),则需要首先使用Library Compiler(以前集成在Design Compiler中,后脱离变成单独的工具)将其编译为.db格式。

Design Compiler使用逻辑库的主要目的包括:

- 实现设计功能:Design Compiler在优化过程中映射到的逻辑库称为目标库,这些库包含用于生成网表的标准单元,目标库是用于综合设计的链接库的子集。

- 解析单元引用:Design Compiler使用链接库解析单元引用,链接库可以包含标准单元和设计文件。

- 计算时序值和路径延迟:链接库定义用于计算时序值和路径延迟的延迟模型。

- 计算功耗:提供了有关功耗计算的信息。

Design Compiler使用在link_library变量中找到的第一个逻辑库作为主库,用于在缺少显式规范时获取默认值和设置。这些设置包括工作条件、线负载模型选择组、线负载模式和线网延迟计算。如果其他库的度量单位与主库的单位不同,Design Compiler会将所有单位转换为主库中指定的单位。Design Compiler从主库中获取以下默认值和设置:

- 单位定义

- 工作条件

- K因子

- 线负载模型选择

- 输入和输出电压

- 时序范围

- RC转换点

- 线网转换时间衰减表

目标库

Design Compiler在映射过程中从目标库中选择功能正确的门电路来构建电路。它还使用供应商提供的这些门电路的时序数据来计算电路的时序。

要指定目标库,可以使用target_library变量。你应当只指定Design Compiler用于映射设计中标准单元(如组合逻辑和寄存器)的标准单元库。不应指定任何DesignWare库或宏库,例如pads或memory。

链接库

为了完成设计,设计中的所有单元必须与库中的标准单元和被引用的设计进行链接。这个过程称为链接设计或解析引用。为了解决引用问题,Design Compiler使用以下变量和属性设置的链接库:

-

link_library变量:列出Design Compiler用于解析引用的库文件和设计文件(.ddc格式或.db格式(不推荐))。Design Compiler将从左到右搜索link_library变量中所列文件的内容,并在找到引用时停止搜索。如果在link_library变量中指定了星号(*),则表示Design Compiler会在内存中搜索引用。例如,如果将link_library变量设置为{"*" typical.db},Design Compiler会首先在内存中搜索引用,然后在typical库中搜索。

-

local_link_library属性:可以使用set_local_link_library命令给当前设计指定local_link_library属性,在解析当前设计的引用时,Design Compiler会首先搜索local_link_library属性中的库文件和设计文件。

可以将这两者统称为link_path,当Design Compiler在link_path指定的文件搜索后,但还是没有成功解析引用时,会在search_path变量指定的目录路径下,查找名字是引用名.ddc或引用名.db的文件,并查找其内容中是否有需要的引用。

search_path变量简介

指定工具在查找库文件和设计文件时使用的目录路径列表。

符号库

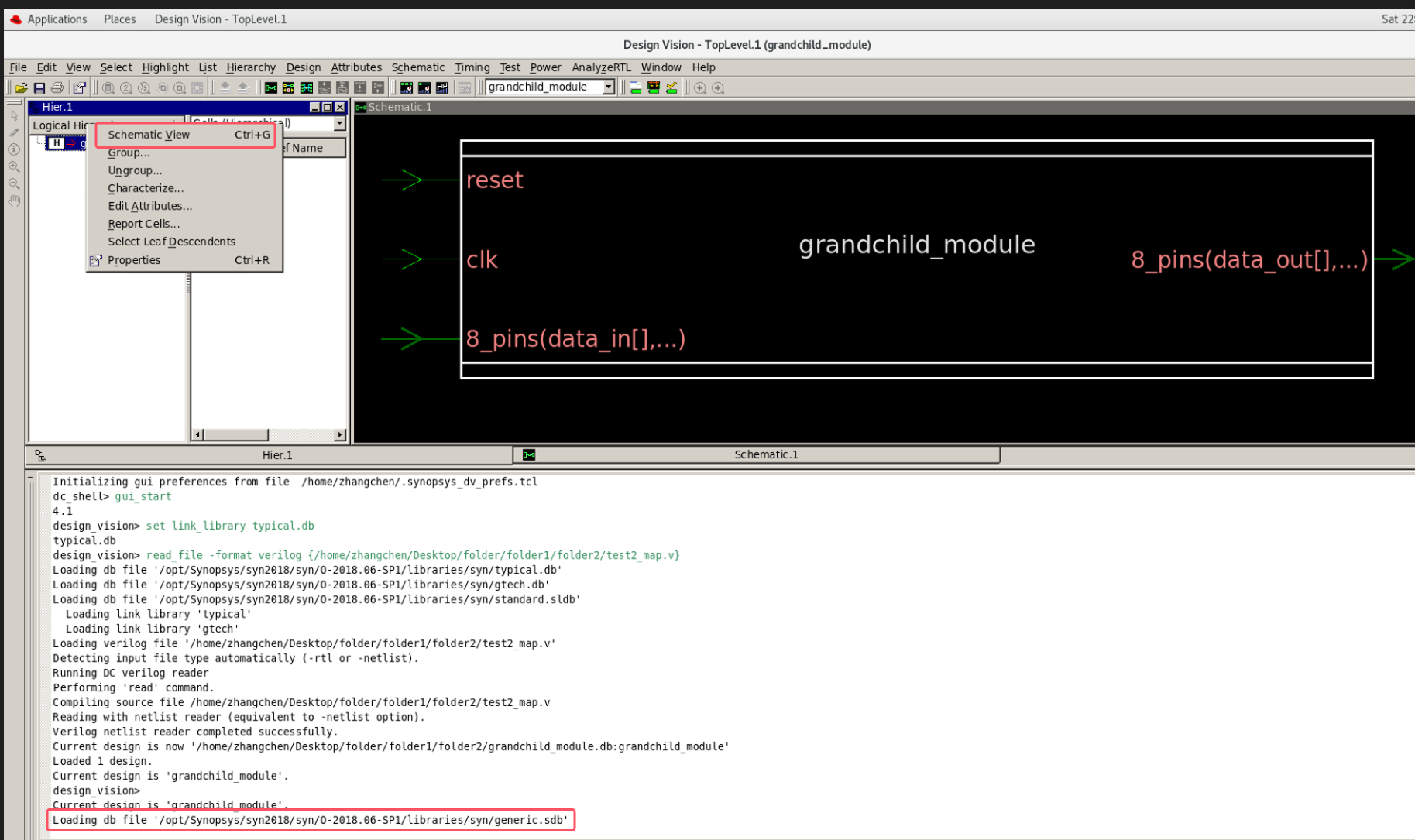

符号库包含在设计原理图中表示库单元的图形符号定义。这些符号库由半导体供应商维护和分发。Design Compiler使用符号库来生成原理图视图。要查看原理图,必须使用Design Vision工具。当你生成原理图时,Design Compiler会将网表中的单元与符号库中的单元进行一对一的映射。

每个Design Compiler的安装包中都包含一个默认的符号库文件generic.sdb,该文件位于Design Compiler安装目录/libraries/syn中。这个文件包含通用符号以及所有Verilog标准逻辑门符号。

为了加载原理图符号,Design Vision首先会检查你通过symbol_library变量指定的符号库文件。例如,symbol_library变量的值为tech.sdb时,工具会在名为tech.sdb的文件中搜索符号。

如果指定的库中不包含所需符号,工具会搜索Design Compiler安装目录/libraries/syn目录中的generic.sdb文件。如果还是没有找到匹配项,工具会将单元实例显示为矩形,这是默认的表示形式。

与逻辑库相同,如果只有符号库的源代码(例如.slib格式),则需要首先使用Library Compiler将其编译为.sdb格式。

综合库

DesignWare库是一个可重用电路设计构建模块(组件)的集合,与Synopsys的综合环境紧密集成。在综合过程中,Design Compiler会从DesignWare库中选择速度和面积优化最优的组件。Synopsys提供了实现许多实现内置HDL操作符的DesignWare组件,这些操作符包括取绝对值、加法、减法、比较、移位、乘法、除法等。除此之外,你可以使用DesignWare Developer在本地开发个性化的DesignWare库,或者从Synopsys或第三方获得DesignWare库的许可。要使用许可的DesignWare库,你需要获取这些库的许可证密钥。

如果在synthetic_library变量中设置的任何DesignWare库需要DesignWare许可证,Design Compiler会检查该许可证。无需指定内置HDL操作符的标准综合库standard.sldb(或者称为Basic DW),因为Design Compiler会自动使用此库。如果进阶综合库dw_foundation.sldb(或者称为Licensed DW)不在synthetic_library中,但已成功检查出DesignWare许可证,dw_foundation.sldb库会自动添加到synthetic_library中。这种行为仅适用于compile_ultra命令(提示:Warning: DesignWare synthetic library dw_foundation.sldb is added to the synthetic library in the current command. (UsN-4)),用户指定的synthetic_library和link_library不会受到影响。

一般来说,compile命令默认使用标准综合库(除非将进阶综合库添加到synthetic_library中),compile_ultra命令可以使用标准综合库和进阶综合库(自动添加)。

默认情况下,所有DesignWare层次结构在使用compile_ultra命令综合的过程中会被无条件解组。你可以通过将compile_ultra_ungroup_dw变量设置为false来防止这种解组行为(默认值为true)。在Synthetic modules较小,比如三位乘法器时,无论是compile命令还是compiler_ultra命令都会对Synthetic modules进行解组,此时无论compile_ultra_ungroup_dw变量为何值。

物理库

Synopsys曾经推出过一个用于物理综合的工具——Physical Compiler,它将逻辑综合和物理设计整合在一个工具中。这意味着在综合阶段就可以引入物理信息,如单元的物理布局、线长、拥塞情况等,而不用等到布局布线阶段才发现物理设计。进行物理综合时,需要物理库,它可以是.pdb格式(Library Compiler编译.plib文件或者.lef文件(Library Exchange Format)生成),也可以是Milkyway设计库(Milkyway参考库和技术文件生成)。

后来推出的DC Ultra有topographical模式,这时不再使用线负载模型作为互联延迟的估算方式,而是根据单元的布局情况计算延迟,这种模式下也需要物理库,最初支持.pdb格式和Milkyway设计库,但是Design Compiler 2009版本中,.pdb格式的物理库已经不受支持了。

详细说明

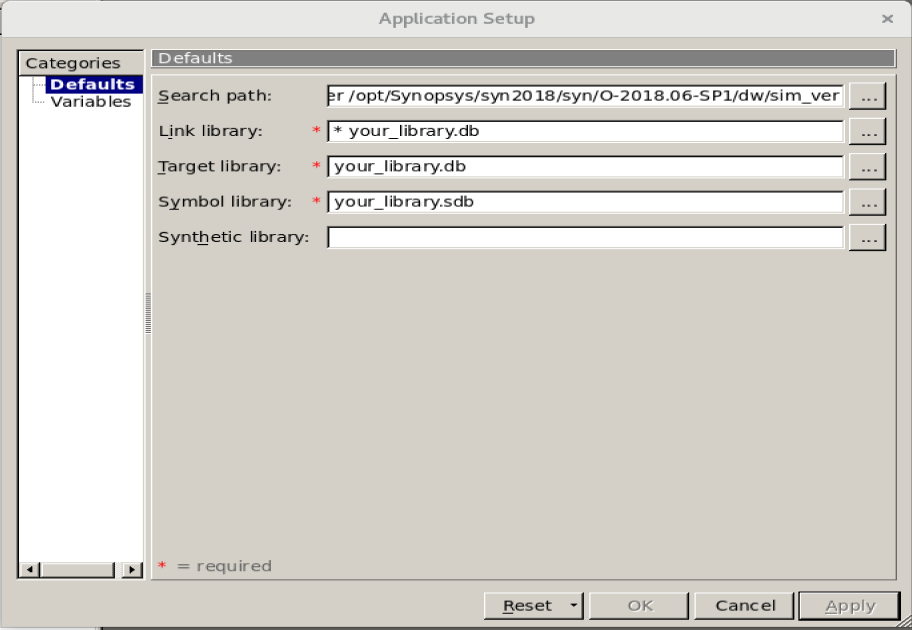

在默认的情况下,Design Compiler默认的库变量的设置情况如例1所示,这因为Design Compiler安装目录/admin/setup下的.synopsys_dc.setup初始化文件有相关初始化设置命令,该文件会在每次Design Compiler启动时自动执行。

# 例1

dc_shell> printvar target_library # 或者使用echo命令和puts命令

target_library = "your_library.db"

dc_shell> printvar link_library

link_library = "* your_library.db"

dc_shell> printvar symbol_library

symbol_library = "your_library.sdb"

dc_shell> printvar synthetic_library

synthetic_library = ""在Design Vision也能观察到这些变量默认的值,如图1所示。

图1 变量设置窗口

为了更好地说明,首先在Design Compiler的启动目录中新建一个.synopsys_dc.setup文件,加入例2所示的命令,Design Compiler会优先执行启动目录下的初始化文件。

# 例2

set_app_var target_library "" # 或者使用set命令

set_app_var link_library ""

set_app_var symbol_library ""

set_app_var synthetic_library "" 目标库的使用

此时我们使用read_verilog命令或read_file命令读取一个未映射的Verilog文件时,此时输出如例3所示。

# 例3

dc_shell> read_verilog test2.v

Loading db file '/opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn/gtech.db'

Loading db file '/opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn/standard.sldb'

Loading link library 'gtech'

Loading verilog file '/home/zhangchen/Desktop/folder/folder1/folder2/test2.v'可以看出在读取Verilog文件前,Design Compiler首先自动读取了两个库文件,即使它们并未显式设置,gtech.db库被设置为了链接库,这是为了解析从Verilog格式转化后的GTECH格式,而standard.sldb库用于DesignWare组件。

此时无法直接综合,如例4所示。

# 例4

dc_shell> compile -exact_map

Warning: No target library specified. (UIO-15)即使使用read_db或者read_file命令读取了一个库文件也是徒劳的,如例5所示。

# 例5

dc_shell> read_db typical.db

Loading db file '/opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn/typical.db'

Loaded 0 designs.

dc_shell> list_lib

Logical Libraries:

-------------------------------------------------------------------------

Library File Path

------- ---- ----

gtech gtech.db /opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn

standard.sldb standard.sldb /opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn

typical typical.db /opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn

1

dc_shell> compile -exact_map

Warning: No target library specified. (UIO-15)

0这是因为target_library变量为空,所以即使库文件已经被读取,Design Compiler也不知道要使用其进行综合。

例6设置了target_library变量的值为typical.db,并成功进行了综合。

# 例6

dc_shell> set_app_var target_library typical.db # 或者使用set命令

typical.db

dc_shell> compile -exact_map

Information: Evaluating DesignWare library utilization. (UISN-27)

============================================================================

| DesignWare Building Block Library | Version | Available |

============================================================================

| Basic DW Building Blocks | O-2018.06-DWBB_201806.1 | * |

| Licensed DW Building Blocks | | |

============================================================================

Beginning Pass 1 Mapping

------------------------

Processing 'grandchild_module'

Updating timing information

Information: Updating design information... (UID-85)

Information: Design 'grandchild_module' has no optimization constraints set. (OPT-108)

Beginning Mapping Optimizations (Medium effort)

-------------------------------

Structuring 'grandchild_module'

Mapping 'grandchild_module'

TOTAL

ELAPSED WORST NEG SETUP DESIGN

TIME AREA SLACK COST RULE COST ENDPOINT

--------- --------- --------- --------- --------- -------------------------

0:00:01 194.0 0.00 0.0 0.0

0:00:01 194.0 0.00 0.0 0.0

0:00:01 194.0 0.00 0.0 0.0

0:00:01 194.0 0.00 0.0 0.0

0:00:01 194.0 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

Beginning Delay Optimization Phase

----------------------------------

TOTAL

ELAPSED WORST NEG SETUP DESIGN

TIME AREA SLACK COST RULE COST ENDPOINT

--------- --------- --------- --------- --------- -------------------------

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

Beginning Area-Recovery Phase (cleanup)

-----------------------------

TOTAL

ELAPSED WORST NEG SETUP DESIGN

TIME AREA SLACK COST RULE COST ENDPOINT

--------- --------- --------- --------- --------- -------------------------

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

0:00:01 126.3 0.00 0.0 0.0

Loading db file '/opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn/typical.db'

Note: Symbol # after min delay cost means estimated hold TNS across all active scenarios

Optimization Complete

---------------------

1其实在这里例5所示的手动读取库文件是不必要的,只要设置了target_library变量,其所指定的库会在使用综合命令后自动进行读取(如有必要,例6没有读取是因为库文件已被读取)。

链接库的使用

随后我们需要保存综合结果,可以将其保存为一个已映射的Verilog文件(.v格式),或者是一个已映射的设计文件(.ddc格式或.db格式(不推荐)),它们两个的区别在于,如果保存为已映射的Verilog文件,则只会保留网表信息,而如果保存为已映射的设计文件,则会保存所有信息(包括设计的约束)。

已映射的Verilog文件

例7使用write_file命令将综合结果保存为已映射的Verilog文件。

# 例7

dc_shell> write_file -format verilog -output test2_map.v

Writing verilog file '/home/zhangchen/Desktop/folder/folder1/folder2/test1_map.v'.

1例8首先是移除所有设计,随后读取已映射的Verilog文件。

# 例8

dc_shell> remove_design -designs

Removing design 'grandchild_module'

dc_shell> read_verilog test2_map.v

*****此时如果使用link命令,则会出错,如例9所示。

# 例9

dc_shell> link

Linking design 'grandchild_module'

Using the following designs and libraries:

--------------------------------------------------------------------------

Information: Building the design 'DFFRQX2'. (HDL-193)

Warning: Cannot find the design 'DFFRQX2' in the library 'WORK'. (LBR-1)

Information: Building the design 'CLKINVX1'. (HDL-193)

Warning: Cannot find the design 'CLKINVX1' in the library 'WORK'. (LBR-1)

Warning: Unable to resolve reference 'DFFRQX2' in 'grandchild_module'. (LINK-5)

Warning: Unable to resolve reference 'CLKINVX1' in 'grandchild_module'. (LINK-5)

0上面的提示说明Design Compiler无法解析引用,这是意料之中的,因为此时即使target_library变量的值为typical.db,而link_library变量为空(即使库文件已经被读取),Design Compiler此时只能使用gtech.db库作为链接库,如果不是碰巧有同名单元,这是不会成功的。

例10设置了link_library变量的值为typical.db,并成功进行了引用解析。

# 例10

dc_shell> set_app_var link_library typical.db # 或者使用set命令

typical.db

dc_shell> link

Linking design 'grandchild_module'

Using the following designs and libraries:

--------------------------------------------------------------------------

typical (library) /opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn/typical.db

1顺带一提的是,就像target_library变量所指定的库文件会在使用综合命令后自动进行读取一样,link_path所指定的库文件和设计文件会在必要时自动读取。

已映射的设计文件

例11使用write_file命令将综合结果保存为已映射的设计文件。

# 例11

dc_shell> write_file -format ddc -output test2_map.ddc

Writing ddc file 'test2_map.ddc'.

1例12首先是移除所有设计,随后读取已映射的设计文件。

# 例12

dc_shell> remove_design -designs

Removing design 'grandchild_module'

dc_shell> read_file -format ddc test2_map.ddc

*****此时如果使用link命令不会出错,即使link_library变量为空,如例13所示。

# 例13

dc_shell> link

Linking design 'grandchild_module'

Using the following designs and libraries:

--------------------------------------------------------------------------

typical (library) /opt/Synopsys/syn2018/syn/O-2018.06-SP1/libraries/syn/typical.db

1这是因为在综合后,设计的local_link_library属性会被设置为target_library变量的值,将设计保存为.ddc格式会保留这些属性(当读取一个设计文件时,如其有local_link_library属性指定的库,也会像link_library变量一样自动读取),解析引用时local_link_library属性指定的库文件也会被搜索。需要注意的是,local_link_library属性只对当前设计生效,如果一个模块是当前设计的一个子模块,则该模块的local_link_library属性不会被使用,只有link_library变量和当前设计的local_link_library属性会被使用。

link_library变量中的*

link_library变量的默认值包含符号*,这表示Design Compiler会在内存中查找引用,例如父模块child_module中引用了grandchild_module模块且它们都已被读取,则可以正常解析引用并构建层次关系。

link_library变量中的设计文件

link_library变量除了可以包含符号*,库文件之外,还可以包含设计文件(.ddc格式或.db格式)。假设这样一个场景,grandchild_module模块已被综合且被保存为已映射的设计文件,将link_library变量设置为相应的库后,将grandchild_module模块所属的设计文件也添加进link_library变量后,此时只读取父模块child_module就会自动读取link_library变量中的库文件和设计文件,这就可以找到grandchild_module模块的引用而无需将两个模块都用命令读取。

符号库的使用

符号库会在查看原理图后自动读取,如图2所示。

图2 符号库的加载

综合库的使用

运算符推断

以例14的RTL代码为例进行说明,其中包括一个加法运算符和一个乘法运算符。

// 例14

module top_module (

input wire clk,

input wire rst_n,

input wire [3:0] in_a,

input wire [3:0] in_b,

output wire [4:0] sum,

output wire [7:0] product

);

wire [3:0] intermediate_sum;

// 实例化加法子模块

adder u_adder (

.a(in_a),

.b(in_b),

.sum(intermediate_sum)

);

// 实例化乘法子模块

multiplier u_multiplier (

.a(in_a),

.b(in_b),

.product(product)

);

// 将加法结果扩展为5位输出

assign sum = {1'b0, intermediate_sum}; // 高位补0

endmodule

// 子模块1:加法器

module adder (

input wire [3:0] a,

input wire [3:0] b,

output wire [3:0] sum

);

assign sum = a + b;

endmodule

// 子模块2:乘法器

module multiplier (

input wire [3:0] a,

input wire [3:0] b,

output wire [7:0] product

);

assign product = a * b;

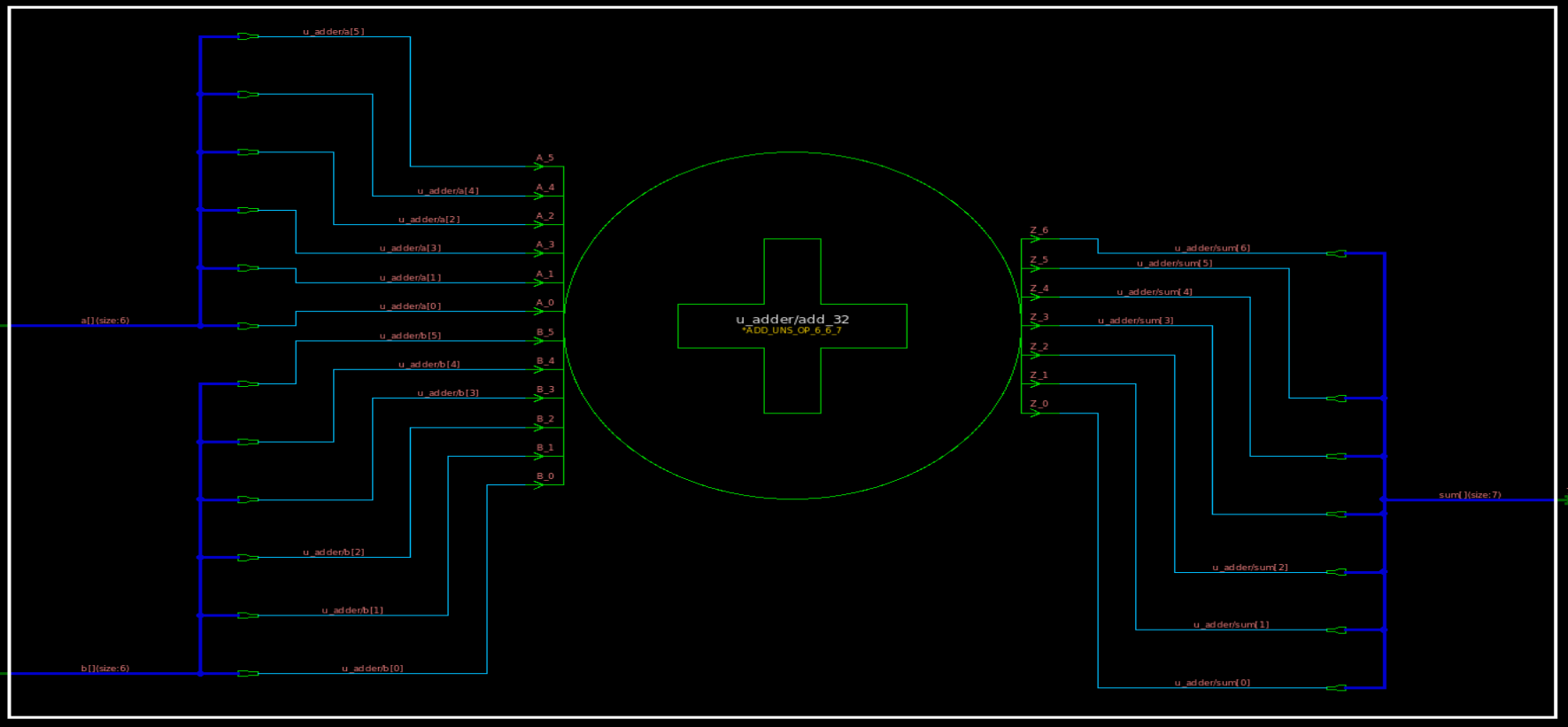

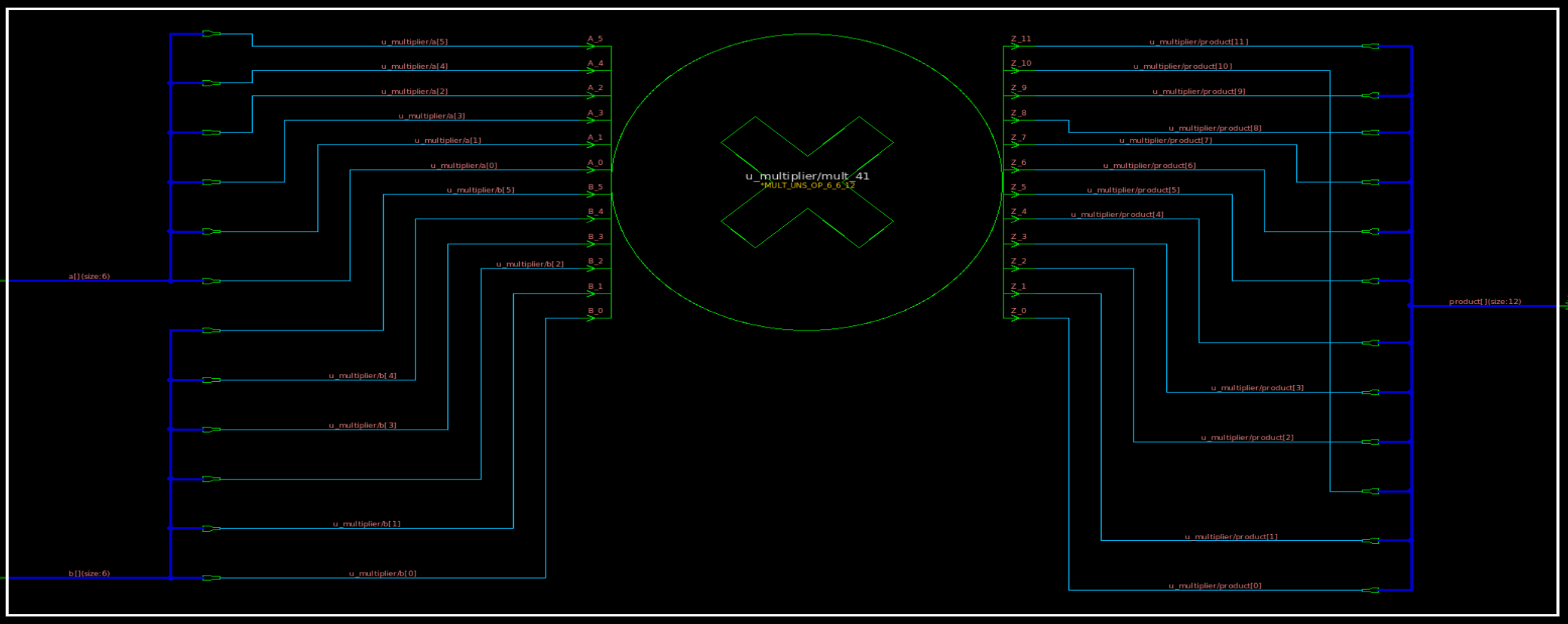

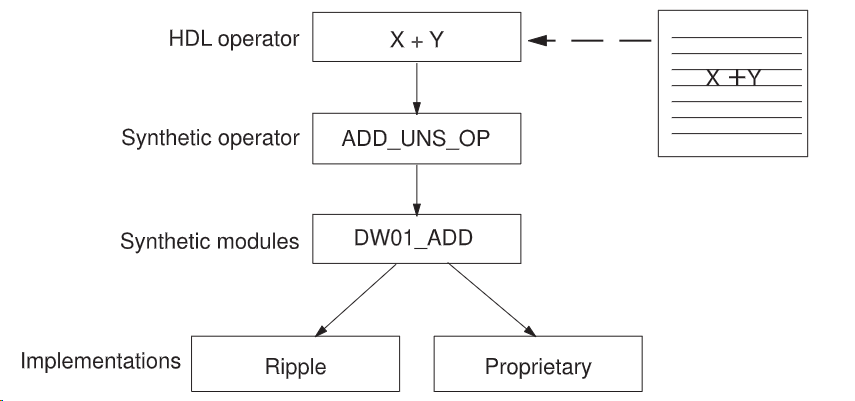

endmodule当把例14读取进Design Compiler时,在DesignVision中打开原理图可以看到一个加号和乘号模块,分别名为ADD_UNS_OP_6_6_7(即无符号,输入为6位,输出为7位的加法运算),如图3所示,和MULT_UNS_OP_6_6_12(即无符号,输入为6位,输出为12位的乘法运算),如图4所示。它们实际上是GTECH形式的模块,由Design Compiler中的HDL Compiler进行转换得来,如图5所示。

图3 加法运算符

图4 乘法运算符

图5 运算符映射

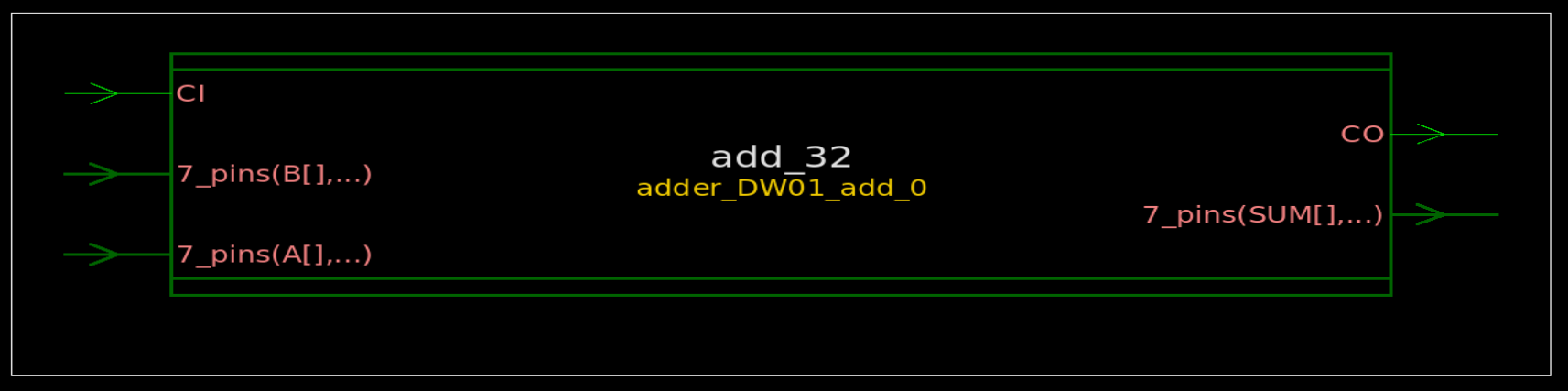

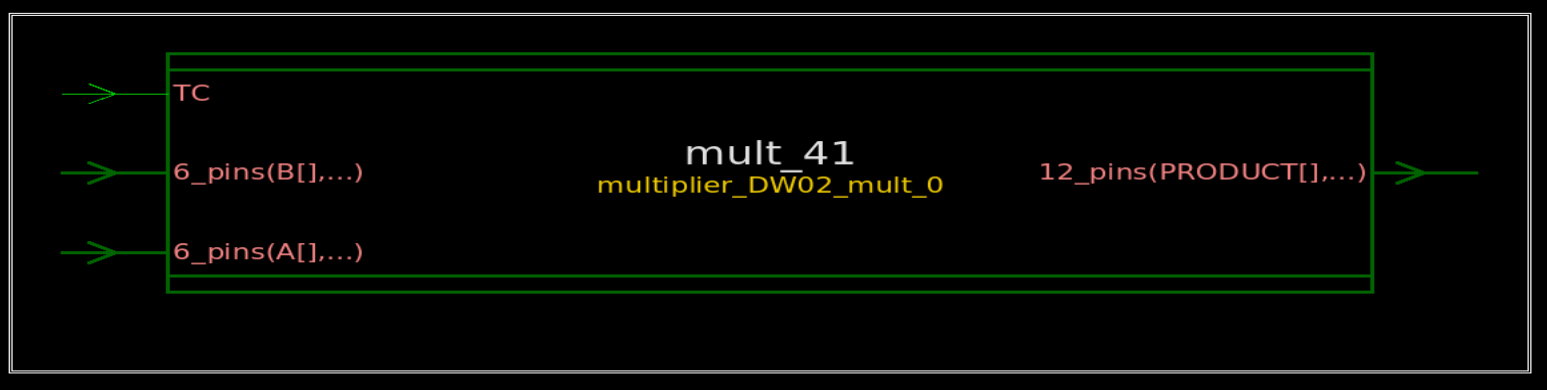

综合完成后,加法运算符和乘法运算符被映射到了DesignWare组件(或者说图5中的Synthetic modules),如图6和图7所示。

图6 映射后的加法器

图7 映射后的乘法器

显式例化

显式例化Synthetic modules也是可行的,但需要提供相关参数,如在例15中显式例化了一个乘法器DW02_mult,提供了输入位宽参数。

// 例15

module top(input [9:0]A, B, output [19:0]PRODUCT);

DW02_mult #(.A_width(10), .B_width(10))

(.A(A), .B(B), .PRODUCT(PRODUCT));

endmodule有些Synthetic modules只能显式例化而无法推断,比如RAM,如下所示。

DW_ram_r_w_s_lat #(WIDTH,DEPTH) memory(.clk(push_clk),

.cs_n(1'b0),

.wr_n(~push),

.rd_addr(rd_address),

.wr_addr(wr_address),

.data_in(data_in),

.data_out(dataout));顺带一提,如果想强制一个运算符的实现方式,可以显式例化Synthetic modules并在Design Compiler中使用set_implementation命令(这只针对compile命令,如果使用compile_ultra命令,Design Compiler可能拒绝用户设置的实现方式并选择有更好QoR的实现)。

最佳实践

一般情况下,会将target_library设置为需要映射到的工艺库,而link_library设置为[list * $target_library $synthetic_library 其他宏单元]。

2181

2181

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?