RF 和 BBPLL 合成器 RF AND BBPLL SYNTHESIZER

1.概述

AD9361收发器包含两个相同的RFPLL(射频锁相环)合成器,用于产生所需的LO(local oscillator 本振)信号,分别独立编程。一个用于Rx通道,另一个用于Tx通道。收发器还包含一个BBPLL(基带锁相环)合成器,用于生成所需的采样和内部操作时钟。PLL合成器均为分数-N架构,具有完全集成的VCO和环路滤波器,不需要外部部件即可覆盖整个设备的频率范围。该配置允许使用任何方便的参考频率在任何通道上以任何采样率进行操作。对于**FDD(分频双工)**操作,Tx和Rx的频率可以相同也可以不同,并且两个RFPLL合成器同时工作。对于TDD操作,RFPLL合成器会根据Rx和Tx帧交替打开。

2.RFPLL 介绍

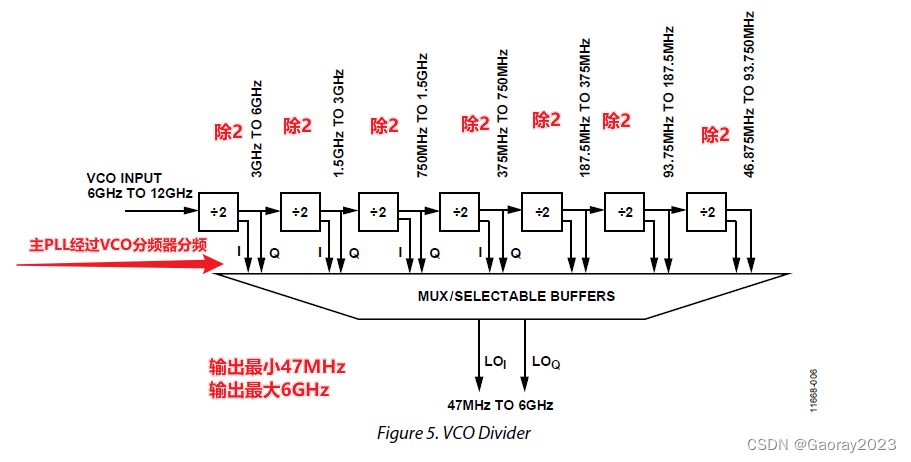

RFPLL的基本频率为6 GHz至12 GHz。通过将PLL频率分频,可以创建介于47 MHz至6 GHz的本地振荡器频率。Rx PLL通过ad9361_set_rx_lo_freq函数进行配置和校准,而Tx PLL则通过ad9361_set_tx_lo_freq函数进行配置。每个合成器必须分别配置和校准。

AD9361 PLL架构:包含参考块、主PLL块和LO GEN输出块。VCO始终在6 GHz至12 GHz之间工作。

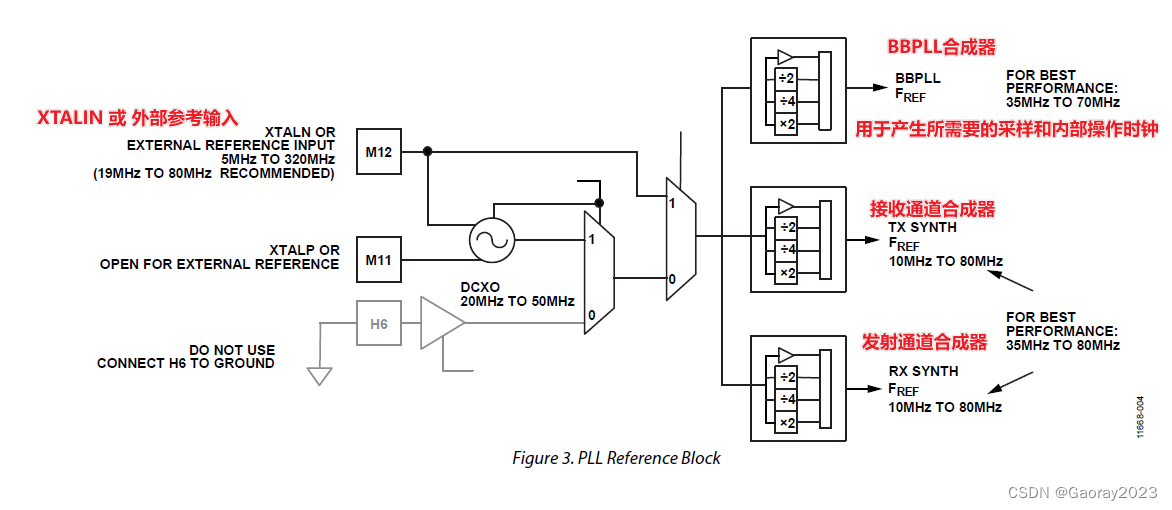

3. 参考块

参考频率可以通过芯片上的DCXO生成,也可以由外部时钟源提供。一个MUX选择所需的源。然后,将参考分割并应用于三个独立的调理块,也称为参考分频器。调理块提供四个选项,即将PLL参考频率FREF(应用于PLL相位检测器的环路参考)缓冲、加倍、减半或除以4。独立的块使得可以为RF和BBPLL设置不同的FREF。参考标度器将由ad9361_init函数设置。为了获得最佳的RFPLL性能,Analog Devices建议选择一个能够尽可能接近80 MHz的参考时钟或晶体。

4.主PLL块

独立的Rx和Tx PLL使用分数-N技术来实现通道合成。整个PLL集成在芯片上,包括VCO和环路滤波器。PLL始终在6 GHz至12 GHz的范围内运行。电荷泵电流可编程,所有环路滤波器组件也可编程,允许针对几乎任何应用优化性能参数。配置特定频率的过程包括计算所需的分频器数值组合,并参考模拟器件提供的查找表,以在温度变化下配置VCO以实现稳定性能。

主PLL(锁相环)输出经过VCO(压控振荡器)分频器块分频,以创建频率带,使设备可以从70 MHz至6 GHz连续运行。图5显示了如何创建这些频率带。在ad9361_rx_lo_freq和ad9361_tx_lo_freq函数调用中,合成器配置寄存器、环路滤波器、整数和分数字、以及VCO分频器都将被计算。

5.电荷泵电流

电荷泵电流是6位可编程的,范围从0.1 mA到6.4 mA,步长为0.1 mA。电荷泵电流需要在初始化期间进行校准,然后在操作期间可以使用模拟器件提供的查找表。

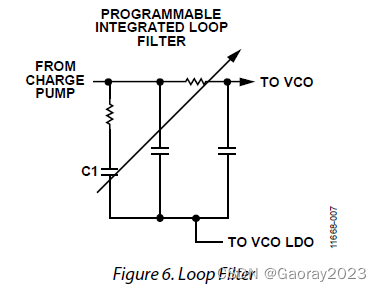

6.RFPLL环路滤波器

RFPLL环路滤波器完全集成在芯片上,是一个标准的被动Type II三阶滤波器,具有五个4位可编程组件(见图6)。环路滤波器值包含在模拟器件提供的合成器查找表中,并且不应进行修改。

7.VCO配置

VCO配置包括从模拟器件提供的查找表中写入几个静态寄存器,然后启用自动校准程序来配置VCO调谐电压(Vtune)和ALC。触发VCO校准的方式有三种:从等待状态到警报状态时,从合成器关机状态到警报状态时(TDD),或者写入Rx或Tx频率整数字的最低有效位时。所有关于VCO、环路滤波器和其他合成器设置的查找表写入应在触发VCO校准之前写入芯片。需要注意的是,在开始VCO校准之前应完成电荷泵校准。

在使用硬件(ENABLE/TXNRX)控制的TDD模式下,当设备状态机处于警报状态时,合成器会随着TXNRX控制线的状态而上下电。TDD操作的典型示例序列是Rx-ALERT-Tx-ALERT-Rx。BB控制器通过在警报状态下设置TXNRX线的电平来将设备引导到正确的下一个状态。然后,状态机在下一个ENABLE边沿处进入下一个状态。在警报状态期间,由于BB控制器将TXNRX的电平从低变为高,Rx合成器关闭,Tx合成器打开,并且触发Tx VCO校准。类似地,在随后的周期中,当BB控制器将TXNRX的状态从高变为低时,Tx合成器关闭,Rx合成器打开,并且触发Rx VCO校准。操作上,BB处理器应在进入警报模式后不久将TXNRX线转换,以便合成器在帧之间有尽可能多的时间进行校准和锁定。典型的TDD校准加锁时间在45μs至60μs左右。有关更快的锁定时间,请参阅TDD模式更快锁定时间部分。

8.VCO校准

校准完成所需的时间是可编程的。通常,对于TDD系统,快速校准是合适的,而对于FDD系统,慢速校准是合适的。对于TDD系统,合成器只会开启很短的时间,因此温度漂移导致失锁的风险很小。对于FDD系统,合成器可能会无限期地被锁定,因此需要更长时间的、更准确的校准来确保Vtune足够中心化。示例校准时间在RF合成器VCO校准部分中显示。

该设备包括一个快速锁定模式,可以通过将所有合成器编程信息,包括本节的VCO校准结果,存储到设备寄存器或BB处理器内存空间中,以便在以后的时间重新调用,从而实现比正常频率更快的变化。有关详细信息,请参阅快速锁定配置文件部分。

VCO Vtune测量

出于调试目的,Vtune电压可以输出到封装引脚。Vtune电压与相应的(Rx或Tx)EXT_LO_IN引脚进行MUX。通过设置VTune Out位,0x23B[6](Rx)或0x27B[6](Tx)进行配置。对于正常操作,这些位应清除。

9.锁定检测器

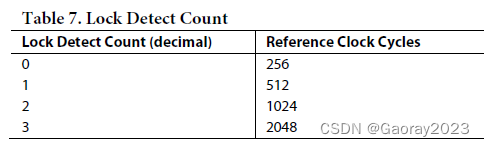

提供了一个锁定检测器位,用于指示对应的合成器在配置的时钟数中已经实现锁定。锁定检测器通过设置锁定检测配置寄存器中的模式和计数值来配置。

锁定检测计数位设置了RFPLL锁定的最大时间。如果在指定的时间内锁定,锁定位将变高。时间按照表7中的参考时钟周期进行测量。建议使用至少1024个参考时钟周期。

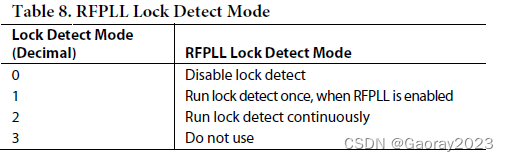

锁定检测模式位根据表8设置锁定检测的操作模式。建议使用连续运行锁定检测模式。

10.合成器查找表

模拟器件提供了合成器查找表,用于生成VCO和环路滤波器所需的静态寄存器写入。有一组用于FDD操作的表,以及一组用于TDD操作的表。每组表覆盖整个VCO频率范围,以及三种不同的RFPLL环路参考频率。FDD表使得VCO温度补偿能够生效,意味着用户将使用更长、更准确的校准时间,以使设备能够无限期地保持运行。在TDD表中,未启用温度补偿,因为假定VCO将在Tx和Rx帧之间进行校准。如果TDD操作需要温度补偿,则可以在TDD合成器校准期间使用FDD表。

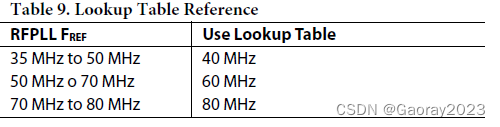

提供的查找表分为三个表,对应40 MHz、60 MHz和80 MHz参考频率。要使用的正确表是与操作模式的环路FREF最接近的表。请参考表9根据基于LUT选择的选择。

11.TDD模式更快的锁定时间

在TDD模式下,Rx和Tx合成器会根据TXNRX控制线的状态交替开启和关闭。通常情况下,合成器被设置为每次上电时都触发VCO校准,以便获得新鲜的校准值。如果TDD中的LO频率在帧与帧之间不变,则不需要每次重新校准VCO。合成器在关机后仍保留VCO校准结果。在相同的LO频率下的Tx/ALERT/Rx之间进行突发时,合成器只需要重新锁定,可能可以在25微秒或更短的时间内完成,这取决于环路带宽。

设置合成器在此模式下:

1.设置VCO进行FDD校准。

2.执行VCO校准。

3.设置禁用VCO校准位。

第3步禁用所有VCO校准的触发,包括写入新的整数字。如果需要新的校准,则必须清除此位。

需要注意的是,如果LO频率发生变化,则需要重新校准VCO。

12.外部LO

与始终从6 GHz到12 GHz操作的内部合成器不同,使用外部LO时应用的频率是所需RF LO频率的2倍。EXT LO信号的范围是从140 MHz到8 GHz,覆盖了70 MHz到4 GHz的RF调谐频率范围。要设置外部LO,请使用ad9361_trx_ext_lo_control函数。

有两个单独的EXT LO输入,一个用于Rx,另一个用于Tx。在AD9361引脚的EXT LO信号的推荐功率级别为−3 dBm ≤ pin ≤ +3 dBm,最大引脚功率不能超过+6 dBm。

需要注意的是,EXT_LO_IN封装引脚是多功能的,当设备使用内部合成器时,它们可以具有不同的功能(Vtune测量)。有关信息,请参阅VCO Vtune测量部分。

13.基带PLL(BBPLL)

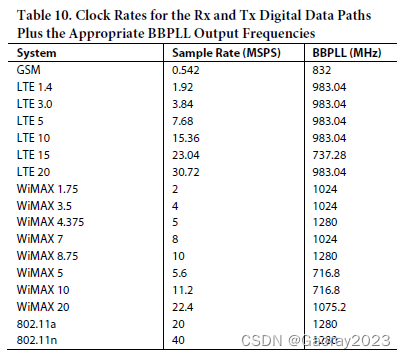

BBPLL(基带锁相环)是用于合成AD9361芯片的数字时钟的分数-N合成器。BBPLL(基带锁相环)合成Rx ADC时钟的整数倍、Tx DAC时钟、所有模拟校准时钟以及数字部分中使用的时钟。BBPLL(基带锁相环)的操作范围为715 MHz至1.430 GHz,这使得可以从任何参考频率生成几乎任何采样率。表10列出了常见通信系统,显示系统采样率及相应的BBPLL频率。BBPLL的输出驱动可编程分频器链,以获得所需的采样率和总线通信速率。通常通过决定如何完成信道滤波来反向计算所需的BBPLL频率,然后选择适当的输出分频器,以使BBPLL在范围内操作。请参阅滤波器指南部分,了解可用的滤波器和降采样/积分设置。

14.BBPLL VCO

BBPLL VCO是一个多频带环形振荡器,其Kv为550 MHz/V,需要在操作前进行频率校准。校准是通过ad9361_bbpll_set_rate函数进行配置和运行的。

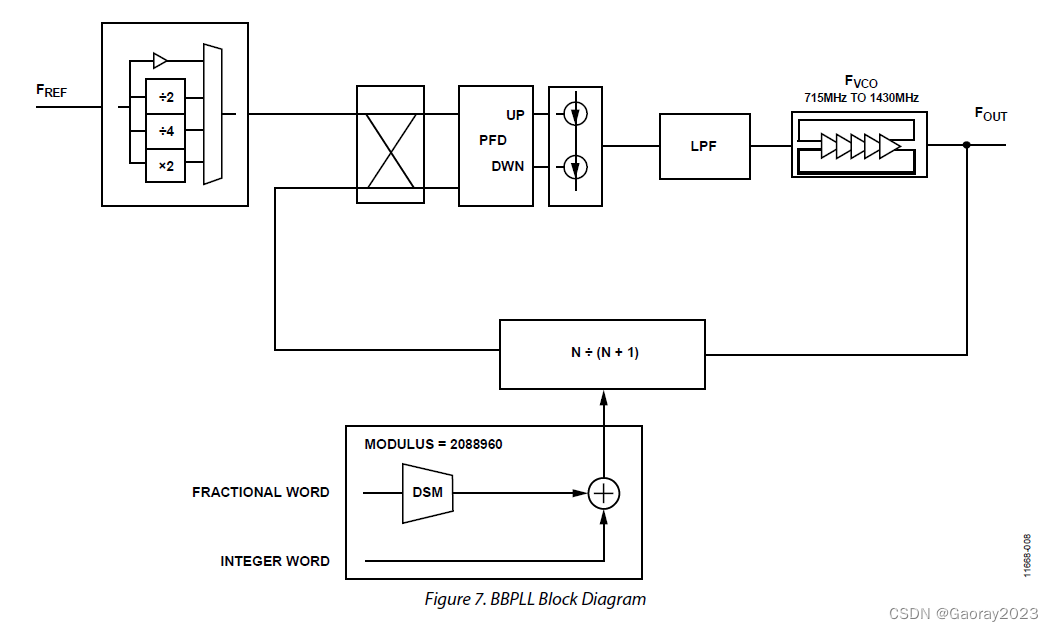

图7是BBPLL的框图。环路的参考频率是参考标度器块的输出,该块与RFPLL的参考标度器块相同,但独立于它们。参考块被配置为在传递给BBPLL相位检测器之前缓冲、倍增或除以设备参考频率。为了获得最佳性能,建议配置BBPLL参考标度器块,使得结果的BBPLL FREF在35 MHz到70 MHz之间。

15.BBPLL电荷泵

电荷泵具有可编程的输出电流,范围从25 μA到1575 μA,步长为25 μA。此外,还提供了可编程的泄漏电流。这是一个NMOS电流源,可编程从0 μA到316 μA。

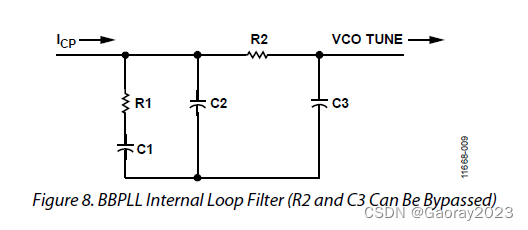

16.BBPLL环路滤波器

环路滤波器完全集成在芯片上,是一个标准的被动Type II三阶滤波器,具有五个可编程组件。该滤波器由ad9361_bbpll_set_rate函数进行编程。

1588

1588

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?