PLL

锁相环 PLL 功能:可以对输入到 FPGA 的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。经过 PLL 后的时钟防抖性能更好,稳定度高。

相关参考:FPGA——PLL

输出的四种模式

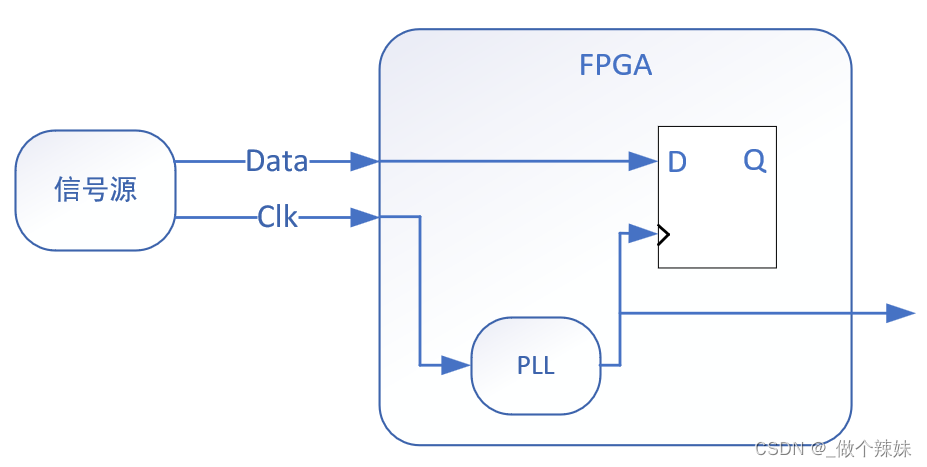

信号源、PLL 与寄存器之间的关系图:

PLL 输出的四种模式:

| 模式 | 含义 | 应用场合 |

|---|---|---|

| 源同步模式 | Data 和 Clk 来源于同一信号源。对经 PLL 后的 Clk 进行补偿,以保持 Clk 与 Data 的相位同步 | 高速的数据接口 |

| 无补偿模式 | 指 PLL 不对 Clk 进行任何补偿 | |

| 标准模式 | 针对 PLL 到寄存器的相位进行补偿 | 用于内部寄存器 |

| 零延迟缓冲模式 | 针对输出时钟进行补偿 | 用于时钟输出 |

没有特殊需求的话,一般选择标准模式。

时钟信号的选取

- 由于锁存器产生的时钟信号选用全局时钟线进行传输,全局时钟线的传输时间相较普通线来说可视为无延时,所以锁存器产生的时钟信号到各个寄存器是没有相位差的,因此优先考虑使用 PLL_IP 产生的时钟信号。

- 若锁存器资源不够,考虑使用计数器的降频方式对时钟信号进行分频,因为通过标志位的方式,当标志位置一时再执行,同样可以达到分频的效果,同时时钟信号选取的仍是系统时钟,不会发生数据错乱的情况。

ROM

只读存储器 ROM(Read-Only Memory) 功能:只能读出事先所存数据的固态半导体存储器,一旦存储不可更改,且资料不会因断电而消失。

RAM

随机存取存储器(Random Access Memory)功能:可随时对任一地址的数据进行读取或写入操作,但断电资料便消失。

分类

- 单端口:读写操作共用一组地址线,读写操作不能同时进行

- 简单双端口:读写操作各占用一个端口,可同时进行读操作和写操作

- 真正双端口:可认为是两个单端口的组合

具体的内容介绍可参考这篇: IP核之RAM

FIFO

FIFO(First In First Out)先入先出式数据缓冲器,用来实现数据先入先出的读写方式。

应用

- 跨时钟域数据处理

由于不同模块使用的时钟信号存在频率或相位上的不一致,因此在跨时钟域情况下进行数据传输时,我们可以采取FIFO数据缓存的方式解决问题。 - 带宽不同步

如果不同模块使用的数据位宽不一致,即带宽不同步的情况下,也可以采取FIFO数据缓存的方式解决问题。

分类

根据读写时钟是否相同,可以将其分为同步FIFO(SCFIFO)和异步FIFO(DCFIFO)。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?