参考:FFT IP核 详细介绍

参考:官方文档介绍

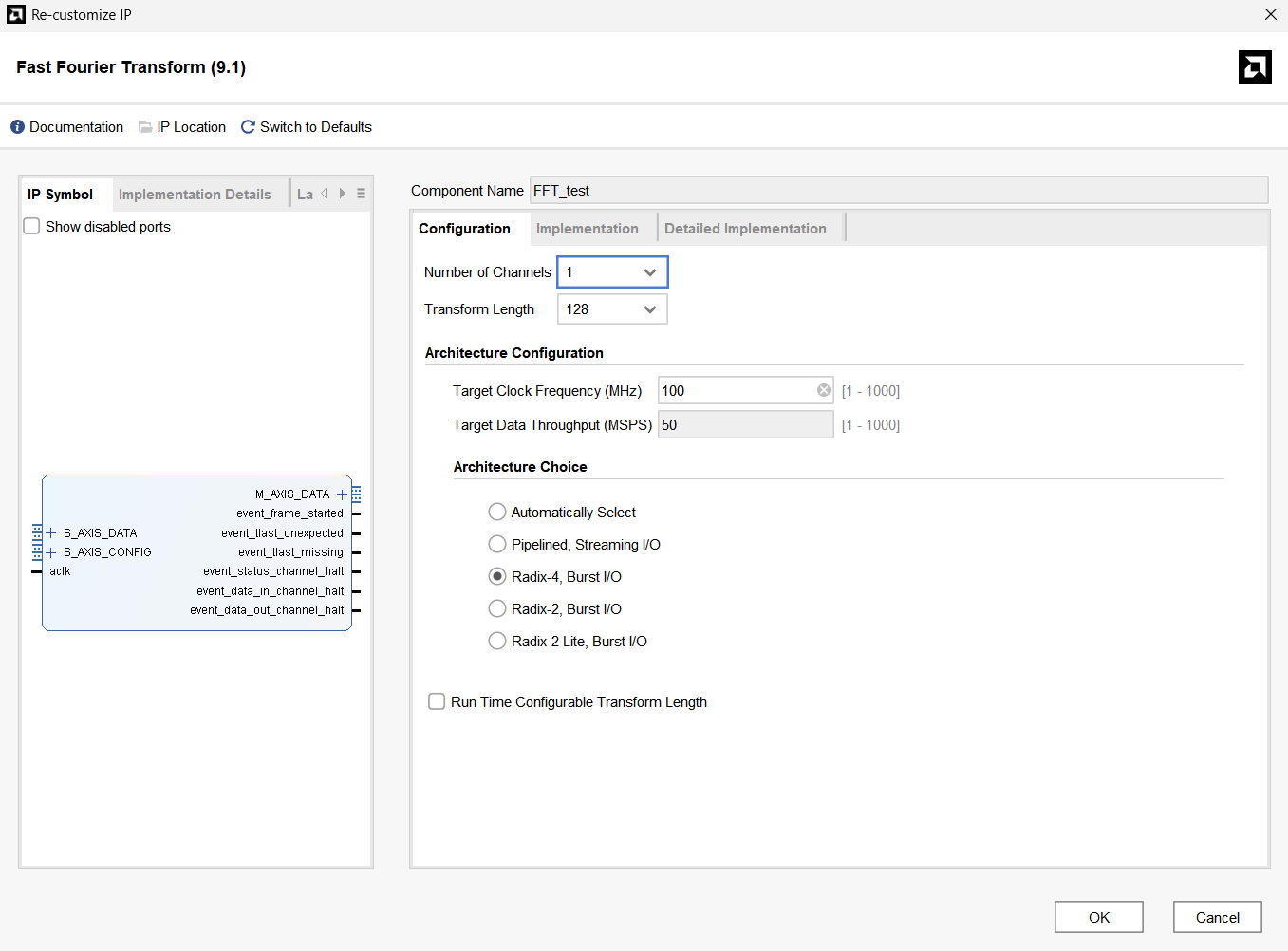

IP 核配置

在 IP Catalog 中搜索:Fast Fourier Transform

按照上图所示进行配置,下文对配置内容进行详述。

- Configuration

- Number of Channels:FFT 通道数,多通道即代表多帧数据同时进行 FFT 计算

- Transform Length:FFT 长度

- 当 Architecture Choise 选择 Automatically Select 时,Target Clock Frequency(期望的时钟频率)和 Target Data Throughput(期望的数据吞吐量)这两个参数用于确定使用的 FFT 架构

- 四种 FFT 架构

- Pipelined Streaming I/O:支持连续的数据流处理,具有最高的处理速度,但资源占用也最多。适用于对实时性要求高的应用

- Radix-4 Burst I/O:资源占用比上级少,处理速度比上级慢

- Radix-2 Burst I/O:资源占用比上级少,处理速度比上级慢

- Radix-2 Lite Burst I/O:资源占用最少,但处理速度最慢。适用于对性能要求不高且资源非常有限的场景。

- Run Time Configurable Transform Length:勾选后,可通过设置 s_axis_config_tdata 中 NFFT 字段的长度来改变 FFT 长度(需小于 Transform Length)

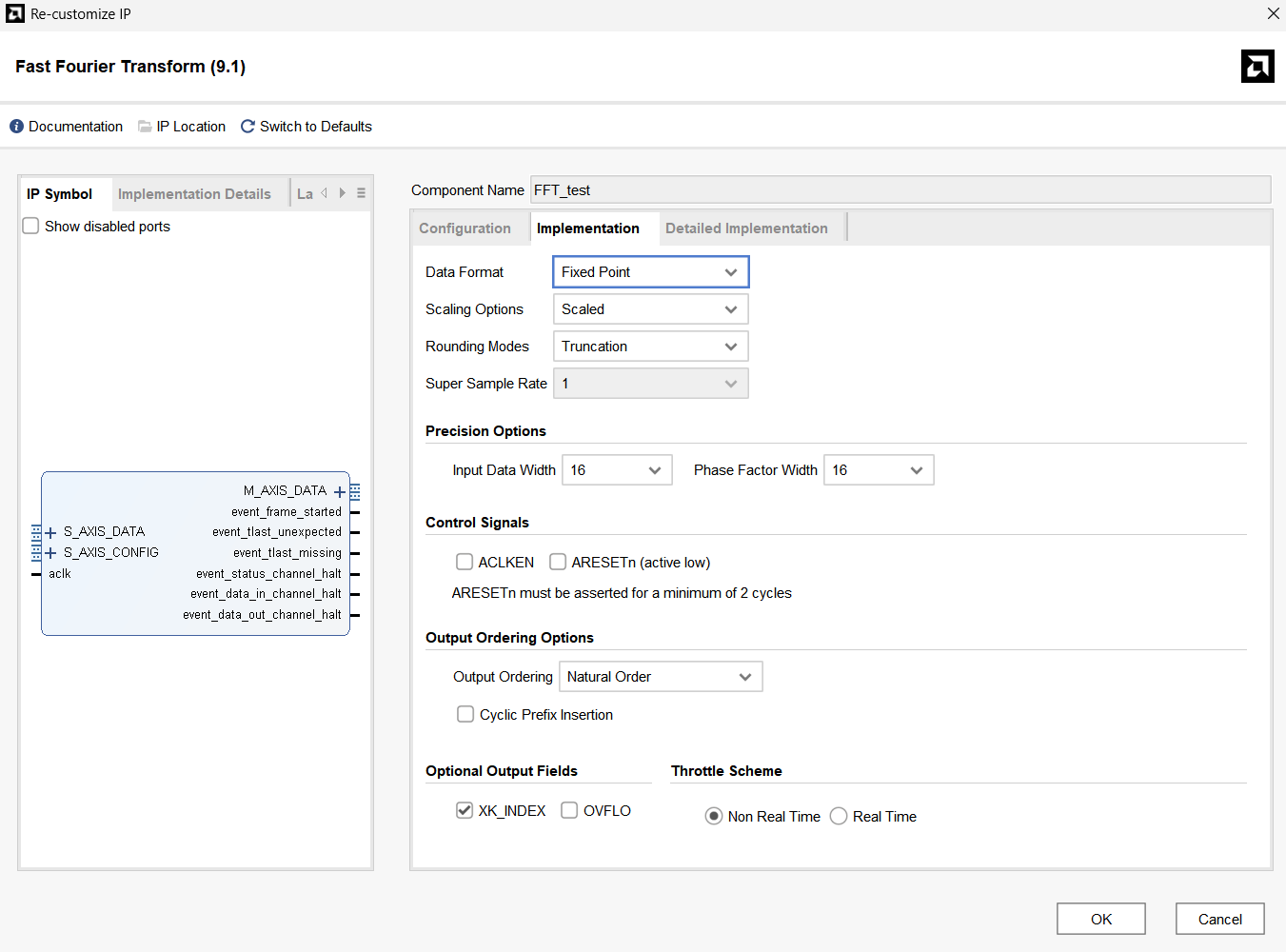

- Implementation

- Data Format:可选定点或浮点

- Scaling Options:在 Radix-4 架构下,每经过一级蝶形运算,值会出现 3bit 的增长;Radix-2 则会出现 2bit 的增长,为避免溢出或资源浪费,需设置缩放模式

- Scaled(缩放):可通过配置缩放因子控制每一级的缩放情况

- Unscaled(未缩放):不对数据进行缩放,输出数据位宽会在计算过程中增长

- Block Floating Point(块浮点缩放):在每个计算阶段动态调整缩放因子,相比于 Scaled 模式,块浮点模式会增加资源使用

- Rounding Modes:Truncation(截断)、Convergent Rounding(收敛舍入,精度高但资源消耗大)

- ACLKEN(使能信号)

- ARESETn(复位信号)

- Output ordering:

- Natural Ordering:输出按顺序排列,已处理过

- Bit/Digit Reversed Order:对于 8 点 FFT,输出顺序为 0、4、2、6、1、5、3、7,需自行后续处理

- XK_INDEX:频谱索引

- OVFLO:溢出指示信号

- Throttle Scheme(节流方案):可选择 Non Real Time(非实时)或者 Real Time(实时)

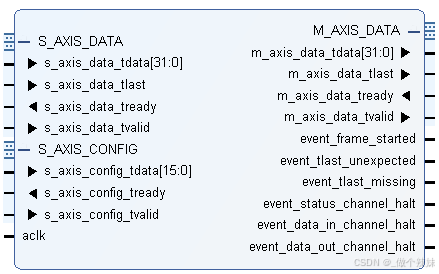

IP 核接口

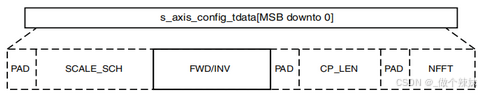

s_axis_config_tdata 配置

| 字段 | 触发条件 | 定义 |

|---|---|---|

| NFFT | 勾选 Run Time Configurable Transform Length | 位宽 5 bit,数值为 log2(FFT点数) |

| CP_LEN | 勾选 Cyclic Prefix Insertion | 循环前缀长度 |

| FWD/INV | 必选 | 1 为 FFT,0 为 IFFT,每个 bit 对应一个 FFT 通道,第一通道放在最低位 |

| SCALE_SCH | Scaling Options 选择 scaled 时 | 配置缩放因子,具体方法见下文 |

| PAD | 自动触发 | 用于 8bit 对齐,当比特数不足 8 时,用零补齐 |

SCALE_SCH 配置方法:

- 基于 Radix-2 架构,蝶形运算的阶数为 log₂(N),基于 Radix-4 和 Pipelined Streaming I/O 架构,蝶形运算的阶数为 log₄(N)

- 对于 Radix-2 和 Radix-4 架构,为每一阶配置一个缩放因子,因子可选 3/2/1/0,每个因子占 2bit

- 因子 3 对应缩放 1/8;因子 2 对应缩放 1/4;因子 1 对应缩放 1/2,一般而言,总放缩系数为 1/N

- 例如,对应 Radix-4 架构的 128 FFT点数,位宽为 2 * ceil( log₄(N) ) = 8,缩放因子可以设置为 [1,2,2,2],高阶放在高位

输入输出端口描述

| 端口 | 方向 | 定义 |

|---|---|---|

| s_axis_config_tdata | IN | 配置数据 |

| s_axis_config_tready | OUT | 表示已准备好接收配置数据 |

| s_axis_config_tvalid | IN | 表示配置数据输入有效 |

| s_axis_data_tdata | IN | 输入数据,[31:16]为虚部,[15:0]为实部 |

| s_axis_data_tlast | IN | 表示输入结束,当 N 点数据输入完后置高 |

| s_axis_data_tready | OUT | 为高时表示 FFT 模块可以接收数据 |

| s_axis_data_tvalid | IN | 表示数据输入有效 |

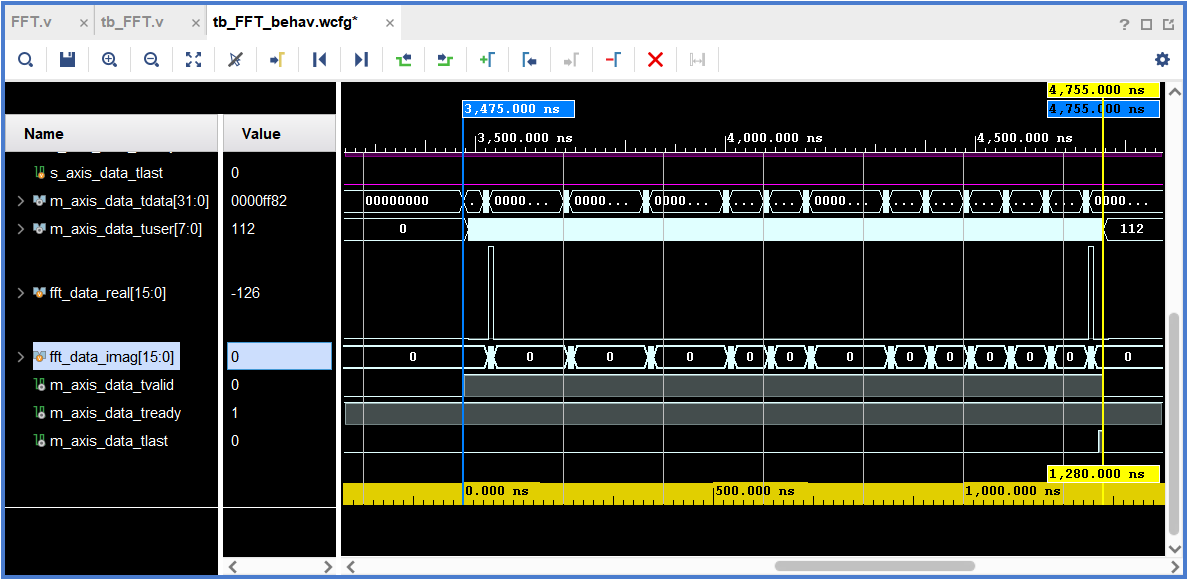

| m_axis_data_tdata | OUT | 输出频谱数据,[31:16]为虚部,[15:0]为实部 |

| m_axis_data_tlast | OUT | 表示输出结束,当 N 点数据输出完后置高 |

| m_axis_data_tready | IN | 表示从设备已准备好数据接收 |

| m_axis_data_tvalid | OUT | 表示数据输出有效 |

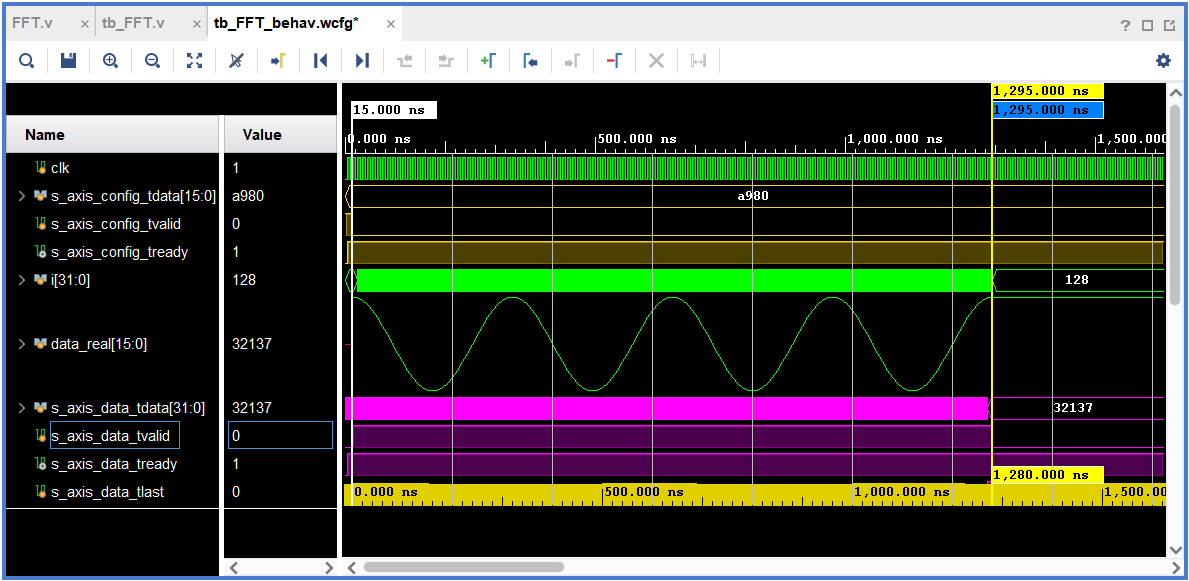

仿真

- s_axis_config_tdata = 16’b10101001_1_0000000; 高八位是缩放因子,低八位是 FWD/INV 和用于补齐的零,如果不使用缩放因子的话,将其配置为 8’b0000_0001

- s_axis_data_tdata [31:16]为虚部,[15:0]为实部,均为有符号数

- 输入信号是频点为 2MHz的单载波,采样率是 64MHz

- s_axis_data_tvalid 要与第一个信号输入的同时拉高,在最后一个信号输出后拉低

- s_axis_data_tlast 是在最后一个信号的所在时钟周期拉高

- m_axis_data_tuser 是频谱索引,m_axis_data_tuser * fs / N 为真实的频点,即 4 * 64M / 128 = 2MHz,与输入设置的相符

5498

5498

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?