题目描述

Create a 16-bit wide, 9-to-1 multiplexer. sel=0 chooses a, sel=1 chooses b, etc. For the unused cases (sel=9 to 15), set all output bits to ‘1’.

代码

// 我的解法

module top_module(

input [15:0] a, b, c, d, e, f, g, h, i,

input [3:0] sel,

output [15:0] out );

always@(*)

case(sel)

4'h0:out=a;

4'h1:out=b;

4'h2:out=c;

4'h3:out=d;

4'h4:out=e;

4'h5:out=f;

4'h6:out=g;

4'h7:out=h;

4'h8:out=i;

default out=16'hffff;

endcase

endmodule

// 参考解法

module top_module (

input [15:0] a,

input [15:0] b,

input [15:0] c,

input [15:0] d,

input [15:0] e,

input [15:0] f,

input [15:0] g,

input [15:0] h,

input [15:0] i,

input [3:0] sel,

output logic [15:0] out

);

// Case statements can only be used inside procedural blocks (always block)

// This is a combinational circuit, so use a combinational always @(*) block.

always @(*) begin

out = '1; // '1 is a special literal syntax for a number with all bits set to 1.

// '0, 'x, and 'z are also valid.

// I prefer to assign a default value to 'out' instead of using a

// default case.

case (sel)

4'h0: out = a;

4'h1: out = b;

4'h2: out = c;

4'h3: out = d;

4'h4: out = e;

4'h5: out = f;

4'h6: out = g;

4'h7: out = h;

4'h8: out = i;

endcase

end

endmodule

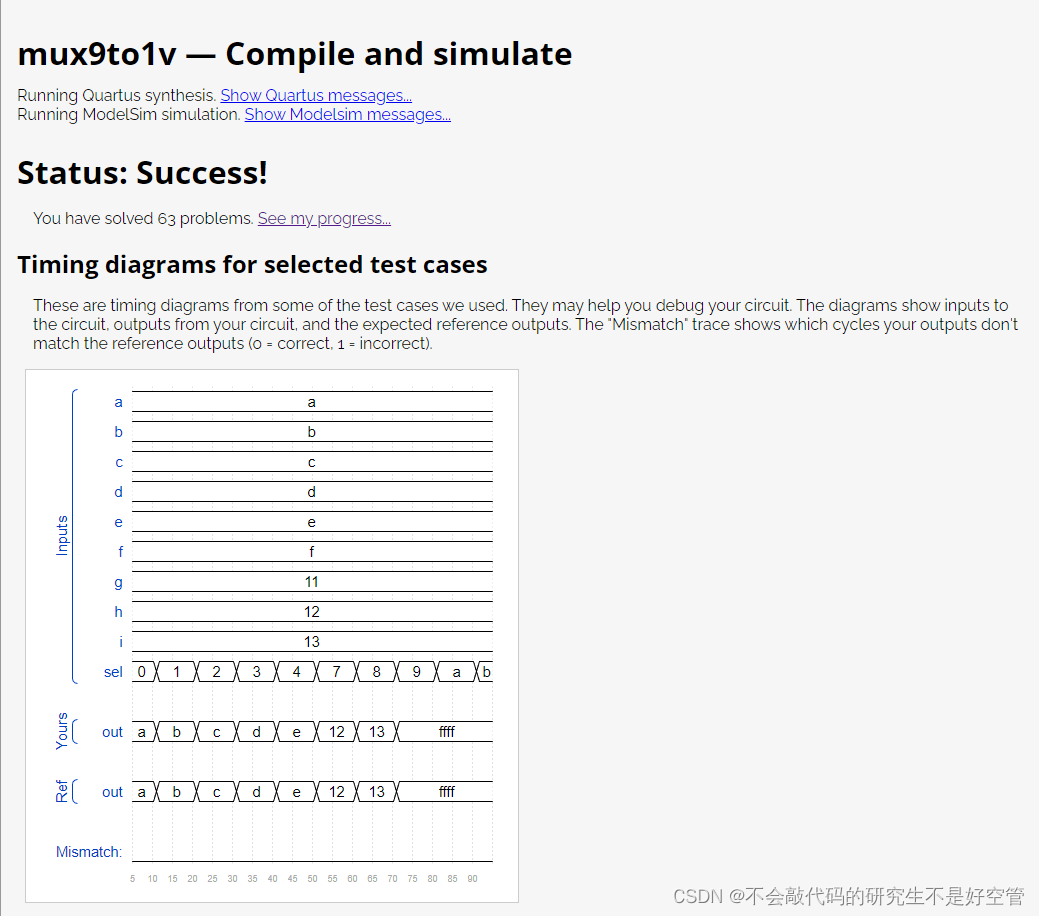

结果

34

34

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?