💥💥💞💞欢迎来到本博客❤️❤️💥💥

🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。

⛳️座右铭:行百里者,半于九十。

📋📋📋本文目录如下:🎁🎁🎁

目录

⛳️赠与读者

👨💻做科研,涉及到一个深在的思想系统,需要科研者逻辑缜密,踏实认真,但是不能只是努力,很多时候借力比努力更重要,然后还要有仰望星空的创新点和启发点。建议读者按目录次序逐一浏览,免得骤然跌入幽暗的迷宫找不到来时的路,它不足为你揭示全部问题的答案,但若能解答你胸中升起的一朵朵疑云,也未尝不会酿成晚霞斑斓的别一番景致,万一它给你带来了一场精神世界的苦雨,那就借机洗刷一下原来存放在那儿的“躺平”上的尘埃吧。

或许,雨过云收,神驰的天地更清朗.......🔎🔎🔎

💥1 概述

模拟下变频的局限性与数字下变频的优点

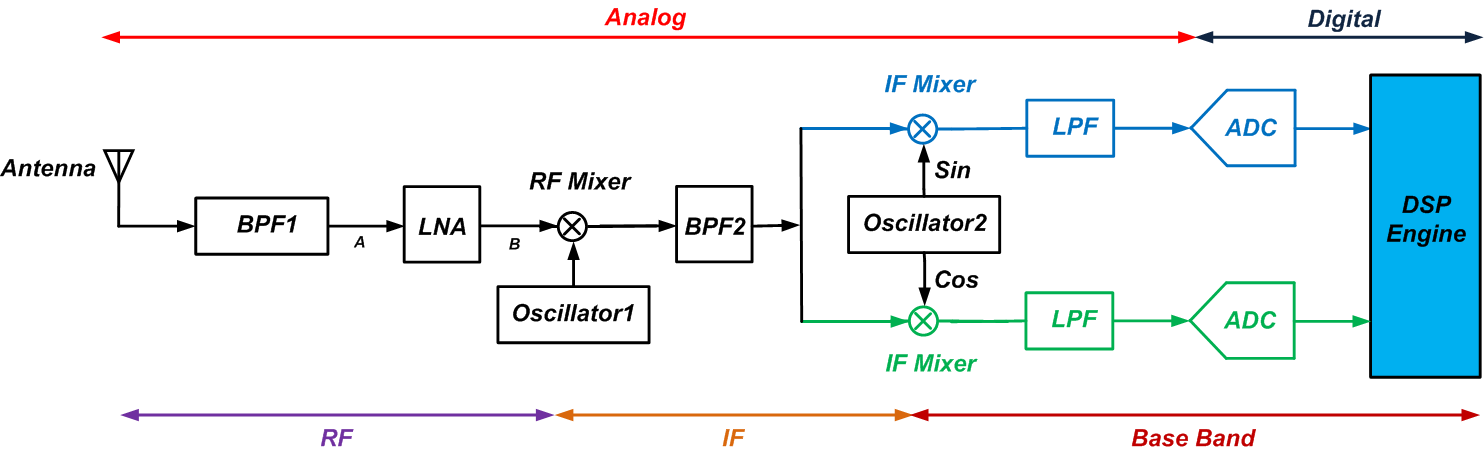

在ADC采样率并不高的时代,通信接收机中的下变频通常由模拟电路完成,即使用正交相参本振信号与中频信号混频,分别得到低频的I、Q分量,经过低通滤波器滤除高频镜频后再用ADC采样并处理。其结构框图如下:

其优点是不需要高采样率的ADC,但缺点也是显而易见的——

- 模拟乘法器参数不匹配,导致输出 镜频抑制比不高,且存在非线性误差;

- 本振时钟源频率不稳定,随电路工作环境变化;除非使用温补晶振等时钟源

- 电路结构复杂,成本高;

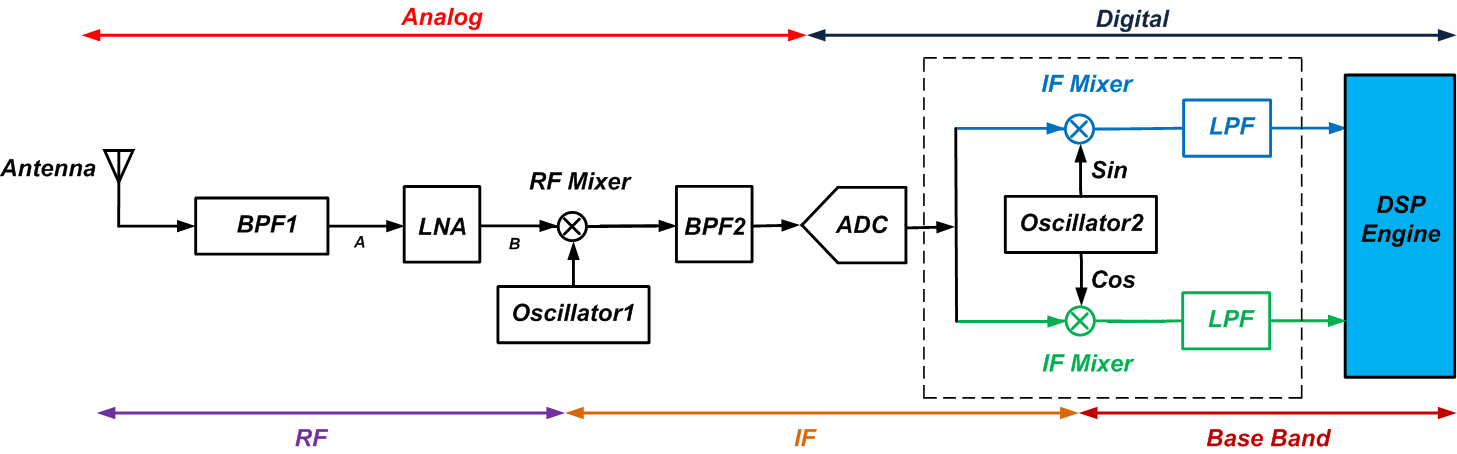

随着技术的发展,高速高精度ADC的诞生使得数字正交采样下变频变得可能。如下图所示:

如图,使用高速ADC直接对滤波后的中频信号进行采样,后在数字域中对中频信号进行正交解调下变频。数字下变频的方法解决了模拟电路参数杂散性的问题,同时更加稳定、精确、低功耗、低成本,还可以简化电路结构。现在这种方式成为了主流。

全部文档见第4部分。

1. 数字下变频(DDC)的基本原理

DDC是一种将高频数字信号(如中频IF)转换为基带信号的数字处理技术,核心目标是通过频谱搬移降低信号频率与采样率,便于后续处理(如滤波、检测)。其核心组成与工作流程如下:

-

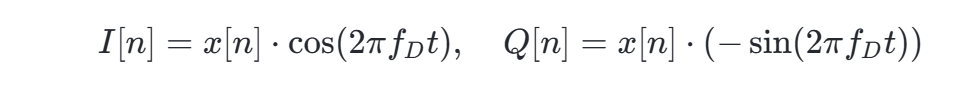

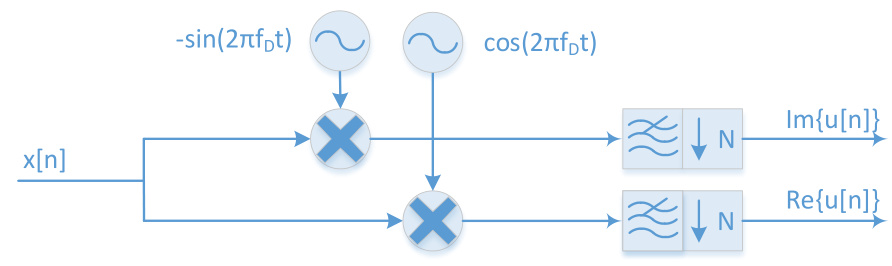

正交混频:输入信号 x[n]与数控振荡器(NCO)生成的正交载波(cos(2πfDt)和 −sin(2πfDt)相乘,产生I(同相)、Q(正交)两路信号:

此步骤将信号中心频率从 fD 搬移至零频附近(基带)。

-

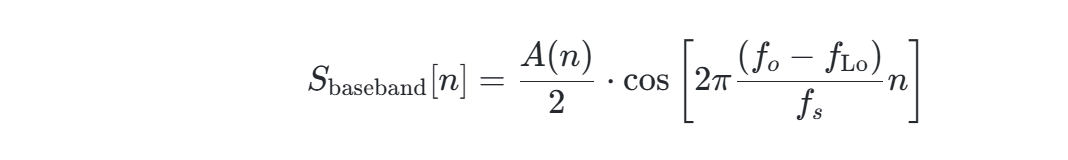

低通滤波(LPF) :滤除混频后的高频分量(和频成分),保留基带信号。滤波后信号为:

其中 fo 为输入中频,fLo为NCO频率(通常 fLo=fo)。

-

抽取(Decimation) :降低采样率以减少数据量,同时避免混叠。通过多级滤波器链(如CIC、HB、FIR)实现。

物理意义:DDC通过数字域操作替代传统模拟混频器,消除模拟本地振荡器的频率漂移、相位噪声和非线性失真问题,提升系统稳定性。

2. DDC在雷达信号处理中的应用场景

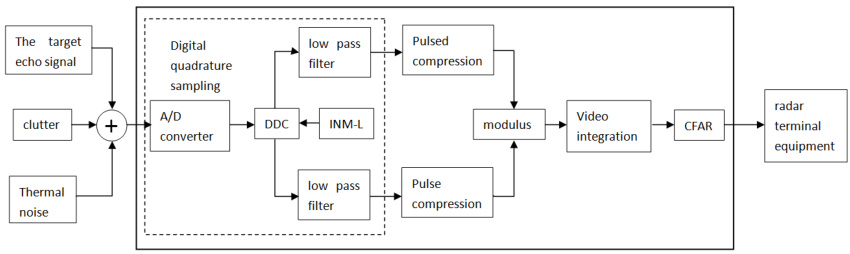

(1) 脉冲压缩雷达(如LFM信号处理)

- 流程:

- 接收回波信号(含目标、杂波、噪声)经ADC采样;

- DDC将中频信号下变频至基带,生成I/Q数据;

- I/Q信号通过匹配滤波器压缩脉宽,提升信噪比(SNR);

- CFAR检测目标并输出。

- 优势:DDC实现精准的IQ解调,保留信号相位信息,为多普勒频移分析提供基础。

(2)数字阵列雷达(DAR)与相参系统

- 多通道同步:DDC集成于数字T/R模块,支持多通道相位同步,提升波束形成精度。

- 性能优势:

- 高集成度:ADRV9009等芯片支持双发双收,减少硬件数量;

- 镜频抑制:有效抑制非线性失真和谐波,改善动态范围。

(3)直接变频接收机

- 简化射频链路,直接从中频下变频至基带,降低成本与体积。

3. DDC关键技术模块设计

(1) 数控振荡器(NCO)

- 功能:生成频率可调的正交载波。

- 实现方式:

- CORDIC算法:通过迭代旋转矢量计算正/余弦值,节省硬件资源;

- 查表法(LUT) :预存波形样本,通过相位累加器索引。

- 关键参数:相位分辨率(48位NCO支持连续跳频)、频率切换速度。

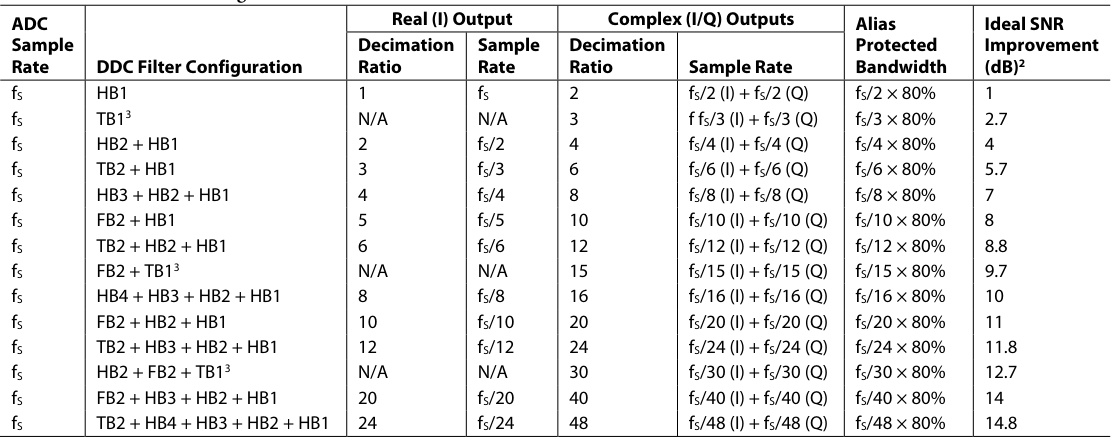

(2)多级滤波器链

-

典型结构:

混频输出 → CIC滤波器(大比例抽取) → CIC补偿FIR(校正通带衰减) → HB滤波器(半带抽取) → FIR(精确整形) -

作用:

- CIC滤波器:实现整数倍抽取,结构简单但通带不平坦;

- HB/FIR滤波器:补偿CIC缺陷,提高阻带抑制比。

(3)数字混频器

- 复数乘法实现频谱搬移,需优化乘法器位宽以减少量化误差。

4. DDC系统设计关键参数

| 参数 | 影响 | 典型值/设计要点 |

|---|---|---|

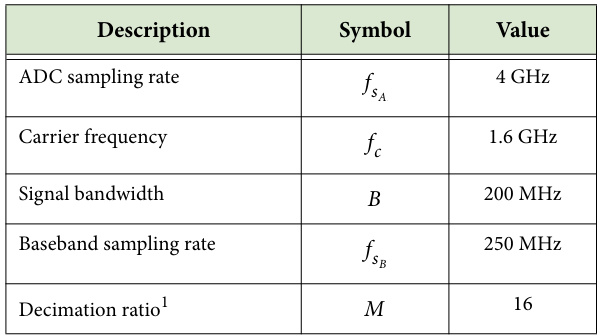

| 采样率(fsfs) | 决定可处理信号最高频率(fs≥2fmaxfs≥2fmax) | 雷达常用:4 GHz(ADC输入)→250 MHz(基带) |

| 降采样比(Decimation Ratio) | 降低数据速率,需避免混叠 | 16倍(例:4 GHz → 250 MHz) |

| 量化位数 | 影响动态范围与信噪比(SNR) | 14-16位(雷达ADC),每增加1位提升≈6 dB SNR |

| NCO分辨率 | 决定频率调谐精度与相位噪声 | 48位相位累加器(ADRV9009) |

设计平衡:高采样率与高位深提升性能,但增加数据存储与计算负担。需根据应用选择(如雷达需高动态范围,通信需高数据率)。

5. DDC性能指标与优化

(1)核心指标

- 信噪比(SNR):

- 理想值:量化位数决定理论上限(e.g., 16位ADC → 98 dB SNR);

- 实际优化:滤波器设计可提升SNR 1–3 dB(如HB1滤波配置)。

- 理想值:量化位数决定理论上限(e.g., 16位ADC → 98 dB SNR);

- 无杂散动态范围(SFDR):

- 受NCO相位噪声影响,添加抖动(Dithering)可改善:

- 5位抖动 → 最优SFDR(实验值113.72 dB)。

- 相位噪声:数字本振无温漂,但有限字长引入误差,需增加NCO位宽。

(2)雷达场景性能验证

- 实验结果:

- 镜频抑制 >40 dB,非线性失真改善30%;

- 目标检测距离提升15%(因SNR改善与杂波抑制)。

6. DDC实现常见问题与解决方案

(1)IQ不平衡问题

- 现象:I/Q两路增益或相位失配,导致镜频泄漏。

- 解决:

- 校准滤波器系数;

- 采用对称FIR结构减少误差。

(2)滤波器链设计挑战

- 通带波动:CIC滤波器引入衰减 → 增加补偿FIR;

- 资源消耗:多级滤波占用FPGA资源 → 复用滤波器核或优化抽取顺序。

(3)NCO相位截断误差

- 影响:引起杂散分量,降低SFDR。

- 优化:相位累加器高位宽(≥32位) + 抖动注入。

(4)系统同步问题

- 多通道相位失锁:采用同一时钟源驱动所有DDC模块,FIR滤波补偿路径延迟。

结论与展望

DDC作为雷达数字化的核心技术,通过正交混频、多级滤波与抽取,实现了高频信号到基带的高精度转换。其在脉冲压缩、数字阵列雷达中显著提升检测性能与系统集成度。未来发展方向包括:

- 片上天线集成:DDC与ADC/RF前端单片化(如RFSoC);

- AI辅助滤波:自适应滤波器优化动态场景响应;

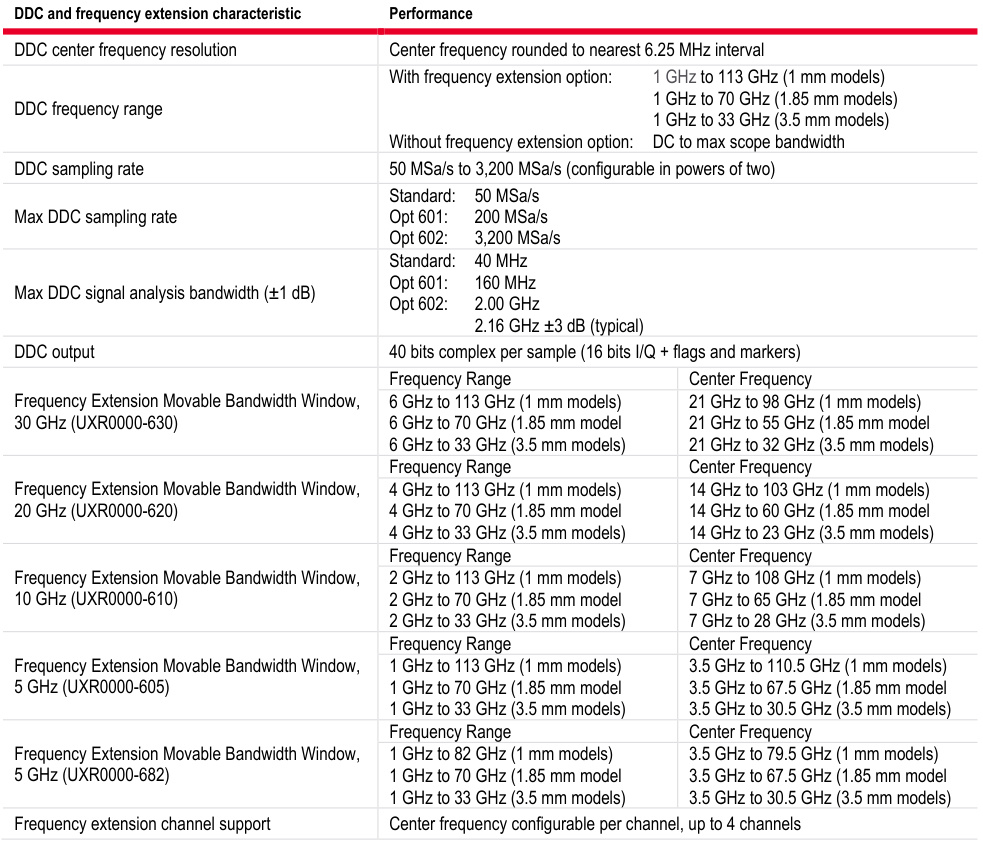

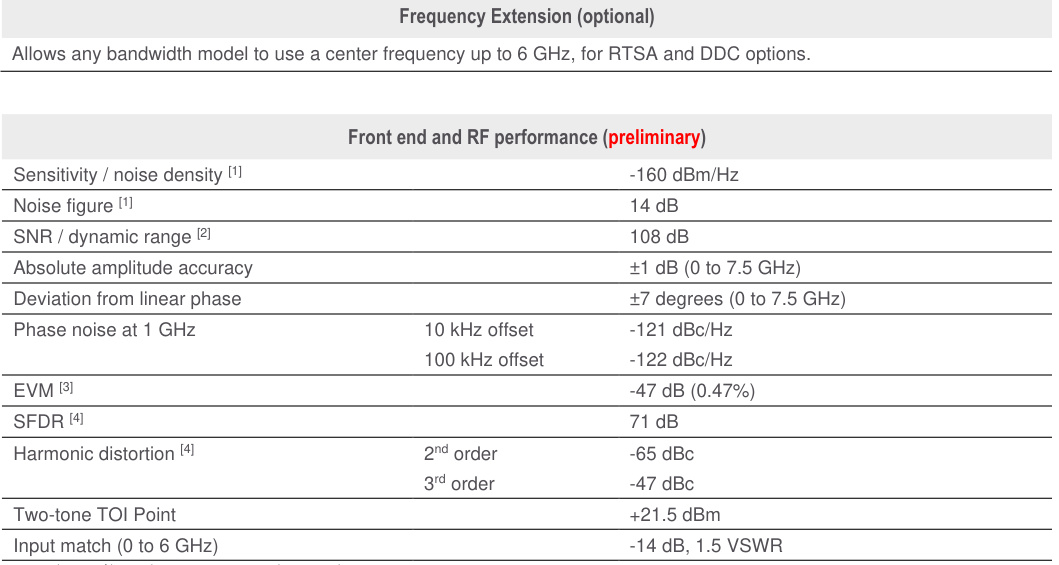

- 太赫兹应用:支持6–113 GHz DDC频段(如Infiniium UXR示波器)。

关键挑战:随着带宽提升(>2 GHz),需解决超高速采样(>10 GSPS)下的功耗与散热问题。

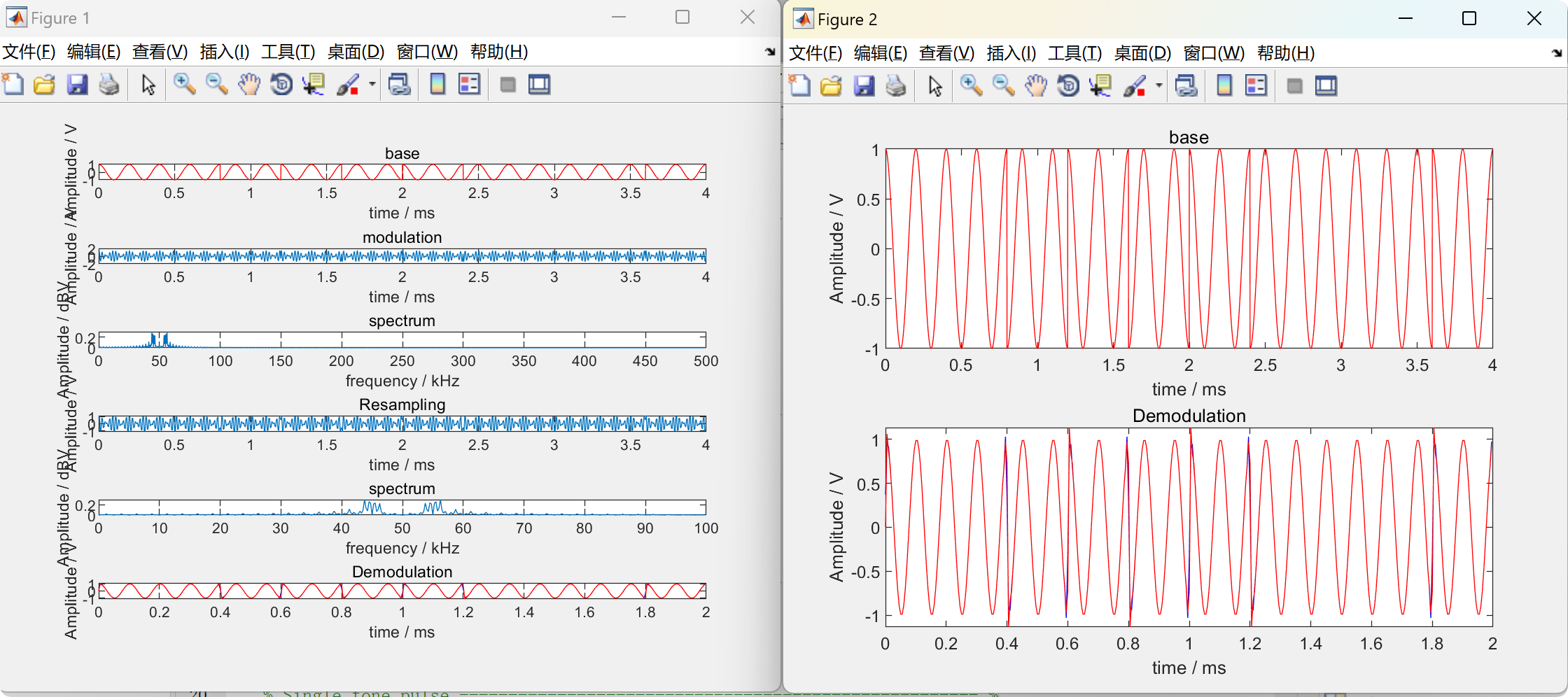

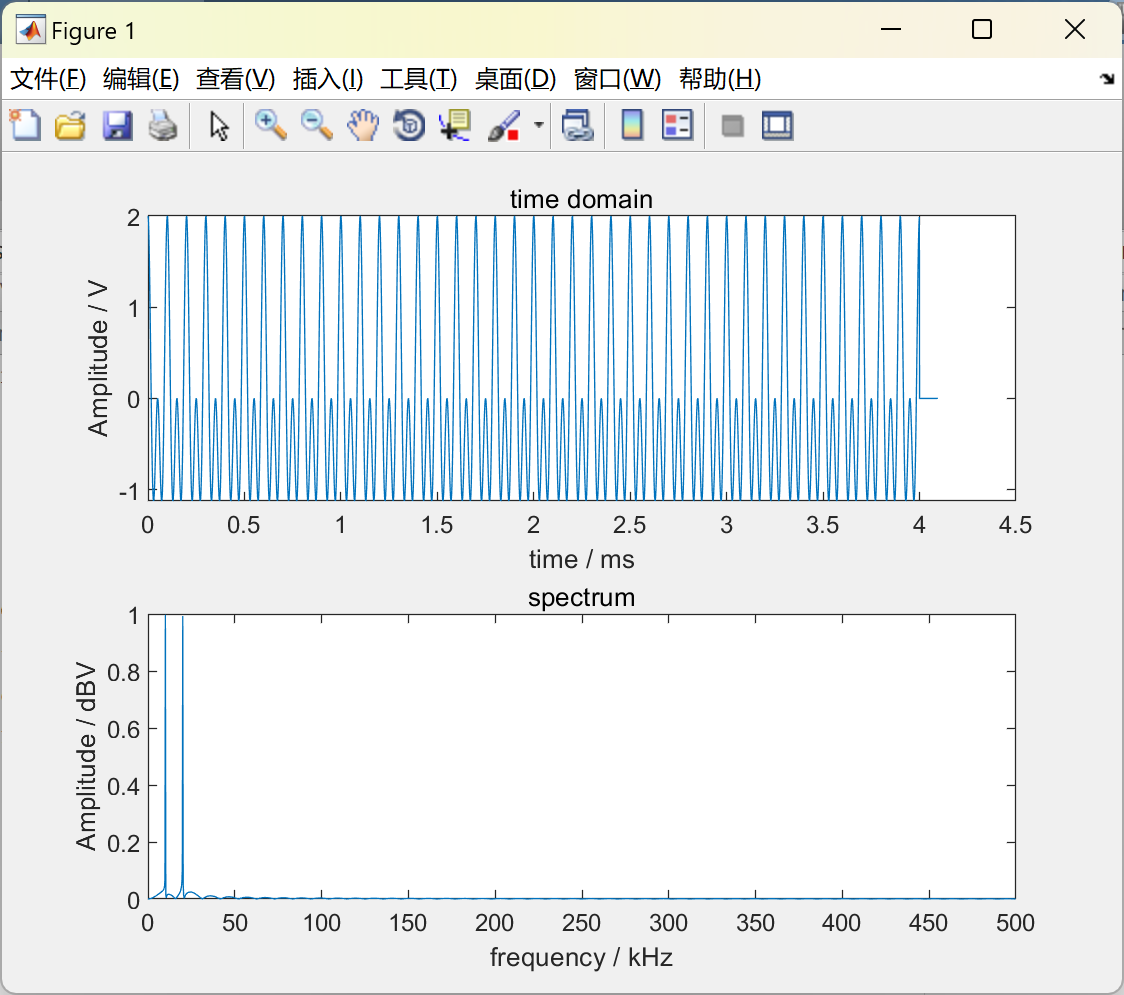

📚2 运行结果

部分代码:

% Time base parameters -------------------------------------------------- %

fs = 1e6; % Sampling frequency: 1Mhz

dt = 1/fs; % Time scale

N = 4000; % Points

tv = 0:dt:(N-1)*dt; % Discrete time vector

fv = (0:N/2-1)*1/dt/N; % Discrete frequency vector

% Modulation ------------------------------------------------------------ %

fb = 5e3; % Base frequency: 5kHz

fc = 50e3; % Carrier frequency: 50kHz

sCCos = cos(2*pi*fc*tv);

scSin = sin(2*pi*fc*tv);

% Single tone ----------------------------------------------------------- %

sBaseQ = cos(2*pi*fb*tv);

sBaseI = sin(2*pi*fb*tv);

🎉3 参考文献

文章中一些内容引自网络,会注明出处或引用为参考文献,难免有未尽之处,如有不妥,请随时联系删除。(文章内容仅供参考,具体效果以运行结果为准)

[1]宋虎,陈建军.一种新的高效数字下变频方法及其FPGA实现[J].雷达与对抗, 2006(2):4.

[2]邱兆坤,马云,陈曾平.DDC在雷达正交接收机中的应用[J].现代雷达, 2004, 26(10):4.

[3]刘培沛,冀会辉,曹嘉辉,等.基于RISC-V的雷达信号处理器设计[C]//第十四届全国DSP应用技术学术会议论文集.2022.

🌈4 Matlab代码、文档下载

资料获取,更多粉丝福利,MATLAB|Simulink|Python资源获取

7394

7394

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?