整体设计

两种设计,一种由PS通过AXI_LITE将数据放入PL端的BRAM中,但后读出。另外一种PS端通过AXI_LITE将数据直接写入到PL端。

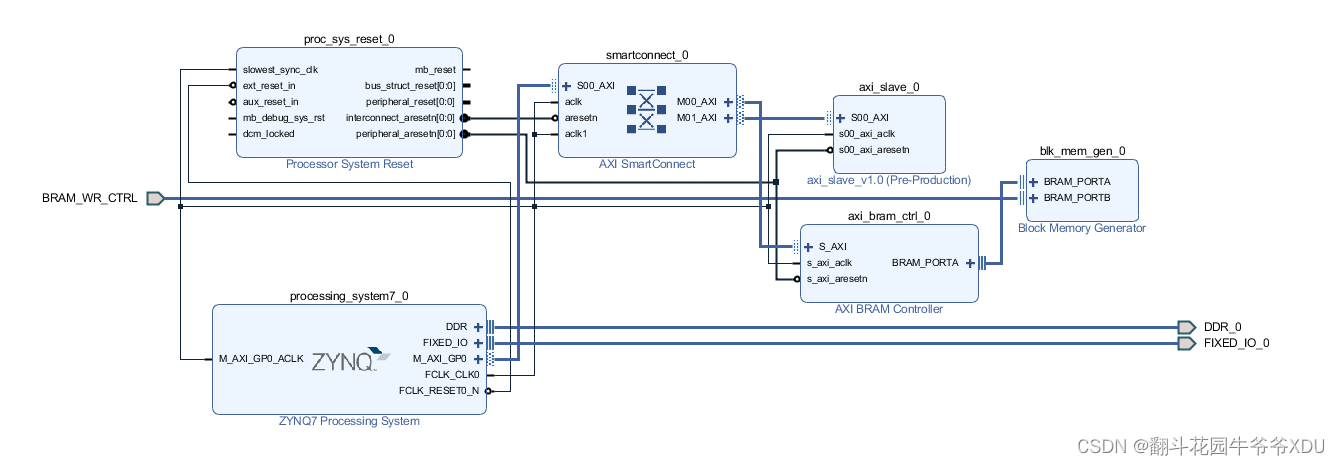

BD设计

注意:

- BRAM Controler 如果设置两个输出端口,A端口是写,B端口是读。如果只设置一个端口,那么这个端口可写可读。

- BRAM的大小配置不了,它的大小随着AXI总线变化而变化。

- 线路一:由PS通过GP口向AXI_SlAVE写数据。

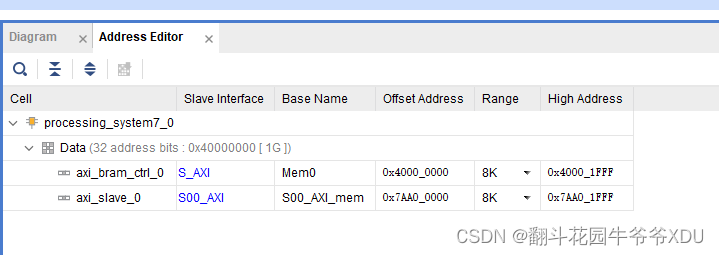

- 线路二:BRAM路线,将BRAM地址空间分为空间一,空间一为PL端的BRAM_WR_CTRL写入数据,PS端通过GP读出,空间二由PS通过GP口写入数据,PL端的BRAM_WR_CTRL读出。

BRAM_WR_CTRL设计

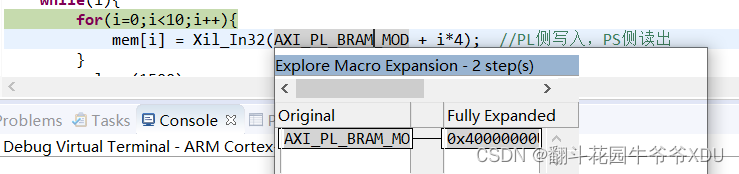

首先PL侧向BRAM模块写入40个32bit的数据,BRAM模块地址是字节地址,此处要计算地址自增,BRAM中地址空间是0-40,这里每一个空间存放的是一个字节,4个字节组成一个数。在PS端读取的时候,使用Xil_In32即可读出

else if(cnt >=100 && cnt < 100 + ((WRITE_DATA_NUM * (DATA_WIDTH/4))))begin

ro_addr <= WRITE_BASE_ADDR + ((cnt - 100)<<2);

ro_wr_data <= cnt - 100;

ro_wr_en <= 4'b1111;

ro_bram_en <= 'd1;

end

写完之后,改成PL读出PS端写入的数据

//PS侧写入地址,PL侧读出

else if(cnt >=100 && cnt < 100 + ((WRITE_DATA_NUM * (DATA_WIDTH/4))))begin

ro_addr <= WRITE_BASE_ADDR + ((cnt - 100)<<2);

ro_wr_data <= cnt - 100;

ro_wr_en <= 4'b1111;

ro_bram_en <= 'd1;

end

总体代码

`timescale 1ns / 1ps

module Bram_Wr_Ctrl # (

parameter WRITE_BASE_ADDR = 0 ,

READ_BASE_ADDR = 40 ,

DATA_WIDTH = 32 ,

WRITE_DATA_NUM = 40 ,

READ_DATA_NUM = 40

)(

input i_clk ,

input i_rst ,

output [31:0] o_addr ,

output [31:0] o_wr_data ,

input [31:0] i_rd_data ,

output o_bram_en ,

output [3:0] o_wr_en

);

reg [31:0] ro_addr ;

reg [31:0] ro_wr_data ;

reg [3:0] ro_wr_en ;

reg ro_bram_en ;

reg [10:0] cnt ;

assign o_addr = ro_addr;

assign o_wr_data = ro_wr_data ;

assign o_bram_en = ro_bram_en;

assign o_wr_en = ro_wr_en;

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)

cnt <= 'd0;

else if(cnt == 1500)

cnt <= 'd0;

else

cnt <= cnt + 1;

end

always @(posedge i_clk or posedge i_rst) begin

if(i_rst)begin

ro_addr <= 'd0;

ro_wr_data <= 'd0;

ro_wr_en <= 4'd0;

ro_bram_en <= 'd0;

end

//PL侧写入地址,PS侧读出

else if(cnt >=100 && cnt < 100 + ((WRITE_DATA_NUM * (DATA_WIDTH/4))))begin

ro_addr <= WRITE_BASE_ADDR + ((cnt - 100)<<2);

ro_wr_data <= cnt - 100;

ro_wr_en <= 4'b1111;

ro_bram_en <= 'd1;

end

//PS侧写入地址,PL侧读出

else if(cnt >= 900 && cnt < 900 + ((READ_DATA_NUM * (DATA_WIDTH/4))))begin

ro_addr <= READ_BASE_ADDR + ((cnt - 900) << 2);

ro_wr_data <= 0;

ro_wr_en <= 4'b0;

ro_bram_en <= 'd1;

end

else begin

ro_addr <= ro_addr;

ro_wr_data <= ro_wr_data;

ro_wr_en <= ro_wr_en;

ro_bram_en <= ro_bram_en;

end

end

endmodule

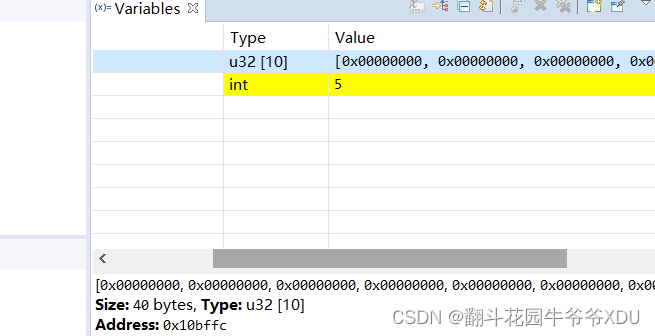

调试记录

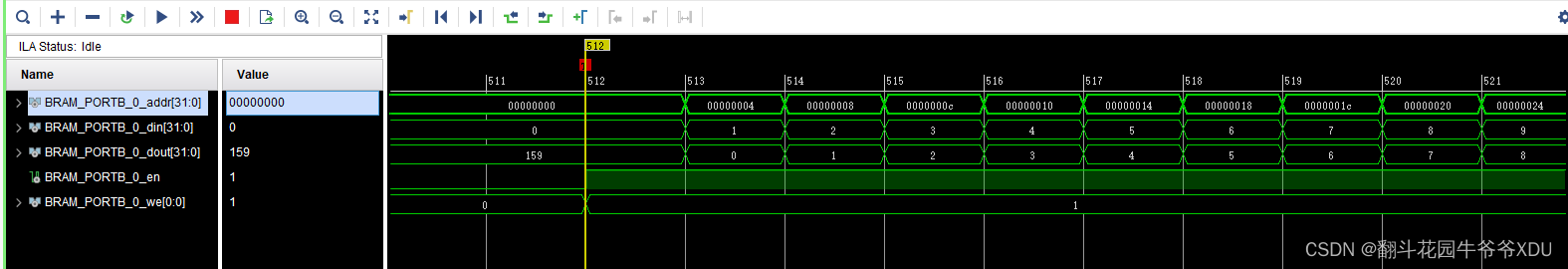

通过ILA抓取可知:PL侧写入BRAM以4Byte对齐地址写入数据Din,数据正确

AXI对应BRAM接口的地址空间,但PS端读出的数据全是0

1514

1514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?