摘要

本文介绍了zynq系统中常用的AXI Lite 协议接口的具体使用方法。简述了AXI协议的特点及结构,说明了其实现的基本机制与时序。此外,结合xilinx官方的AXI Lite设计模板,给出了灵活自定义修改的一般方法。最后通过简要的的读写模块对此自定义AXI Lite 模块进行了PS端对PL端的读写测试。测试结果表明,此自定义模块高效实用,读写准确,本文提供的方法可灵活应用到各类zynq设计架构中去。

1.前言

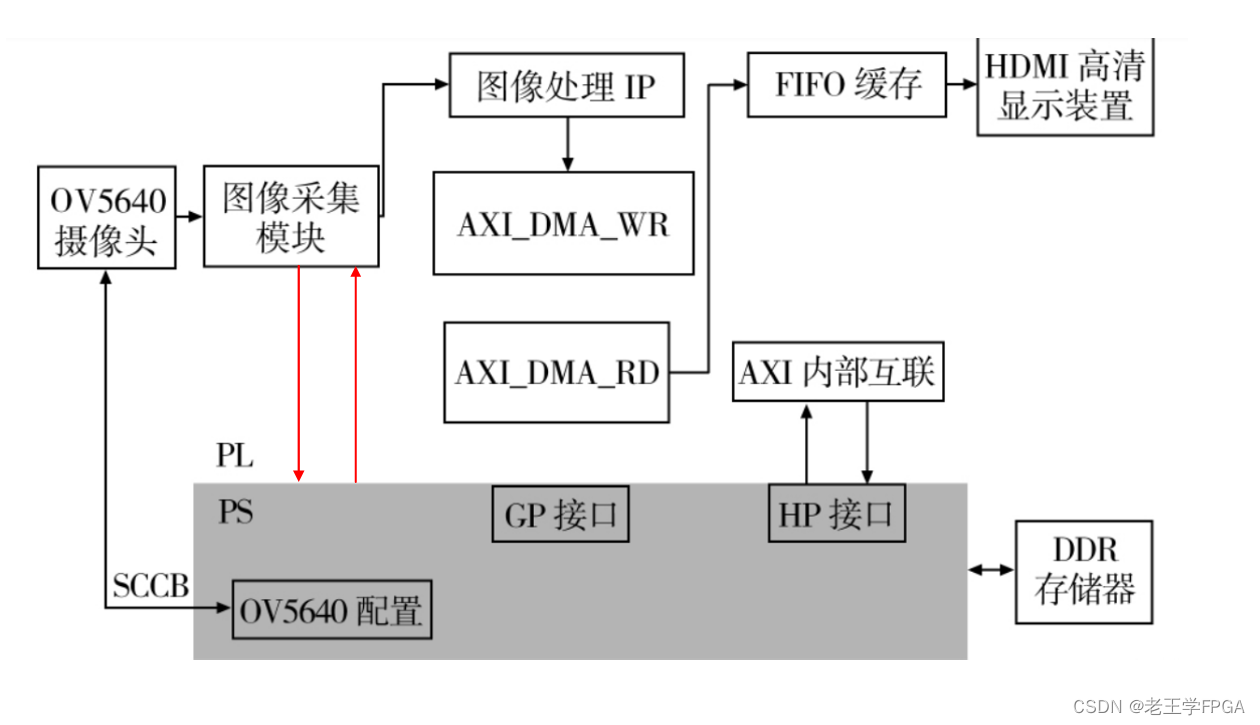

先看一个图像处理工程架构:

图1.1 基于zynq的图像系统架构

图1.1 我们可以看出基于zynq的图像处理往往需要PS系统和PL端的联合工作。他们之间的交互至关重要,往往通过axi接口进行交互,所以xilinx推出了各类具有axi接口的IP供用户调用。比如图中的AXI DMA IP,其自带封装好的axi接口,我们无需编写实现,只要正确配置IP就可以工作。

然而当需要实现PS端读写PL的自定义模块的某些参数,怎么实现呢?

比如,PS控制图像采集模块中的帧频、行频、曝光时间等。这时就需要我们自定义AXI模块,自由的实现PS和PL的读写交互。我们可以自己编写AXI模块,也可以在官方模板中修改。总之这些自定义模块是图像处理中常见的,需要掌握。

2.理论介绍

2.1 特点

AXI 的英文全称是 Advanced eXtensible Interface, 即高级可扩展接口,它是 ARM 公司所提出的 AMBA( Advanced Microcontroller Bus Architecture)协议的一部分。

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、 总线的地址/控制和数据通道是分离的;

2、 支持不对齐的数据传输;

3、支持突发传输, 突发传输过程中只需要首地址;

4、 具有分离的读/写数据通道;

5、 支持显著传输访问和乱序访问;

6、 更加容易进行时序收敛。

AXI4 协议支持以下三种类型的接口:

1、 AXI4: 高性能存储映射接口。

2、 AXI4-Lite:简化版的 AXI4 接口, 用于较少数据量的存储映射通信。

3、 AXI4-Stream: 用于高速数据流传输,非存储映射接口。(直接访问ddr)

AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。 AXI-Lite为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而 AXI-Stream 接口则像 FIFO 一样,数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速 AD、 PCIe、 DMA 接口等需要高速数据传输的场合。

2.2 工作机制

axi协议实现的是master主机与slave从机间的数据读写。其不仅可以实现单对主从模块间的数据通信,此外其还可以基于内存映射机制实现多个主从模块的自由连接,后者就要用到用来实现路由机制的 Axi_SmartConnect IP核。

AXI4和AXI4-Lite 接口由以下5个部分(通道)组成:

1、Read Address Channel

2、Write Address Channel

3、Read Data Channel

4、Write Data Channel

5、Write Response Channel

数据的读写可以在主机与从机之间同时进行,并且数据位数可以调整。AXI4中的限制是最多256个数据传输的突发事务。AXI4-Lite只允许每个事务进行一次数据传输。

本文详细介绍了如何在Zynq系统中使用AXI-Lite协议接口,包括AXI协议的特点、AXILite的工作机制以及在Xilinx Vivado中自定义AXILite模块的方法。通过实例展示了如何修改官方模板并进行读写测试,验证了自定义模块的正确性和实用性。

本文详细介绍了如何在Zynq系统中使用AXI-Lite协议接口,包括AXI协议的特点、AXILite的工作机制以及在Xilinx Vivado中自定义AXILite模块的方法。通过实例展示了如何修改官方模板并进行读写测试,验证了自定义模块的正确性和实用性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

170

170

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?