DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,其中,SDRAM是Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。而DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。

SDRAM在一个 时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。

与SDRAM相比:DDR运用了更先进的同步电路,使指定地址、数据的输送和输出主要步骤既独立执行,又保持与CPU完全同步;DDR使用了DLL(Delay Locked Loop,延时锁定回路提供一个数据滤波信号)技术,当数据有效时,存储控制器可使用这个数据滤波信号来精确定位数据,每16次输出一次,并重新同步来自不同 存储器模块的数据。DDL本质上不需要提高 时钟频率就能加倍提高SDRAM的速度,它允许在时钟脉冲的上升沿和下降沿读出数据,因而其速度是标准SDRAM的两倍。

从外形体积上DDR与SDRAM相比差别并不大,他们具有同样的尺寸和同样的 针脚距离。但DDR为184 针脚,比SDRAM多出了16个针脚,主要包含了新的控制、时钟、电源和接地等信号。DDR内存采用的是支持2.5V电压的SSTL2标准,而不是SDRAM使用的3.3V电压的LVTTL标准。

//https://www.cnblogs.com/xianyufpga/p/13236797.html

DDR 与SDRAM 的不同主要体现在以下几个方面:

1、时钟

SDRAM 的读写采用的是单一的时钟,DDR 的读写采用的是差分时钟,即 CLK 和 CLK#。CLK# 能起到触发时钟校准的作用。由于数据是在 CLK 的上下沿触发的,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确性,这就要求对 CLK 的上下沿间距要有精确的控制。但由于温度、电阻性能的改变等原因,CLK上下沿间距可能发生变化,此时与其反相的 CLK# 就起到了纠正的作用,CLK 上升沿快下降沿慢,CLK# 则是上升沿慢下降沿快。

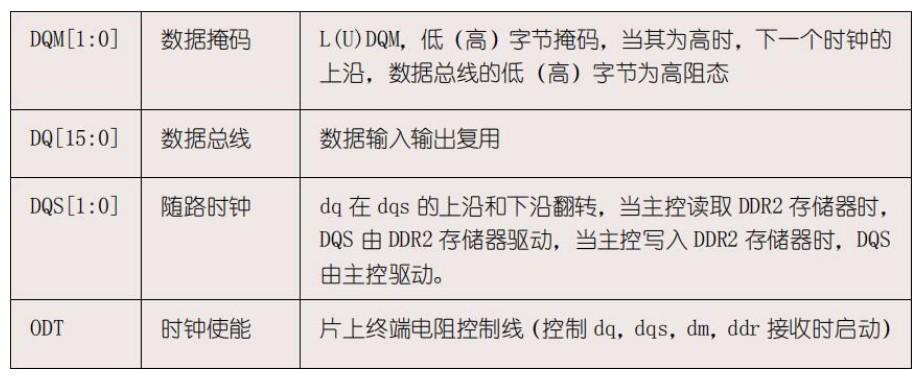

2、数据选取脉冲(|DQS)

DQS 是 DDR SDRAM 中的重要信号,其功能主要是用来在一个时钟周期内准确地区分每个传输周期,并使数据得以准确接收,每一块 DDR SDRAM 芯片都有一个双向的 DQS 信号线。

3、写入延迟

SDRAM 的写入延迟是 0,而 DDR 的写入延迟不再是 0 了,DDR在发出写入命令后,DQS 与写入数据要等待一段时间才会送达。这个周期被称为 DQS 相对于写入命令的延迟时间( tDQSS )。之所以会有这样的延迟,这是因为同步,毕竟在一个时钟周期内进行两次传送需要很高的控制精度,它必须要等接收方做好充分的准备才行。

4、突发长度

在 DDR 中,突发长度只有 2、4、8 三种选择,没有了突发长度 1 和全页式突发。之所以去掉突发长度 1 主要是因为 DDR 预读取位数是 2,L_BANK 一次就存取两倍于芯片位宽的数据,所以芯片至少也要进行两次传输才可以,否则内部多出来的数据很难被处理。之所以去掉全页式突发主要是因为PC内存中很难用得上。

5、延迟锁定回路(DLL )

DDR 有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上这两个时钟应该是同步的,但由于实际物理种种原因,所以导致这两个时钟并不同步,这就需要根据外部时钟动态修正内部时钟延迟来实现内部时钟与外部时钟的同步,为此专门设置了DLL,利用DLL可以使内部时钟与外部时钟保持同步。

DDR和DDR2

DDR2 全称是 Double Data Rate 2 SDRAM,翻译成中文是第二代双倍数据速率同步动态随机存取存储器。它也属于 SDRAM 家族的存储器产品,提供了相较于 DDR 更高的运行效能与更低的电压,是 DDR SDRAM 的后继者,DDR2 和 DDR 一样,也是在时钟信号上升沿与下降沿各传输一次数据,但是最大的区别在于DDR2内存可进行 4bit 预读取。这就意味着 DDR2 拥有两倍于 DDR 的预读系统命令数据的能力,因此 DDR2 具有两倍于DDR的完整的数据传输能力。 DDR2 拥有两倍于 DDR 的预读取系统命令数据的能力(DDR2 4bit预读,DDR 2bit预读)。也就是说,在同样100MHz 的工作频率下,DDR 的实际频率为 200MHz,而 DDR2 则可以达到 400MHz。

DDR2与DDR的不同主要体现在以下几个方面

1、片内驱动调校( OCD, Off Chip Driver )

OCD 的主要用意在于调整 I/O 接口端的电压,来补偿上拉与下拉电阻值。目的是让 DQS 与 DQ 数据信号之间的偏差降低到最小。

2、片内终结( ODT, On Die Termination)

所谓的终结,就是让信号被电路的终端被吸收掉,而不会在电路上形成反射,造成对后面信号的影响。.

3、前置CAS (Post CAS)

为了解决 DDR 内存中指令冲突而设计的功能,它允许 CAS 信号紧随 RAS 发送,相对于以往的DDR等于将CAS前置了,这样地址线可以立刻空出来,便于后面的行有效命令发出,避免造成命令冲突而被迫延后的情况发生。

DDR2 存储单元阵列部分可以说和 DDR、SDRAM基本相同,唯一不同的就是 I/O 输出和输入缓冲区部分了。这部分内容主要包含了差分选取脉冲( DQS )、延迟锁定回路(DLL)和片内终结(ODT )等电路,这和我们前面介绍的是一致的。由于 UDM 和 LDM 只连接到写操作上,所以 DDR2 是支持写入数据屏蔽,并不支持读出数据屏蔽。

SDR SDRAM 的突发长度为1、2、4、8、page

DDR SDRAM 的突发长度为2、4、8 (2bit预读, 2起步)

DDR2 SDRAM 的突发长度为4、8 (4bit预读,4起步)

// https://www.cnblogs.com/xianyufpga/p/13074382.html DDR2教程版本1

// https://blog.csdn.net/Linker00/article/details/98034776 DDR2教程版本2

https://blog.csdn.net/qq_57342311/article/details/128138196 关闭防火墙方法

(1)General Settings

即页面左上角,这部分主要是配置驱动 DDR2 存储器的通用设置。

Device family:设备家族,也就是我们用的是哪个系列的 FPGA 芯片,像我们常用的以 EP4CE 开头都是 CycloneIV E 系列。

Speed grade:FPGA 芯片的速度等级,在芯片的型号名称中可以看到,比如 “EP4CE30F23C8”, 最后一位 8 指的就是速度等级。

PLL reference clock frequency: PLL 参考时钟频率,由于 DDR2 IP 核内部包含了 PLL 模块,因此我们需要给它提供参考时钟,一般由外部晶振或外部 PLL 输出提供。

Memory clock frequency:存储器时钟频率,指的就是 DDR2 存储器的工作频率。

Controller datarate:控制器数据速率,这里有两种选择,一种是Full (全速率),另一种是Half(半速率)。全速率控制器提供的接口时钟频率就是存储器工作时钟频率,半速率控制器提供的接口时钟频率是存储器工作时钟频率的一半。

Local interface clock frequency:本地接口时钟频率,指的是 DDR2 IP 核给用户提供的接口(也就是控制器接口)时钟频率,由存储器时钟频率和控制器数据速率决定。

Local interface width:本地接口宽度,指的是 DDR2 IP 核给用户提供的接口(也就是控制器接口)数据宽度,由存储器数据宽度和控制器数据速率决定。如果控制器速率选择的是 Full,那么本地接口宽度是存储器数据宽度的两倍( DDR2内部在时钟上升沿和下降沿都能吞吐数据)。如果控制器速率选择的是 Half,那么本地接口宽度是存储器数据宽度的4倍,这是由于控制器接口时钟频率降低了一半。

Memoryvendor:存储器生厂商,有Micron、 Samsung、 Hynix, 以及 JEDEC 等。

Memory format:存储器格式,有 Discrete Device (分散设备),Unbuffered DIMM (无缓存DIMM) 和 Registered DIMM (寄存器的DIMM )。

Maximum memory frequency:设置存储器支持的最大频率。

Column address width:定义存储器列地址宽度。

Row address width:定义存储器行地址宽度。

Bank address width:定义存储器 bank 地址宽度。

Output clock pairs from FPGA:指定从 FPGA 驱动到存储器的差分时钟对。当接口有多个设备时,时钟对越多,每个输出的负载就越小。

Chip selects per DIMM:定义接口中每个 DIMM 的片选数。

Total Memory chip selects:设置存储器接口中片选信号数,存储深度决定该参数。可以限制显示本地端二进制编码片选地址的范围。如果范围不能满足设计要求,则可以选择下一个较高的值。但是 ALTMEMPHY 的最高位地址空间不会映射到真正的存储器地址。ALTMEMPHY 使用多个片选信号并用 mem_cs_n 信号校准片选信号。

Precharge address bit:选择用于预充电的地址宽度。

Drive DM pins from FPGA:指定是否用 DM 引脚进行写操作。

Maximum memory frequency for CAS latency (3.0、4.0、 5.0、6.0):每个给定 CAS 延时情况下存储器的最大频率限制,如果输入的值超出了范围则会生成警告信息。

Memory burst length:设置每次传输的读或写数据字的个数。这是IP核内,不是外部的 local_size,full rate下只能是 4,half rate下只能 8 。

Memory burst ordering:控制向写操作期间存储器和 FPGA 之间数据传输的顺序。

Enable the DLL in the memory devices:指定是否在存储器设备中使能DLL,最好选择是,否则 ALMEMPHY 不能确保在关闭在 DLL 时能正常工作。

Memory drive strength setting:控制存储器芯片输出缓存的驱动强度。

Memory on-die termination (ODT) setting:设置存储器 ODT 的值。

Memory CAS latency setting:设置从读命令到从存储器中输出第 1 个数据之间的延时时钟周期数。

Memory Additive CAS latency setting:附加 CAS 延迟设置。

Memory initialization time at power- -up (tINIT):最小存储器初始化时间。

Load mode register command period (tMRD):最小加载模式寄存器命令周期。

Active to precharge time (tRAS):激活到预充电的最小时间。

Active to read/write time (tRCD):激活到读-写的最小时间。

Precharge command peniod (tRP):最小预充电命令周期。

Refresh command interval (tREFI):刷新命令之间的最大间隔。

Auto-refresh command interval (tRFC):最小自刷新命令周期。

Write recovery time (tWR):最小写恢复时间。

Write to read period (tWTR):最小写到读命令延时。

DQ output access time from CK/CK# (tAC):从 CK/CK# 信号到 DQ 输出访问时间。

DQS output access time from CK/CK# (tDQSCK):从 CK/CK# 信号到 DQS 输出访问时间。

DQS-DQ skew for DQS and associated DQ signals (tDQSQ):DQS 到DQ 的最大时间差。

First latching edge of DQS to associated clock edge,+or- (tDQSS):正的 DQS 锁存沿到相应时钟沿的时间。

DQ and DM input hold time relative to DQS (tDH):DQ 和 DM 关于 DQS 的输入保持时间。

DQ and DM input setup time relative to DQS (tDS):DQ 和 DM 关于 DQS 的建立时间。

DQS flling edge hold time from CK (tDSH):从 CK 开始 DQS 下降沿保持时间。

DQS flling edge to CK setup time (tDSS):DQS 下降沿到 CK 建立的时间。

Address and command input hold time (tlH):地址和控制输入保持时间。

Address and command input setup time (tIS):地址和控制输入建立时间。

DQ hold skew factor (tQHS):最大数据保持时间差因子。

Four active window time (tFAW):每个芯片的 4 个活动窗时间。

RAS to RAS delay time (tRRD):每个芯片的激活时间。

Read to precharge time(tRTP):读到预充电的时间。

这个标签我们一般不用改动。可以看出,这里设置的是 ALTEMEMPHY 有关的参数。对于 cyclone IV E 系列芯片,在 PHY Settings 页面下只有两项可以修改:

Address/Command Clock Settings:设置的是时钟相位,调整地址和命令相位可以改进存储器芯片中地址和命令的建立和保持延时,以补偿不同加载带来的传输延时。可以根据 phy_clk 和 write_clk 时钟信号的上升沿和下降沿选择0°、90°、 180° 和 270° 相位偏移。

Auto-Calibration Simulation Options:设置的是自动校准仿真选项,在 Full Calibration(全校准) Quick Calibration (快速校准) 和 Skip Calibration (跳过校准)之间进行选择,仅用于仿真,选择 Full Calibration 时仿真时间较长。

3、Board Settings

这个标签我们一般不用改动。可以看出,这里主要是设置一些板级参数来消除对时序的影响。

Number of Slots/Discrete Devices:需要设置芯片数,可以选择单级或多级配置。

CKCK# slew rate ( Differential):设置 CK/CK# 信号的差分压摆率。

Addr/Command slew rate:设置地址/命令信号的压摆率。

DQS/DQS# slew rate ( Differential ):设置 DQS/DQS# 信号的差分压摆率。

DQ slew rate:设置 DQ 信号的压摆率。

tIS、tH、tDS、tDH:这 4 个量是控制信号和数据总线的建立和保持时间,这意味着建立和保持时间是通过设置压摆率来实现的,当然这 4 个量也可以手动输入更改。

Addr/Commmand eye reduction ( setup ):设置地址和命令信号上由于 ISI 导致的建立过程的眼图缩减。

Addr/Commmand eye reduction ( hold ):设置地址和命令信号.上由于 ISI 导致的保持过程的眼图缩减。

DQ eyereduction:设置 DQ 信号上由于 ISI 导致的眼图缩减。

Delta DQS:设置由于 ISI 导致 DQS 信号到达时间范围的增量。

Max skew within DQS group:设置 DQS 组中 DQ 管脚之间的最大偏移,此值在所有配置(单级或多级,DIMM或器件)中影响 DDR2 接口的读捕捉和写裕量。

Max skew between DQS groups:设置不同 DQS 组中 DQS 信号之间的最大偏移,此值在单级或多级配置中都会影响 DDR2 接口的再同步裕量。

Addr/command to CK skew:设置 CK 信号与地址和命令信号之间的偏移或传输延迟,正值代表长于 CK 信号的地址和命令信号,负值代表短于 CK 信号的地址和命令信号,Quartus II 使用该偏移值来优化地址和命令延迟,从而为 DDR2 接口获得合适的建立和保持裕量。

4、Controller Settings

这个标签我们一般不用改动。可以看出,这里设置的是控制器的参数。我们一般默认选择的是:High Performance Controller II,第二代,性能更好。

Enable Self-Refresh Controls:使能控制器允许用户控制何时让外部存储器工作在自刷新模式。

Enable Auto Power Down:使能控制器在观测到特定数量的空闲时钟周期后自动将外部存储器置于 power-down 模式,如果勾选了该项,在其后的 Auto Power Down Cycles 一栏可以设置空闲时钟的数量。

Enable User Auto-Refresh Controls:使能控制器允许用户发出单一刷新。

Enable Auto-Precharge Control:在控制器顶层使能自动预充电控制,用户可以在读或写突发期间置位 auto-precharge 控制信号来指定控制器在读或写突发末尾是否关闭(也就是auto-precharge )当前打开页。

Enable Reordering:使能控制器重排序命令和数据来达到更高效率。

Starvation limit for each command:指定执行一个等待命令之前能够执行的命令数量,该值的合法范围是1~63。

Local-to-Memory Address Mapping:允许用户控制Avalon接口的地址位与存储器接口的 chip、row、 bank、 column 位的映射方式,如果用户应用程序发出了大于存储器列大小的突发操作,选择 Chip-Row-Bank-Column 可以利用 look-ahead bank management 特性在突发到达列尾时隐藏改变当前打开页所产生的影响。另外一种情况是,如果用户应用程序有几个主机并且用到的是存储器的不同区域,那么选择 Chip-Bank-Row-Column 可以通过高位地址给每个主机分配相应的物理bank,这样就避免了当控制器必须在同一 bank 打开和关闭行的情况下不同主机访问同一bank可能造成的效率下降。

Command Queue Look- Ahead Depth:指定命令队列 look-ahead 深度值来控制 look- ahead bank management 逻辑检验的读或写请求数。

Local Maximum Burst Count:指定突发数来配置控制器从端口能接收的最大 Avalon 突发数,选择 4(100),则外部 local_size 位宽为3。

Enable Configuratio and Status Register Interface:使能控制器的运行时刻配置和状态检索,这样可以添加一个额外的 Avalon-MM 从端口到存储控制器顶层,从而实现存储器时序参数、存储器地址大小和模式寄存器设置以及控制器功能,如果 Eror Detection and Correction Logic 选项被使能,那么该从端口允许用户控制和检索该逻辑的状态。

Enable Error Detection and CorrectionLogic:使能错误检测和纠正(ECC )功能用于单比特和双比特错误纠正。Enable Auto Error Correction 开启此选项后,当 ECC 逻辑检测到单比特错误时,允许控制器执行自动纠错,如果关闭此选项,意味着在特定的时间进行纠错,以实现更高的系统效率。

5、EDA

从该页面中可以看出,如果我们想要仿真 DDR2 IP 核,那么就需要用到 altera_mf 、220model 和 sgate 这三个仿真库。Generate simulation model 选项可以选择是否要生成这3个文件,Generate netlist 选项可以选择是否生成网表文件,如果用户想用第三方EDA综合工具来综合设计的文件,Quartus可以为该综合工具提供网表文件,用来评估时序和资源利用率。这里需要注意的是,并不是所有的第三方EDA工具都支持。我们需要仿真,因此勾选。

6、Summary

总结页面,不用管。

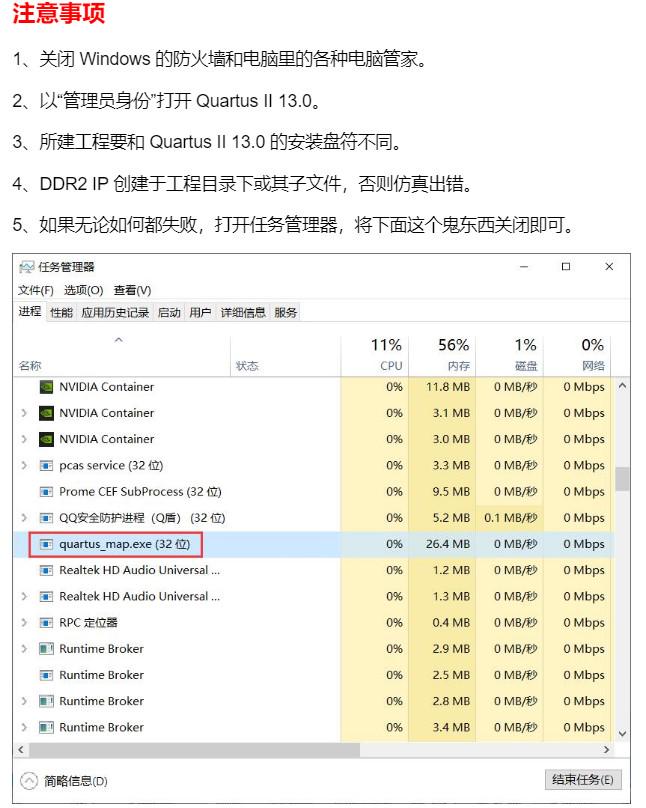

点击 Finish,等待 1 分钟,生成 IP 完毕。如果等了 3 分钟还未生成,表明生成 IP 失败,请删除工程,检查注意事项后重新操作。

4945

4945

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?