目录

一、版本控制

| 版本 | 撰写日期 | 撰写记录 | 字体颜色 |

| V1.0 | 2024.02.07 | 以当前时间点对AURIX 2G 系统定时器(STM)的认识及实践,撰写了此文档,旨在阐述STM模块的实现原理。 | 黑色(有部分红色字体仅为辨识突出) |

二、功能概述

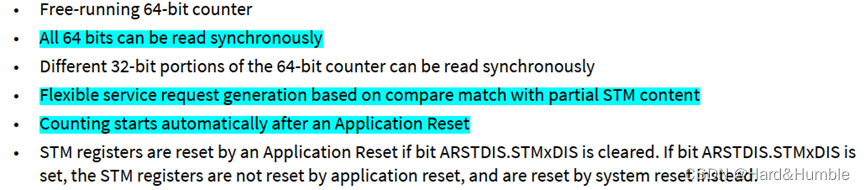

STM模块简单却很重要,是整个软件系统任务能够合理周期调度的基础,主要特点如下图所示:

- 64位的计数空间,计数频率为STM模块的频率。

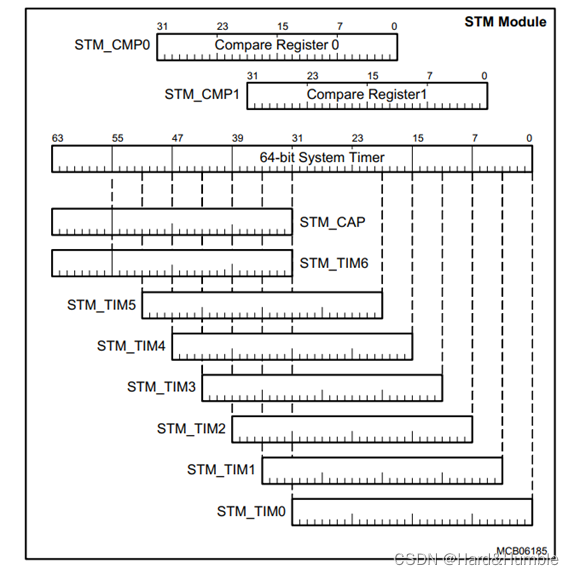

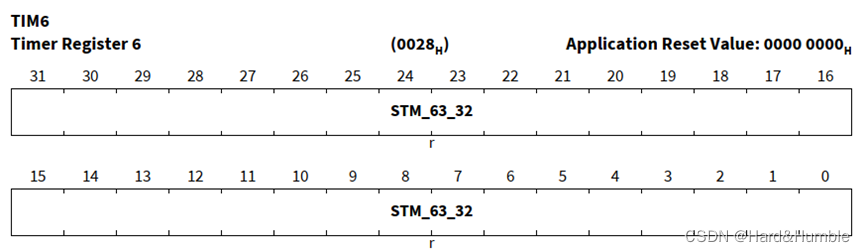

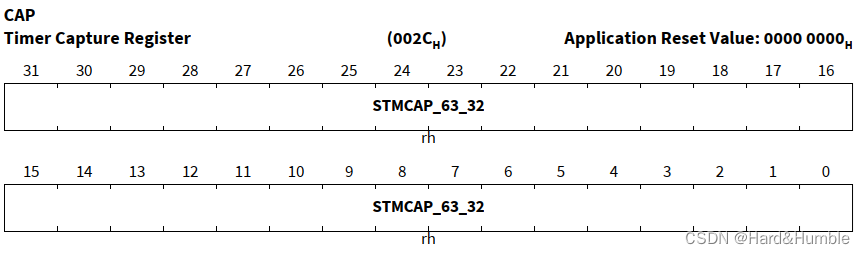

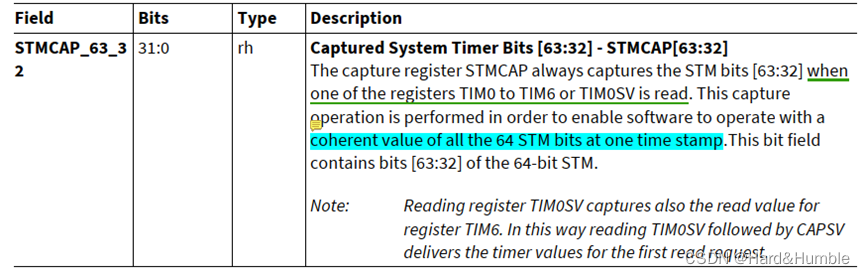

- 由于是64位的空间,不能一次性把全部Counter值读出,分两次读会产生时间差,所以,硬件上给了CAP方案,每一次对计数器的读取时,CAP寄存器就会自动把这次读取时的高位(32:63)Counter值存在CAP寄存器,这样就能够同步读取64位Counter值了。

- 两个比较寄存器可以用来和计数器比较值是否相等,以产生中断服务请求,这个是软件调度的基础,是STM的核心。

- STM的计数器在应用复位后就自动开始计数。

- RCU的ARSTDIS寄存器控制了各个STM模块在Application Reset时的复位与否,0时Application Reset 会导致复位,1时不会导致复位,但此时System Reset会导致STM模块复位。

-

三、主要模块

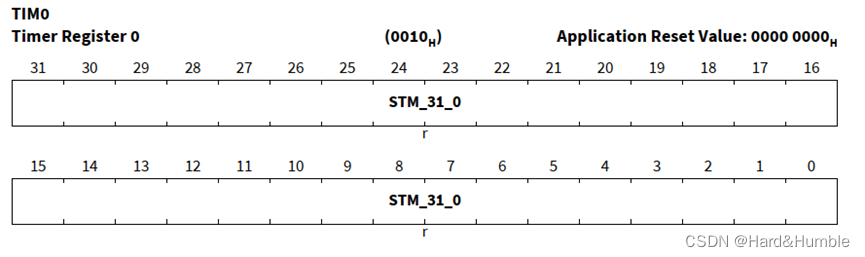

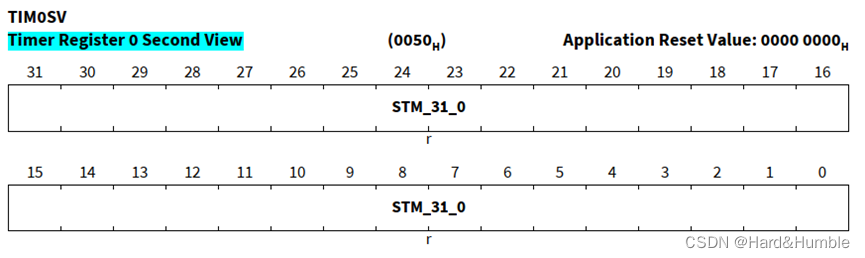

(一)Timer/Capture

任何一个计数器,包括TIM0SV被读的时候,CAP寄存器就会记录读取时的STM的高位值,方便软件读取到一个连续的64位的计数值。

(二)Compare

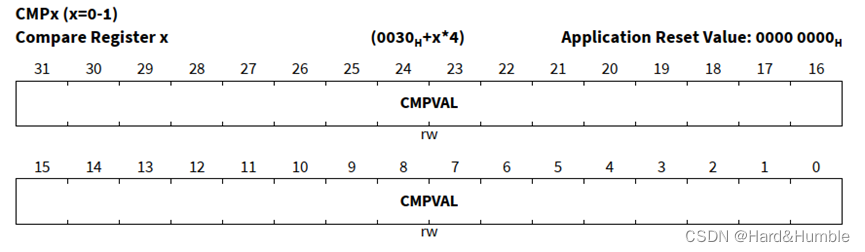

每个STM模块都有两个比较寄存器,CMPx。

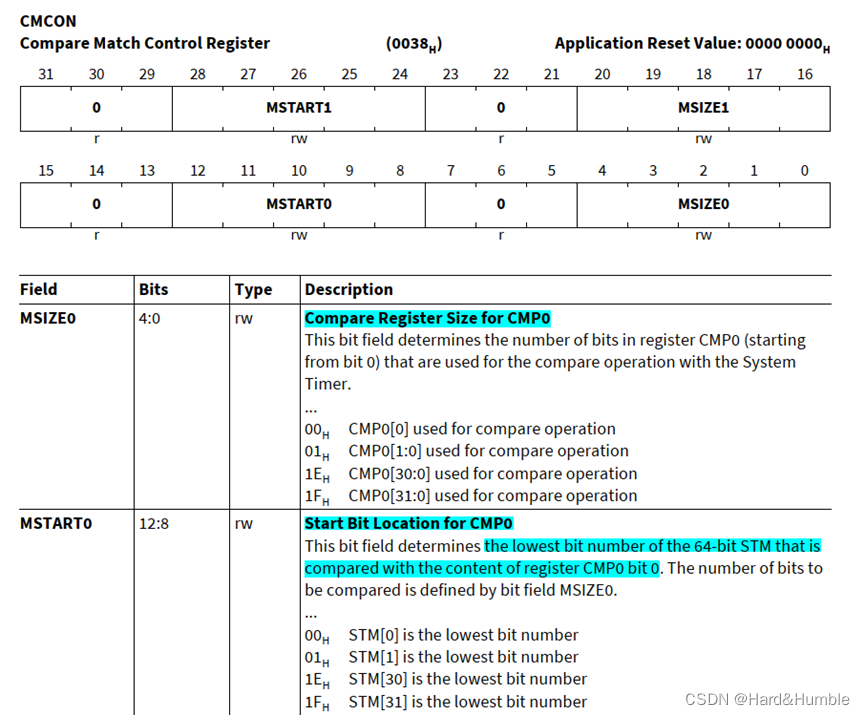

STMx.CMCON寄存器实现了STM的灵活比较:

STMx.CMCON寄存器实现了STM的灵活比较:

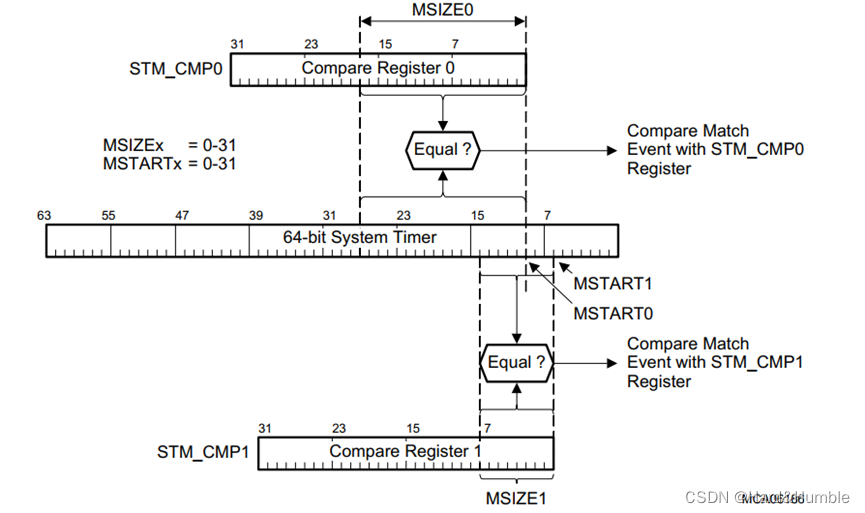

MSIZEx用来配置CMP寄存器的多少位来与计数器比较,MSTARTx用来配置计数器的第几位开始与CMP比较,即比较的最低位是哪一位,一般的用法是计数器的第0位作为最低位,与CMP寄存器的所有位来比较。

![]()

(三)Interrupt

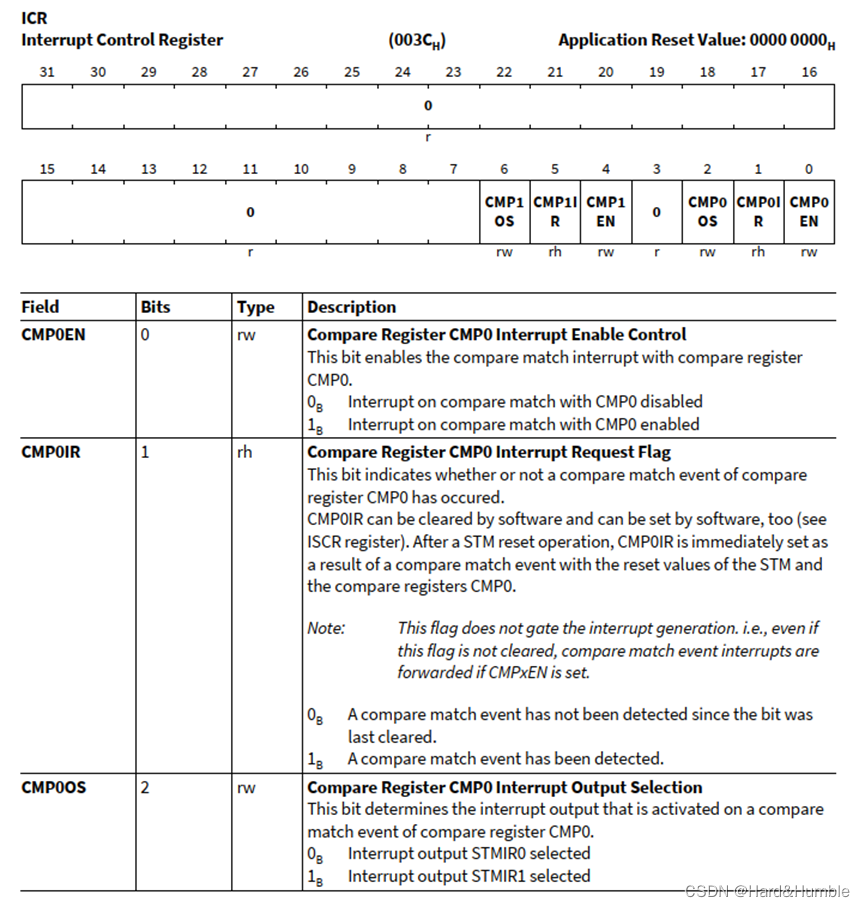

ICR控制了比较器的中断逻辑:

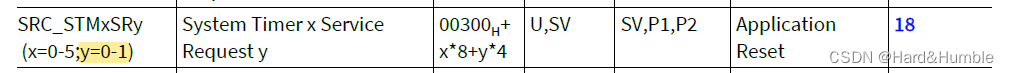

一个用来控制比较相等时的中断是否产生,一个用来表征是否有比较相等事件产生,一个用来控制链接到哪个中断服务请求节点,每个STM有两个SRN(Serve Request Node)。

(四)Interface

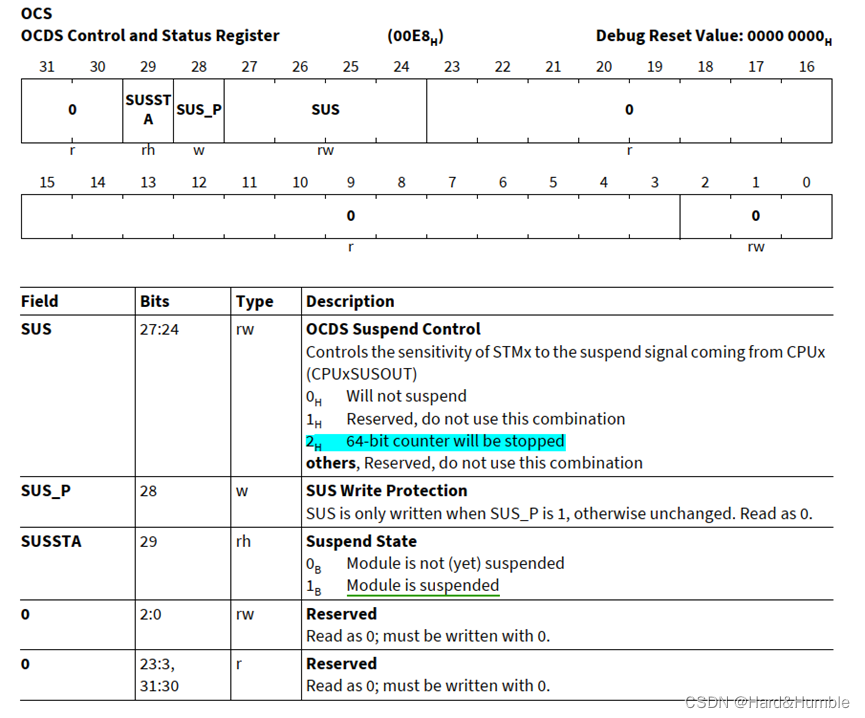

STM模块是独立于CPU的控制的,如果没有相应的同步设置,在CPU被调试工具break时,STM计数器仍会处于一个running的状态,当再次运行的时候就可能导致不同任务的非同步(OS的调度时间基准一般用的STM系统定时),从而导致任务不能正常跑动,这个寄存器的SUS位域就可以设置STM在CPUbreak的时候是否也能够同步停止。

四、参考文档

1.《TC3xx User Manual part1.pdf》

2.《TC39x B-Step User Manual Appendix.pdf》

5240

5240

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?