AXI4的基础知识:FPGA——AXI4总线详解_居安士的博客-CSDN博客

DDR的基础知识:FPGA ——DDR基础概念详解_居安士的博客-CSDN博客

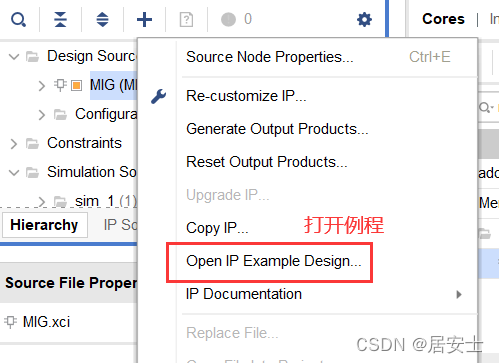

在把AXI4的基础知识和DDR的基础知识掌握了之后,我们可以对基于AXI4总线的DDR进行仿真,我们之间使用DDR的例程:

打开例程:

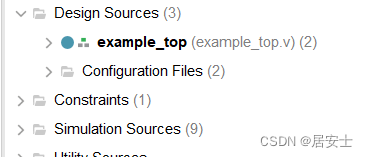

会自动打开一个新的工程:

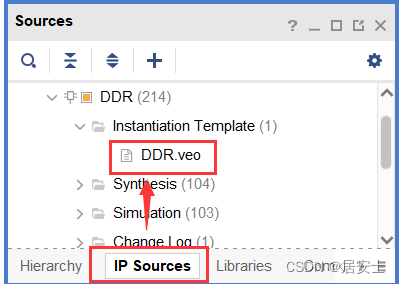

新工程出现之后,我们可以首先 看一下例化文件

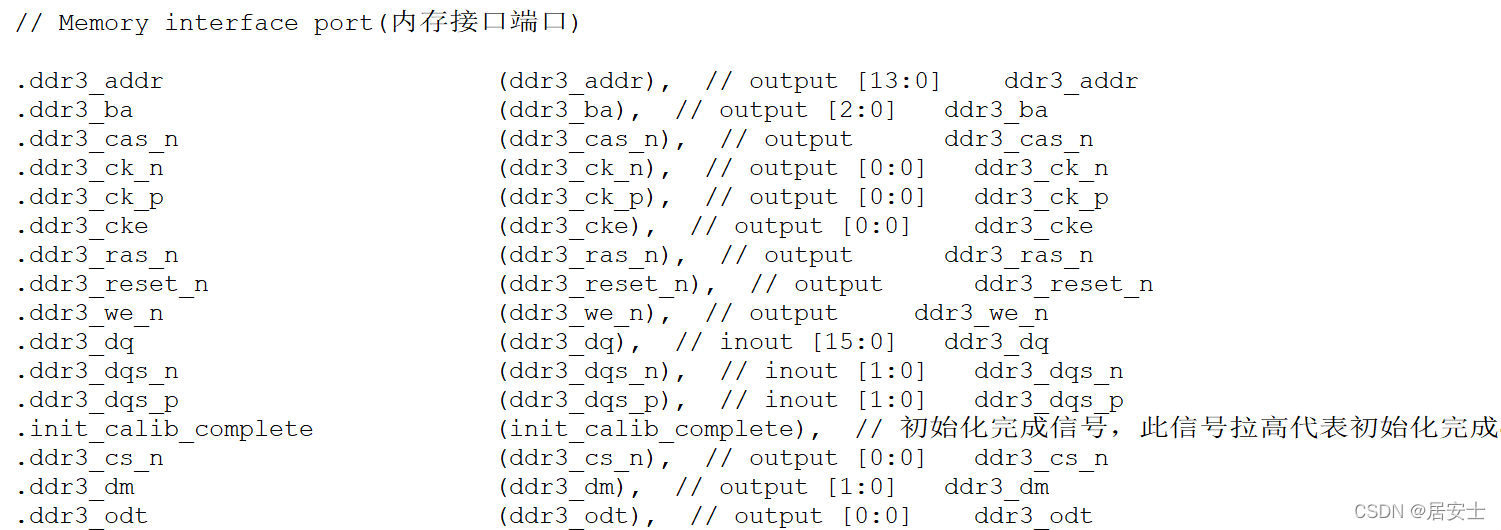

里面有各种接口:

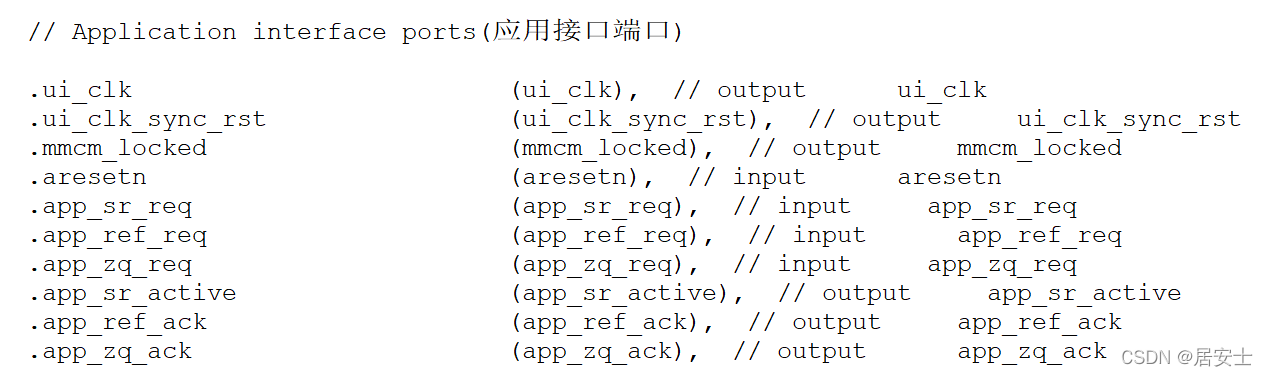

1、MIG核外部接口

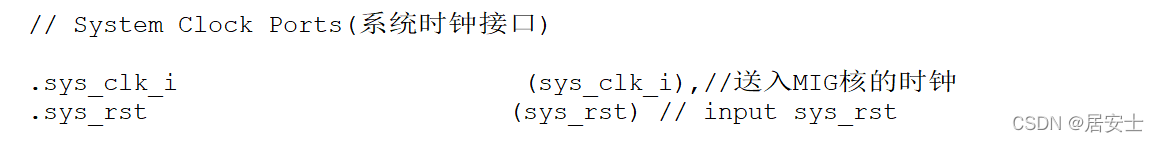

2、MIG核时钟接口

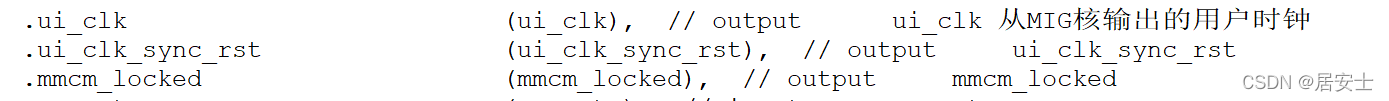

// 用户时钟接口

如果按照我们之前在DDR里面设置的参数,系统时钟接口为200MHZ,用户时钟接口为100MHZ

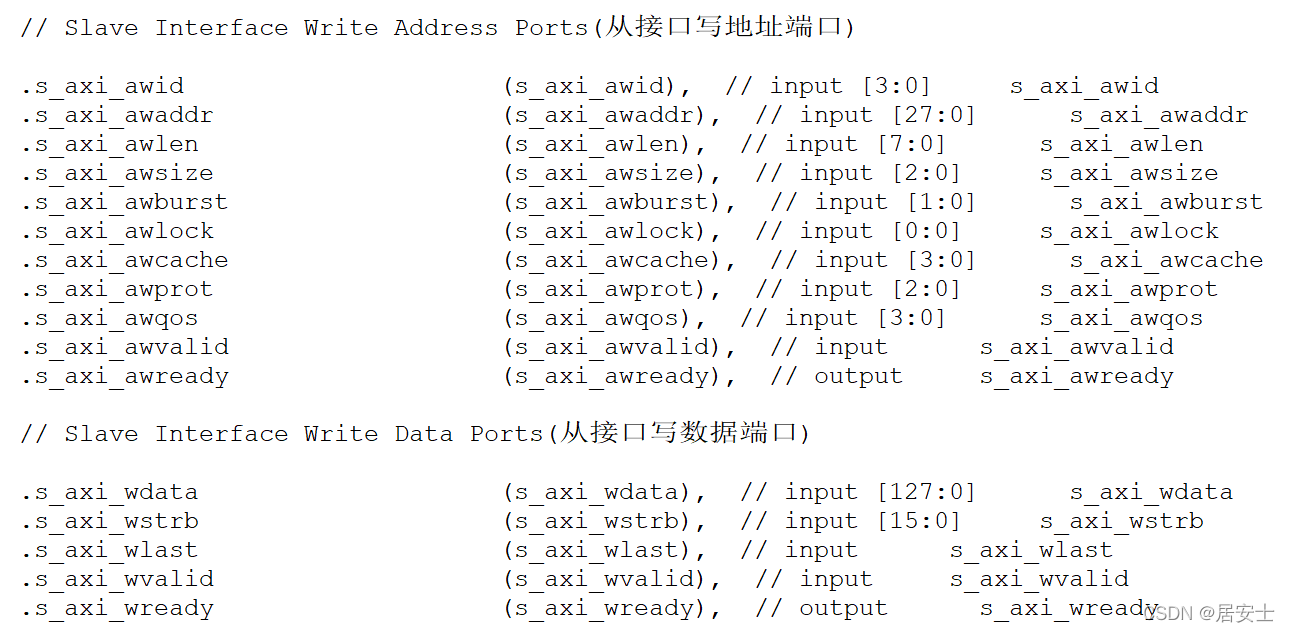

3、MIG核用户接口

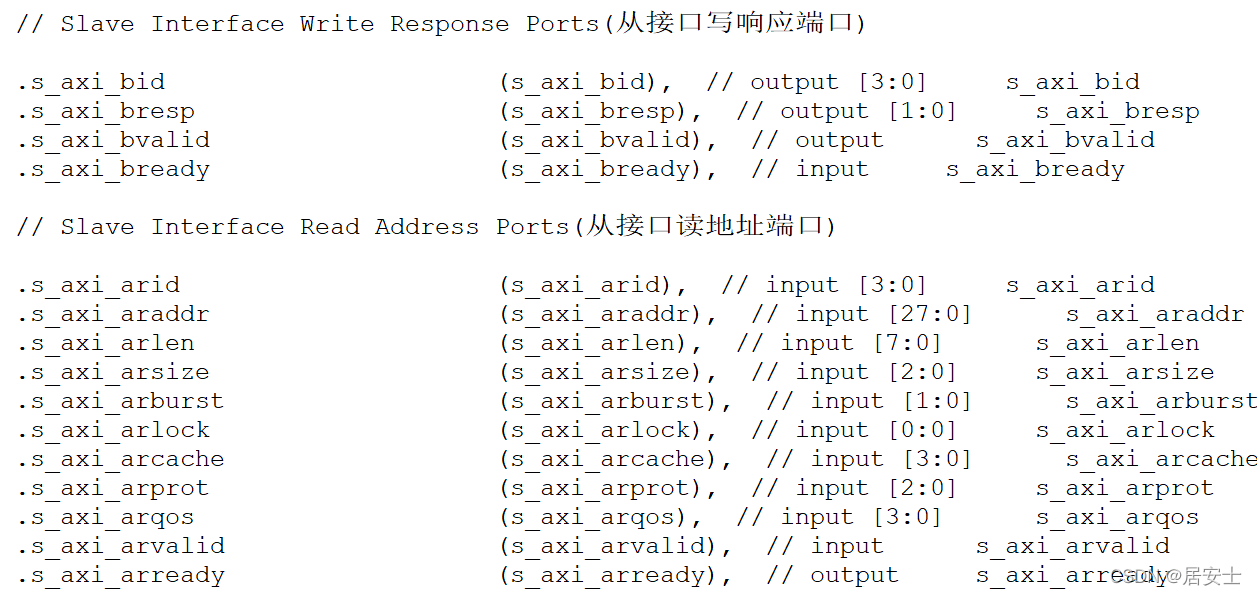

分别对应了写地址,写数据,写响应,读地址,读数据这5个通道

这里特别说明一下len和size这两个信号

len 表示 一次突发的总数据个数 突发长度=awlen+1

size 表示 突发传输中每个传输通道的大小(每个数据的大小) 总线位宽=2^size Betyes

比如我要突发3个位宽为128的数据,3就是len+1,size就是4 2^4=16 16*8=128bit

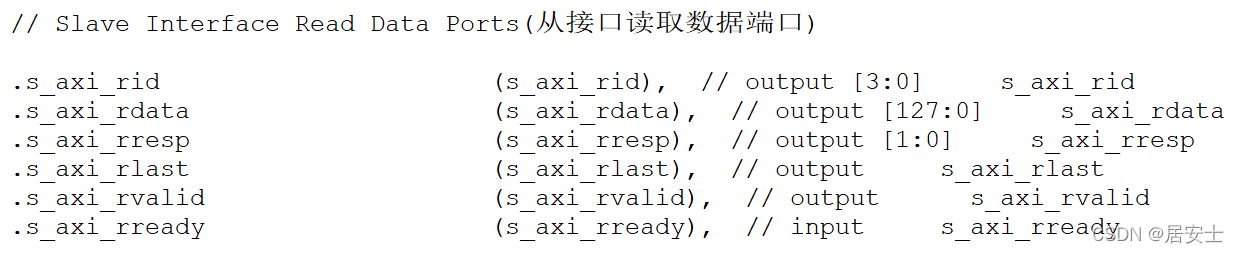

从上面这个图看,len=4时,突发的数据长度约是len=2时的2倍,但是他们都是128位的

接下来,我们直接运行DDR的例程:

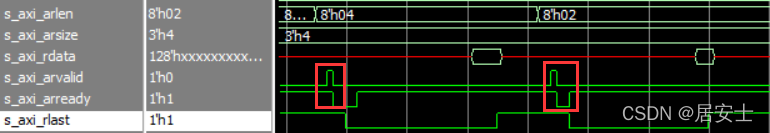

写操作:先写地址,再写数据,再发送写应答

写地址(aw)的vaild和ready都为高时地址有效,此处为28’h0000000

写数据(w)的vaild和ready都为高时数据有效,此处为128’h5a5aa5a…

写数据完成后,发送写应答bvaild,bready

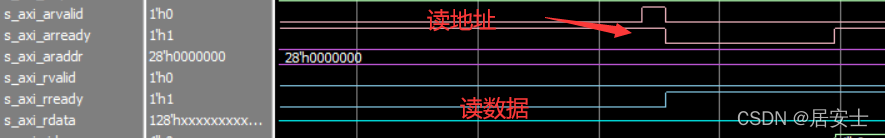

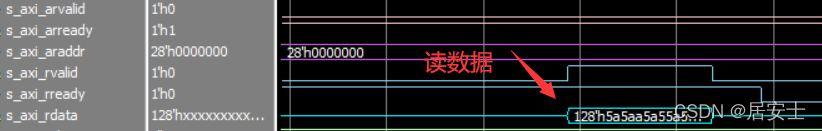

读操作:先读地址,再读数据

读地址(ar)的vaild和ready都为高时地址有效,此处为28’h0000000

读数据(r)的vaild和ready都为高时数据有效,此处为128’h5a5aa5a…

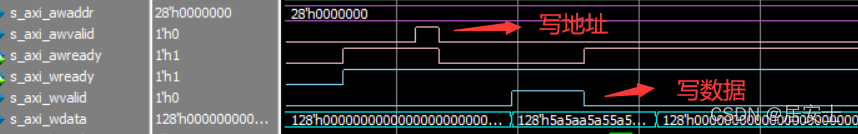

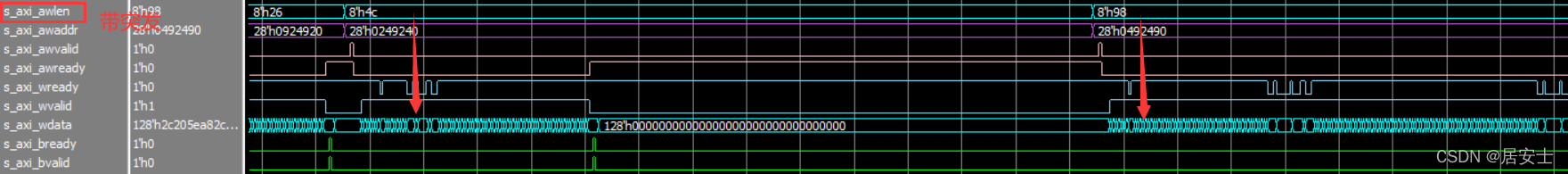

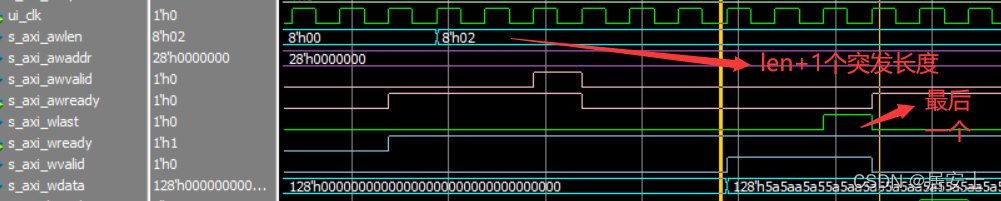

带突发长度的写操作:

给定突发长度和首地址,MIG会自己往后写突发长度的地址

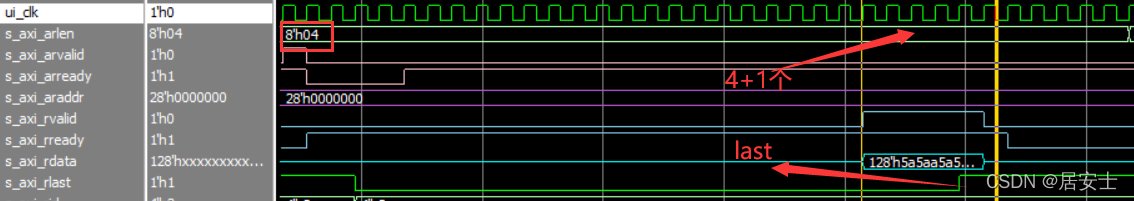

突发长度=len+1,ui_clk一共len+1个周期,完成最后一次突发时last信号拉高

如上图,从wdata有数据开始到last信号一共3个ui_clk周期 ,相当于写了4个 128’h5a5aa5a…

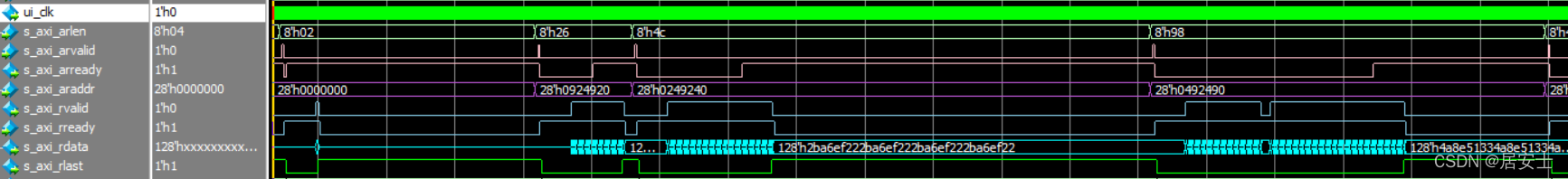

带突发长度的读操作:

突发长度=len+1,ui_clk一共len+1个周期,完成最后一次突发时last信号拉高

如上图,从rdata有数据开始到last信号一共5个ui_clk周期,相当于读了5个 128’h5a5aa5a…

本文详细介绍了FPGA中AXI4总线的基础知识和DDR的基础概念,包括MIG核的外部接口、时钟接口和用户接口。通过实例展示了如何进行基于AXI4的DDR仿真,包括写操作、读操作以及带突发长度的操作。讲解了awlen、size等关键信号的作用,并通过具体例子解释了突发传输的过程。

本文详细介绍了FPGA中AXI4总线的基础知识和DDR的基础概念,包括MIG核的外部接口、时钟接口和用户接口。通过实例展示了如何进行基于AXI4的DDR仿真,包括写操作、读操作以及带突发长度的操作。讲解了awlen、size等关键信号的作用,并通过具体例子解释了突发传输的过程。

2560

2560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?