眼看着到了秋招,做了一些公司的笔试题,发现基本都考了数电的各种触发器,我忘得一干二净还相互混淆,今天就来把这些触发器一起汇总了!

ps:发现软件开发的八股文很多,硬件开发的八股文很少,只能靠自己总结了,FPGA八股文会持续更新,直到我找到工作!

目录

触发器的输入输出

触发器:一种具有记忆功能,能够存储0和1这样的数字信息的电路,是构成时序逻辑电路的基本逻辑器件

触发器的输出端状态:0或者1

触发器输出端收到有效激励信号的时候:状态可以翻转0→1、1→0

若输入激励信号不是有效信号:触发器输出状态保持不变(存储记忆功能)

触发器的分类

根据逻辑功能划分:

RS触发器:置0置1触发器

JK触发器:置0置1及翻转触发器

D触发器:跟随触发器

T触发器:翻转触发器

根据内部结构划分:(结构越来越复杂,抗干扰能力提高)

基本触发器

同步触发器(带有时钟控制的触发器)

主从触发器

边沿触发器

基本RS触发器

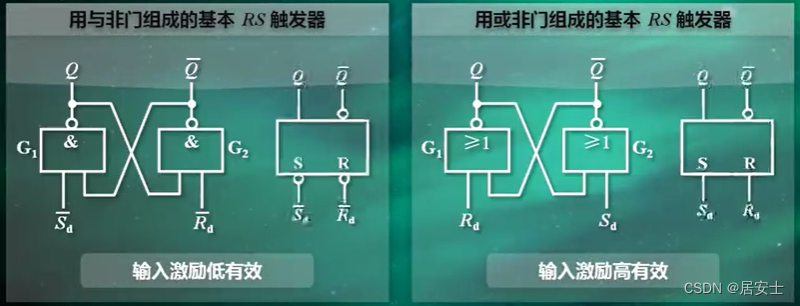

RS触发器有两种结构:

不同之处在于输入S和D是高电平有效还是低电平有效

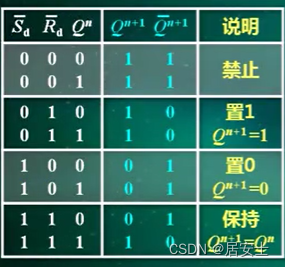

S(set)置1 ,R(reset)置0,输出Q为1和0,上图所对应的真值表如下:

次态Q与现态Q,S,R都有关

当S和R值不同:激励信号有效,输出置1或者置0

当S和R都没输入:保持当前Q值

当S和R都有效:禁止

同步触发器—RS触发器

当clk=0,输入激励被封锁,输出状态保持不变

当clk=1,电路正常工作,完成RS触发器功能

同步D触发器

当clk=0,输入激励被封锁,输出状态保持不变

当clk=1,电路正常工作,完成D触发器功能

次态Q和D为同一个值(跟随器)

同步JK触发器

当clk=0,输入激励被封锁,输出状态保持不变

当clk=1,电路正常工作,完成JK触发器功能

J和K都无激励:保持功能

J和K不同:根据有效的激励置1或0

J和K都有激励:次态会“翻转”成现态相反的数

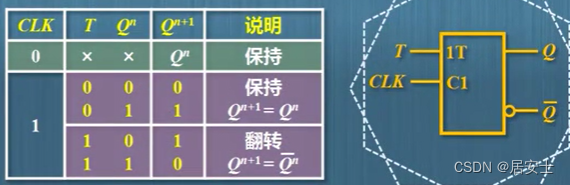

同步T触发器

当clk=0,输入激励被封锁,输出状态保持不变

当clk=1,电路正常工作,完成T触发器功能

T激励无效:保持当前状态

T激励有效:次态是现态翻转后的结果

1391

1391

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?