日常·唠嗑

最近用到XO3器件,XO1跟XO2还没用到,所以这里先不写。

一、MachXO3 CPLD简介

MachXO3™器件系列是一种超低密度器件支持最先进的可编程家庭桥接和I/O扩展。它有突破I/O密度和每个I/O的最低成本。设备I / O功能对最新行业有综合支持标准I / O。MachXO3L/LF系列的低功率,即时启动,非易失性pld有五种密度器件范围从640到9400个查找表。在除了基于lut的低成本可编程逻辑这些设备的特点是内嵌块RAM (EBR),分布式RAM,锁相环,预先设计的源同步I/O支持,高级配置支持,包括双启动常用的功能和加固版本功能,如SPI控制器,I2C控制器和定时器/计数器。MachXO3LF设备也支持User闪存(UFM)。这些特性允许设备要在低成本、高产量中使用应用如消费电子,计算机还有存储,无线通信,工业控制和汽车系统。

MachXO3L/LF器件设计在65 nm上非易失性低功耗过程。该设备架构有几个特征,例如可编程的低摆动差分I/O和能够关闭I/O银行,片上锁相环和动态振荡器。这些特性有助于管理导致静态和动态功耗低所有家庭成员的静电。MachXO3L/LF设备有两个版本C和E两种速度等级:-5和-6,其中-6为最快的。C器件有一个内部线性电压支持外部VCC电源电压的稳压器电压为3.3 V或2.5 V。E器件只接受1.2 V作为外部VCC供电电压。除了电源电压C和E都是正常的彼此兼容。

MachXO3L/LF可编程逻辑器件的范围很广先进的无卤包装,从节省空间2.5 × 2.5 mm的WLCSP至19 × 19 mmcaBGA。MachXO3L/LF设备支持密度在同一个包内迁移。表1.1显示了LUT密度,包和I/O选项,以及其他关键参数。MachXO3L/LF设备提供了增强的I/O特性如驱动强度控制,转速控制,PCI兼容性,总线锁存器,上拉电阻,下拉电阻,开漏输出和热套筒。上拉,下拉和总线看守功能在“每个引脚”的基础上是可控的。内置用户可编程内部振荡器MachXO3L /低频设备。时钟输出振荡器可以被计时器/计数器分开使用作为LED控制等功能的时钟输入,键盘扫描器和类似的状态机。MachXO3L/LF设备还提供灵活的,来自片上的可靠和安全配置

NVCM / Flash。这些设备也可以配置自己从外部SPI Flash或配置外部主机通过JTAG测试访问端口或通过I2C端口。此外,MachXO3L /低频设备支持双启动能力(使用外部闪存)和远程字段升级(TransFR)能力。Lattice提供了多种设计工具使用复杂的设计来有效地实现MachXO3L/LF系列设备。受欢迎的逻辑合成工具为的合成库提供支持MachXO3L /低频。利用格型设计工具进行合成工具输出以及用户指定的首选项和限制放置和路线的设计MachXO3L /低频设备。这些工具提取时间从路由和反向注释到设计中时间验证。Lattice提供了许多预先设计的IP (Intellectual属性)LatticeCORE™模块,包括一个数字免费授权的参考设计,优化适用于MachXO3L/LF PLD系列。通过使用这些可配置的软核IP核作为标准化块,用户可以自由地专注于独特的方面他们的设计,提高了他们的生产力。

二、缩略语

| Acronym | Definition | Chinese |

|---|---|---|

| AES | Advanced Encryption Standard | 高级加密标准 |

| BGA | Ball Grid Array | 球栅阵列(封装,具体百度) |

| caBGA | ChipArray Ball Grill Array | 封装,具体百度 |

| csfBGA | Chip Scale Flip-Chip Ball Grid Array | 封装,具体百度 |

| CE | Clock Enable | 时钟使能 |

| CLK | System clock | 系统时钟 |

| CMOS | Complementary Metal Oxide Semiconductor | 互补金属氧化物半导体(由N沟道-MOS-场效应管和P沟道-MOS-场效应管构成) |

| DDR | Double Data Rate | 双倍数据速率 |

| EBR | Embedded Block RAM | 嵌入块RAM |

| ECDSA | Elliptic Curve Digital Signature Algorithm | 椭圆曲线数字签名算法 |

| ECLK | Edge Clock | 边缘的时钟 |

| ESB | Embedded Security Block | 嵌入式安全块 |

| FCIN | Fast Carry In | 快速执行 |

| FCO | Fast Carry Out | 快速执行 |

| I2C | Inter-Integrated Circuit | |

| IP | Intellectual Property | |

| I/O | Input/Output | |

| JTAG | Joint Test Action Group | |

| LED | Light-emitting Diode | 发光二极管 |

| LSR | Local Set/Reset | 本地设置/重置 |

| LUT | Look-Up Table | 查找表 |

| LVCMOS | Low-Voltage CMOS | 低压CMOS |

| LVDS | Low-Voltage Differential Signaling | 低压差分信号 |

| LVPECL | Low-Voltage Positive/Pseudo Emitter-Coupled Logic | 低压正/伪发射极耦合逻辑(简单来说就是一种电平标准,自己百度) |

| LVTTL | Low Voltage Transistor to Transistor Logic | 低电压晶体管对晶体管逻辑 |

| MIPI | Mobile Industry Processor Interface | 移动工业处理器接口 |

| MLVDS | Multipoint Low-Voltage Differential Signaling | 多点低压差分信令 |

| NVCM | Non Volatile Configuration Memory | 不挥发配置内存 |

| PCI | Peripheral Component Interconnect | 外围组件互连 |

| PCLK | Primary Clock | 主时钟 |

| PDPR | Pseudo Dual Port RAM | 伪双端口RAM |

| PFU | Programmable Functional Unit | 可编程功能单位 |

| PIC | Programmable Interface Controllers | 可编程接口控制器 |

| PIO | Programmed Input/Output | 程序输入/输出 |

| PLD | Programmable Logic Device | 可编程逻辑器件 |

| PLL | Phase Locked Loop | 锁相环 |

| RAM | Random Access Memory | |

| ROM | Read-only Memory | |

| SDR | Single Data Rate | |

| SHA | Secure Hash Algorithm | |

| SPI | Serial Peripheral Interface | 串行外围接口 |

| SPR | Single Port Random Access Memory | |

| SRAM | Static Random Access Memory | |

| TransFR™ | Transparent Field Reconfiguration | |

| UFM | User Flash Memory | |

| WLCSP | Wafer Level Chip Scale Package |

三、器件资源

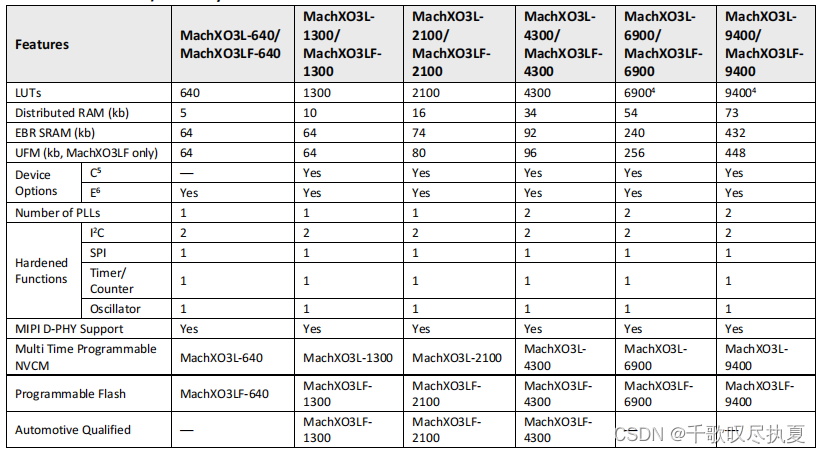

MachXO3L/LF Family Selection Guide

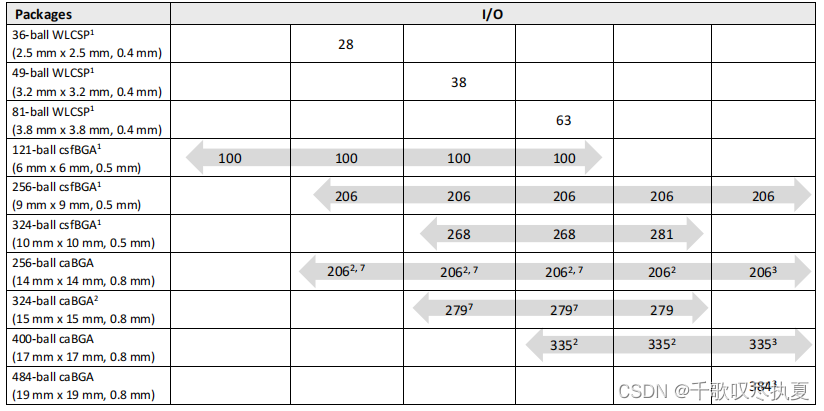

四、XO3 系列封装&PIN

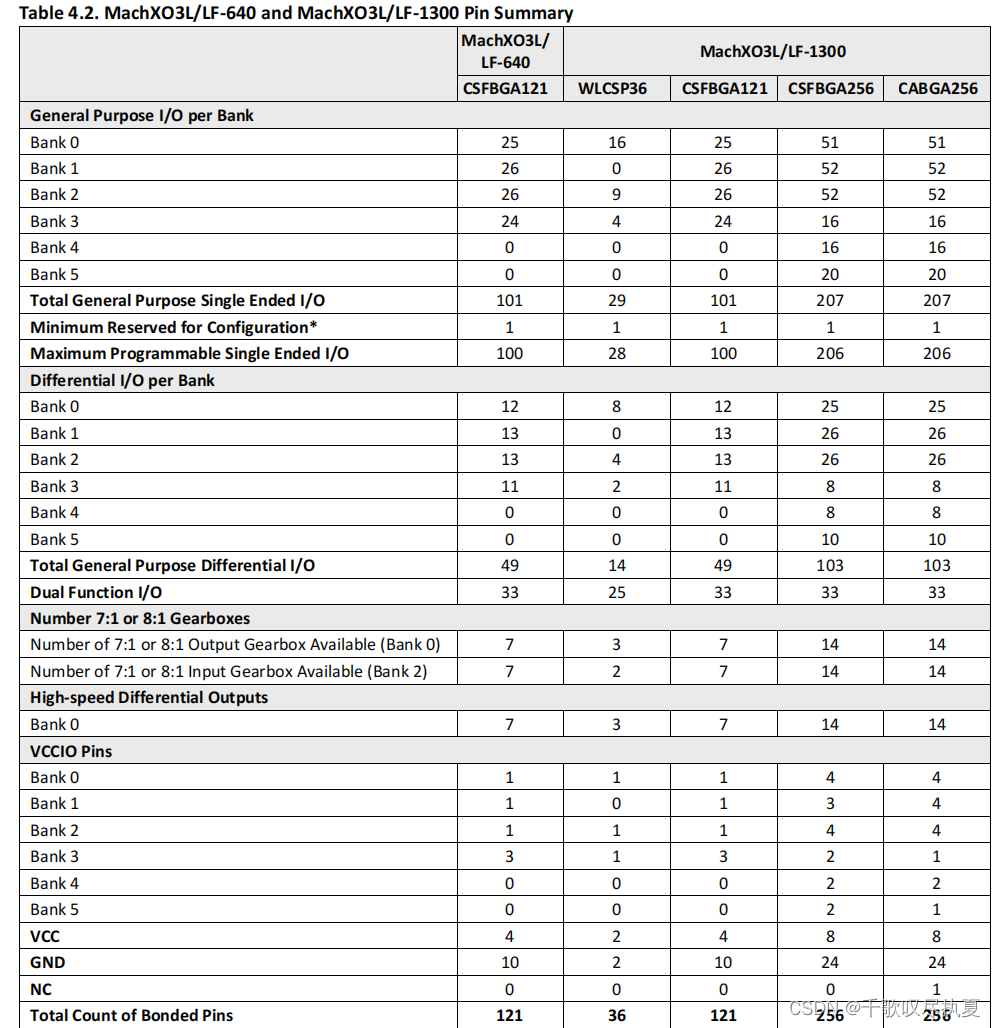

MachXO3L/LF-640 and MachXO3L/LF-1300 Pin Summary

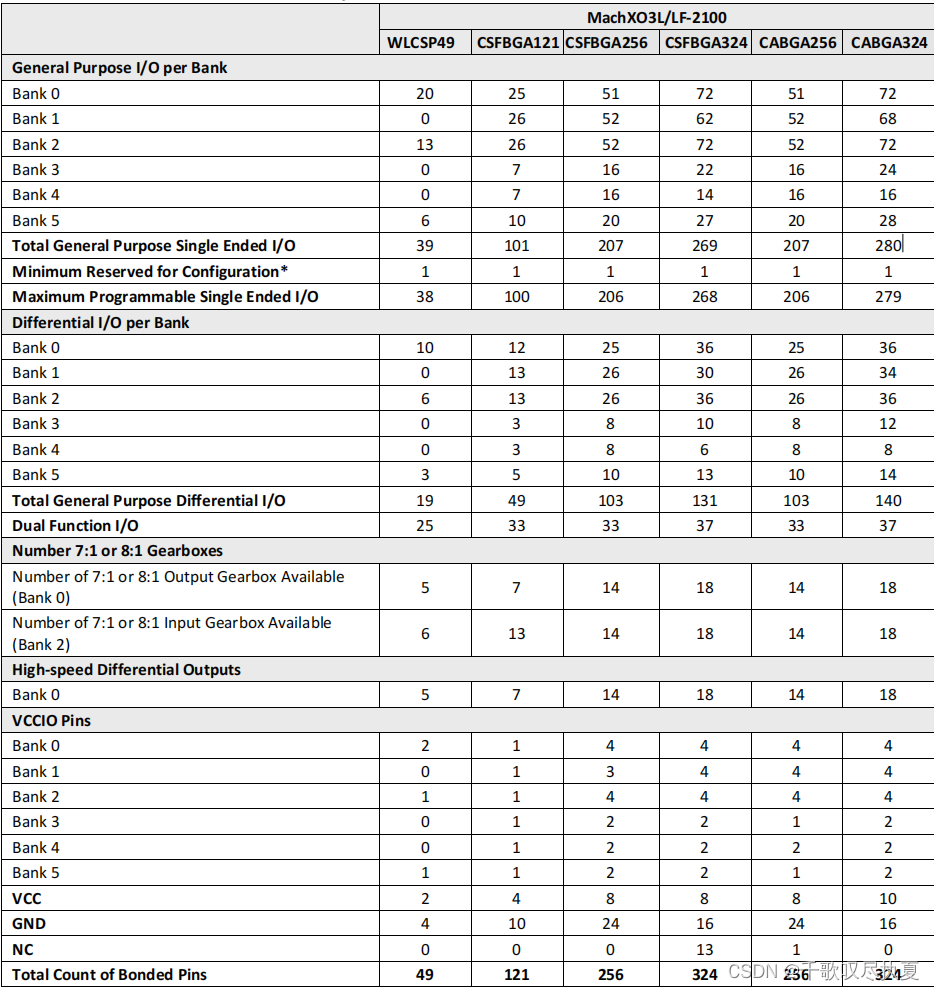

MachXO3L/LF-2100 Pin Summary

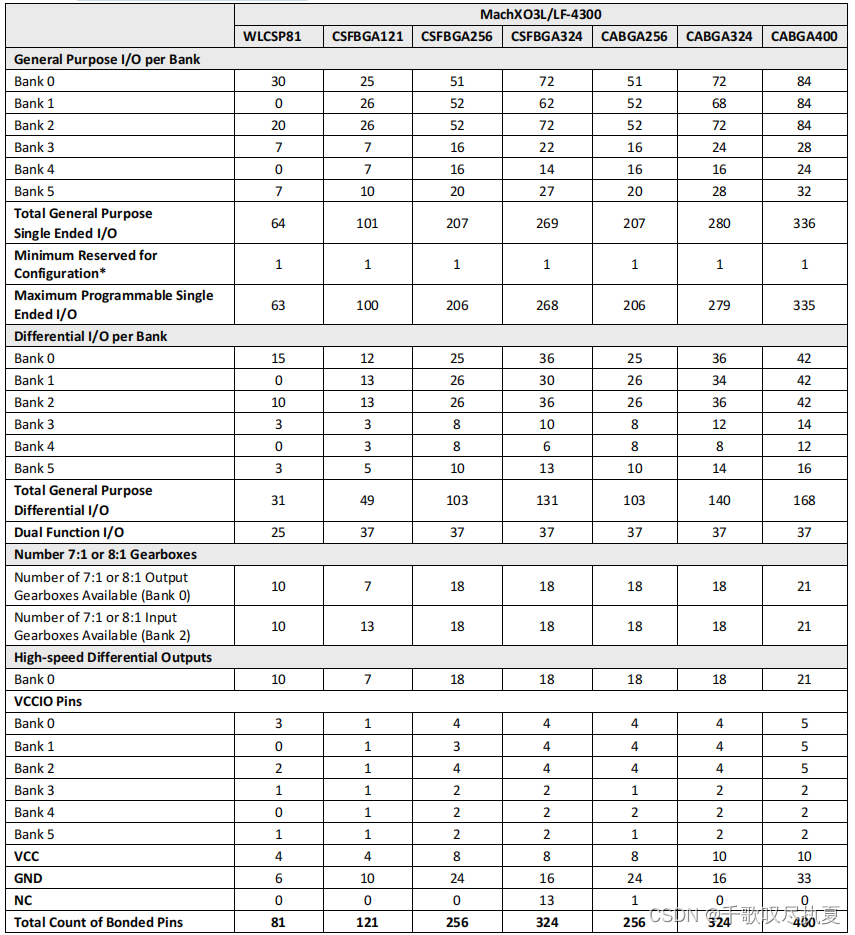

MachXO3L/LF-4300 Pin Summary

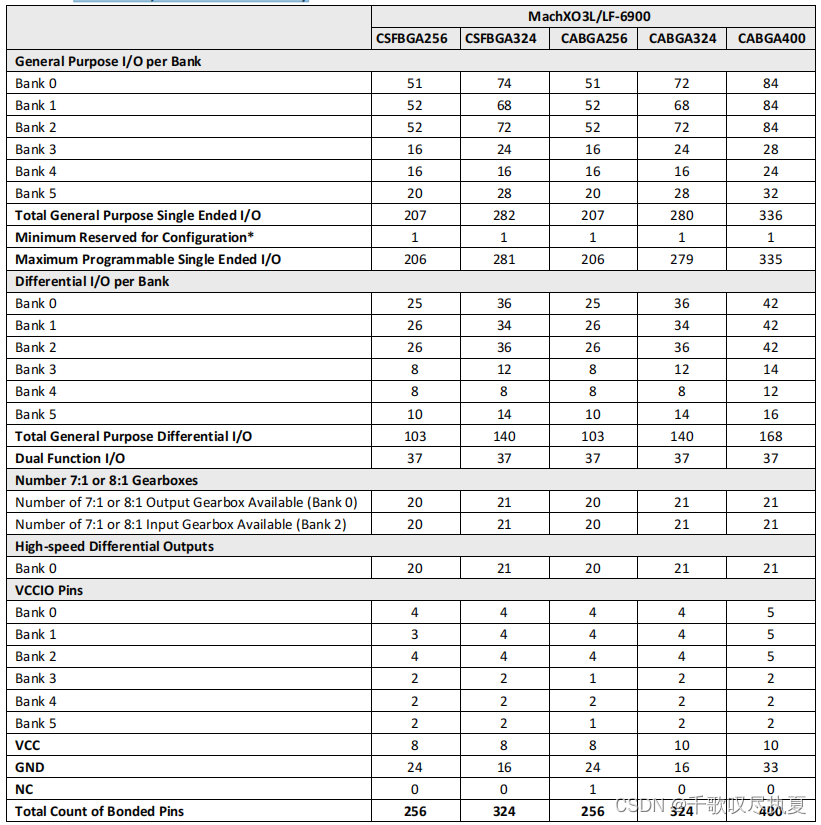

MachXO3L/LF-6900 Pin Summary

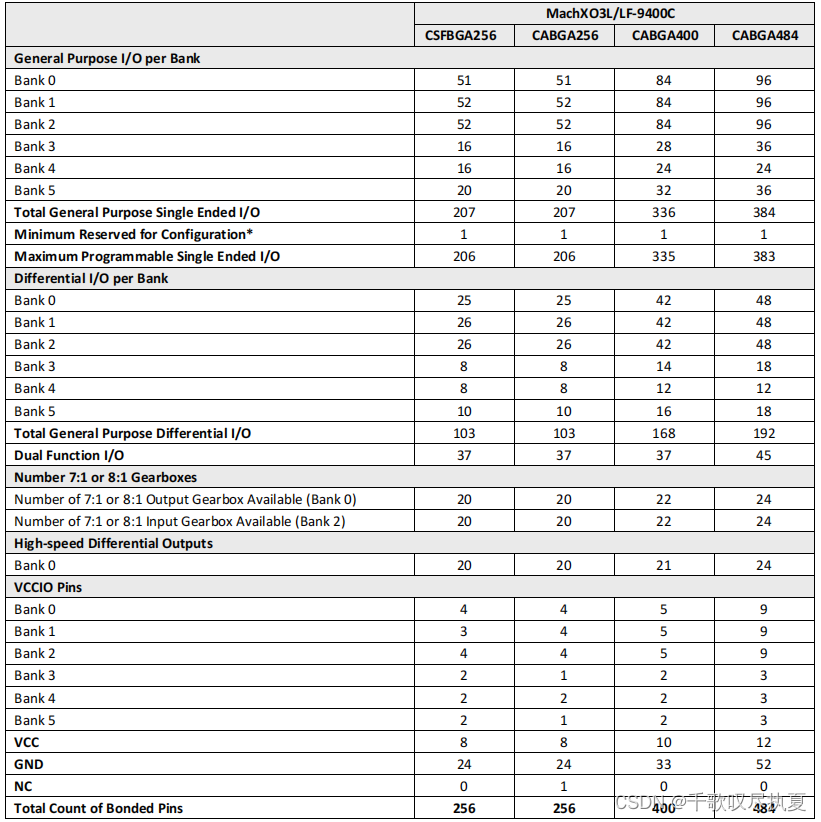

MachXO3L/LF-9400C Pin Summary

四、参考文献

MachXO3 Family Data Sheet

官网:https://www.latticesemi.com/zh-CN/Products/FPGAandCPLD/MachXO3

本文详细介绍了MachXO3CPLD的特性,包括其超低密度设计、先进的I/O支持、内置块RAM和预设功能,以及各种封装选项。重点讲解了L/LF系列的低功耗、高性能和配置灵活性,适合消费电子到汽车系统的应用。

本文详细介绍了MachXO3CPLD的特性,包括其超低密度设计、先进的I/O支持、内置块RAM和预设功能,以及各种封装选项。重点讲解了L/LF系列的低功耗、高性能和配置灵活性,适合消费电子到汽车系统的应用。

636

636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?