TC3XX内存映射Features

AURIX TC3xx系列设备的内存映射中包含的各个部分。这些内存部分在设备上有各自的用途和特性。以下是这些部分的一些概念解释:

-

Program Flash Interface (PFI) 和 Program Flash Memory (PF) 是用来存储程序代码的闪存。即使在断电时,存储在闪存中的数据也不会丢失。

-

Data Memory Unit (DMU) 包含了多种类型的数据存储区:

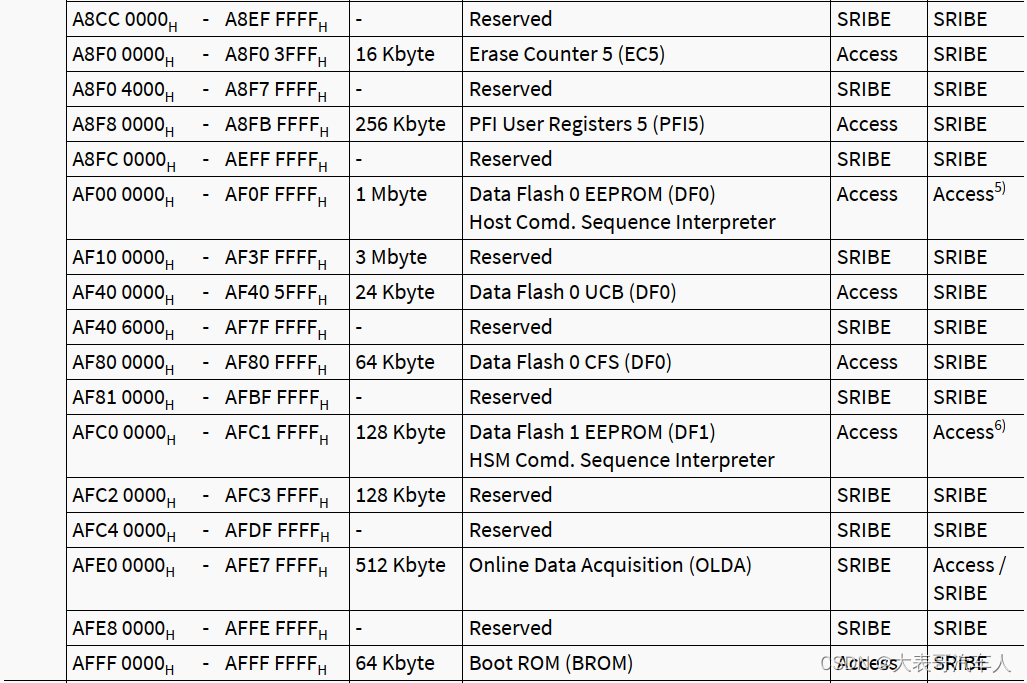

- Data Flash Memory for CPU EEPROM (DF0) 和 Data Flash Memory for HSM EEPROM (DF1) 是用来模拟EEPROM的闪存。这种闪存可以被反复地擦写,适合存储需要频繁更新的数据。

- User Configuration Blocks (DF0) 和 Configuration Sector (DF0) 可能用于存储系统配置信息。

-

CPU0和CPU1 以及 CPU2至CPU5 都有一些用于高速数据存取的本地存储,包括:

- Program Scratch-Pad SRAM (PSPR) 和 Data Scratch-Pad SRAM (DSPR) 是SRAM类型的内存,用于存储程序代码和数据。

- Program Cache (P-Cache) 和 Data Cache (D-Cache) 是CPU的高速缓存,用于加速对常用数据和程序的访问。

- Local Memory Unit (DLMU) 可能是一个本地数据存储区。

-

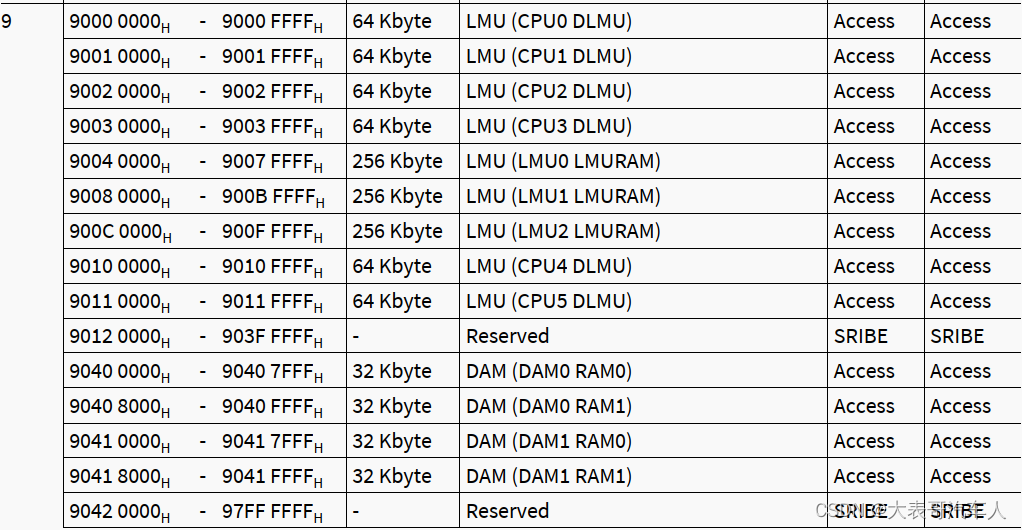

Local Memory Unit (LMU) 包括 LMU SRAM (CPU DLMU or LMU LMURAM) 和 DAM SRAM (DAMRAM),这些可能是用于高速数据存取的本地内存。

-

Boot ROM (BROM) 是存储启动代码的只读存储器。当设备上电或复位时,CPU会从这里开始执行代码。

此外,这个设备还有一些内部总线,包括 System Peripheral Bus (SPB),Shared Resource Interconnect (SRI) 和 Back Bone Bus (BBB)。这些总线用于在设备内部的各个部分之间传输数据。

2.3 功能描述

总线特定地址映射描述了不同总线主设备对芯片内存储器和模块访问的反应方式,以及相应总线的有效或无效地址范围。

例如,控制寄存器、SRAM块或模块内的闪存块/扇区的详细地址映射在相关模块章节中描述。

注意:除了这里描述的系统地址映射之外,每个TriCore还具有通过C000_0000H对其PSPR进行TriCore IP内部访问以及通过D000_0000H对其DSPR进行内部访问。这种对本地高速缓存SRAM的附加/私有视图在CPU章节中描述。

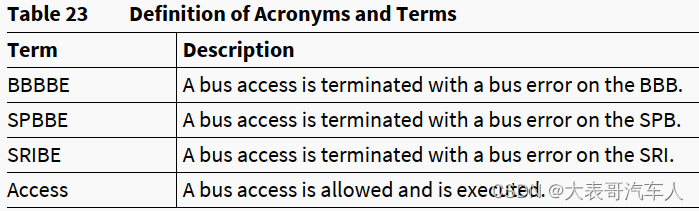

表23定义了地址映射表(表24和表40)中使用的首字母缩略词和其他术语。

2.3.1 段

本节总结了各段的内容。

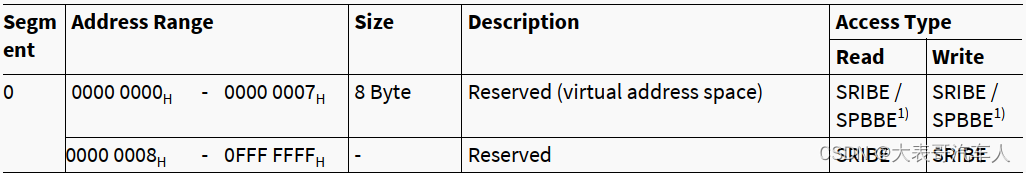

段0和2

这些内存段是保留的。

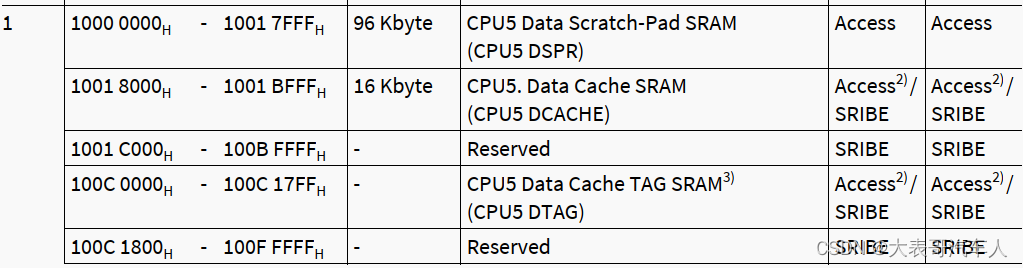

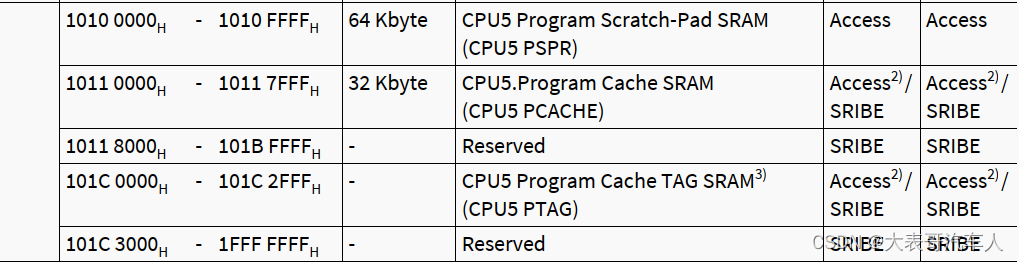

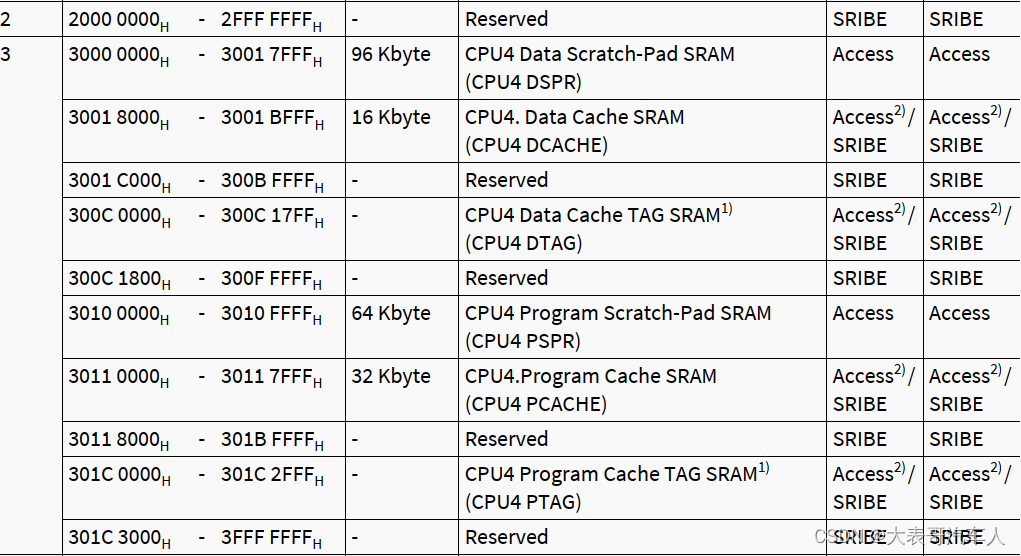

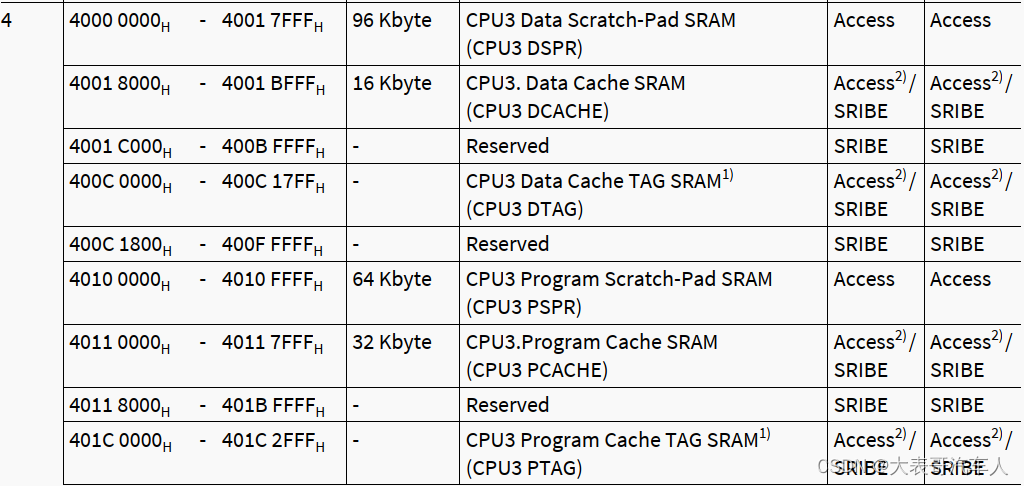

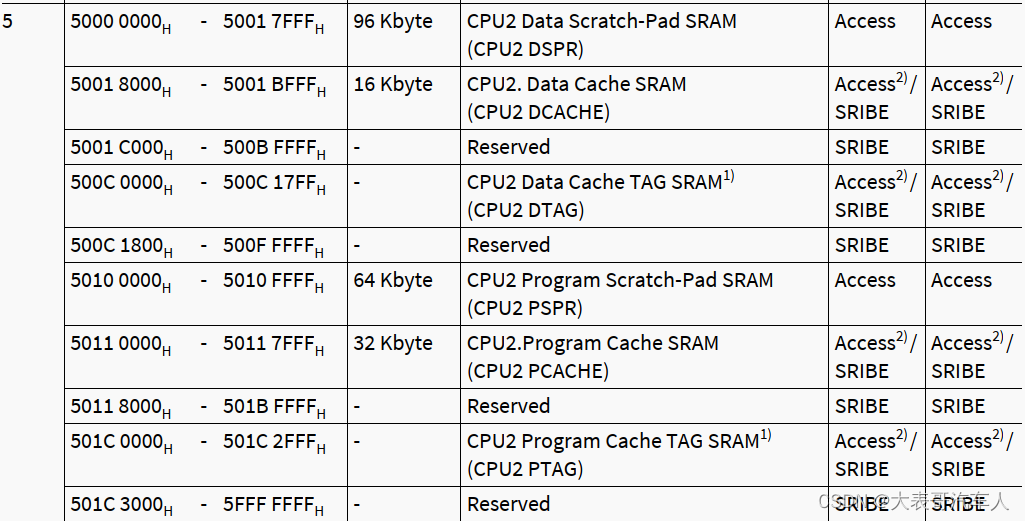

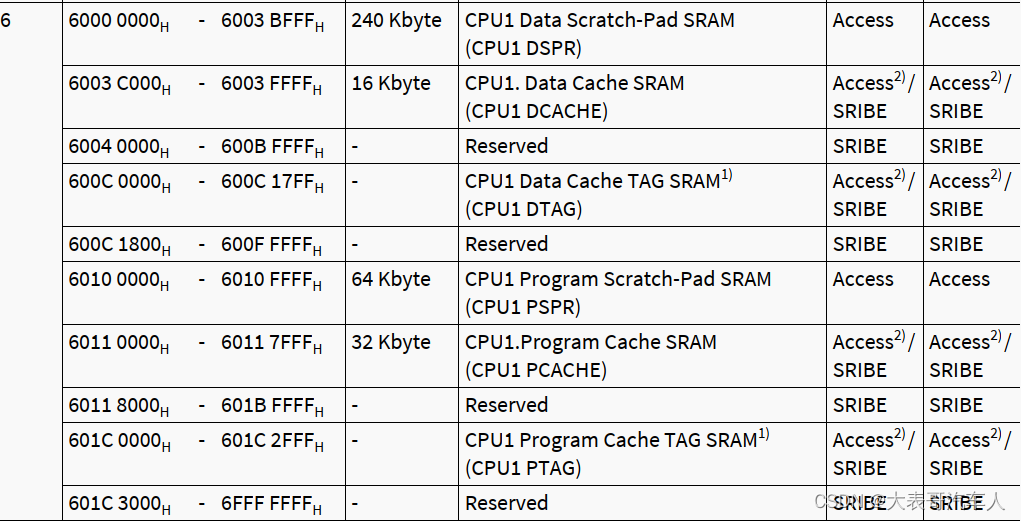

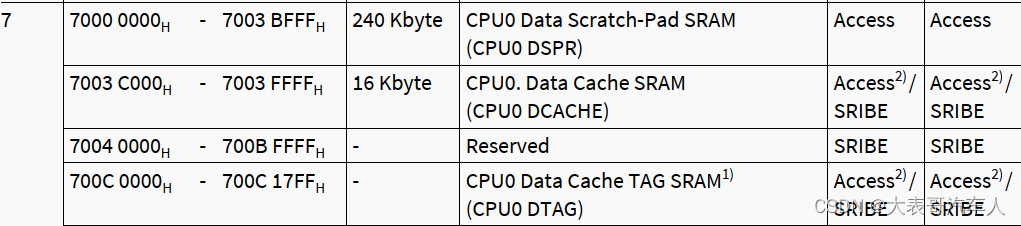

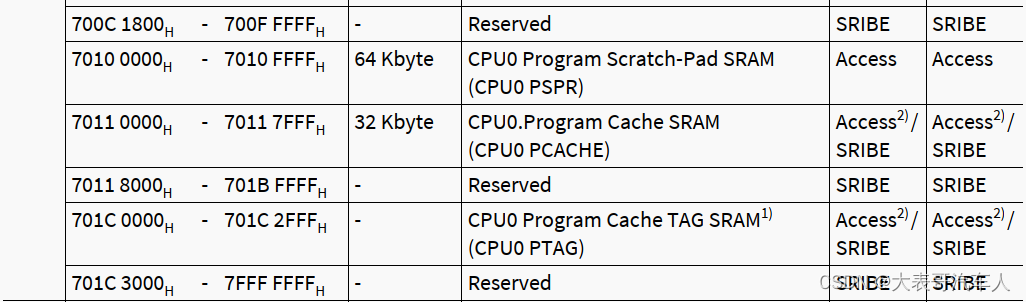

段1和3-7

这些内存段允许访问CPU程序和数据高速缓存SRAM(PSPR,DSPR),程序和数据缓存SRAM(PCACHE,DCACHE)以及与程序和数据缓存相关的标记SRAM(PTAG SRAM1)和DTAG SRAM1)。

如果支持DCACHE,则只有在禁用数据缓存时才能访问DCACHE和DTAG SRAM1)。

只有在禁用相关程序缓存时才能访问PCACHE和PTAG SRAMs1)。

这些段的属性(缓存/非缓存)可以为每个CPU的数据和程序侧单独部分配置2)(请参阅CPU章节:物理内存属性寄存器,PMAx)。

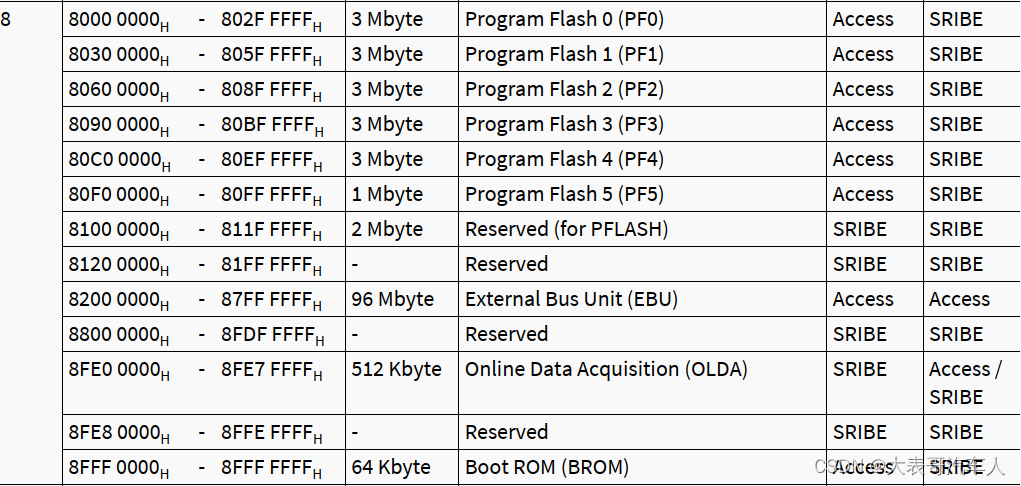

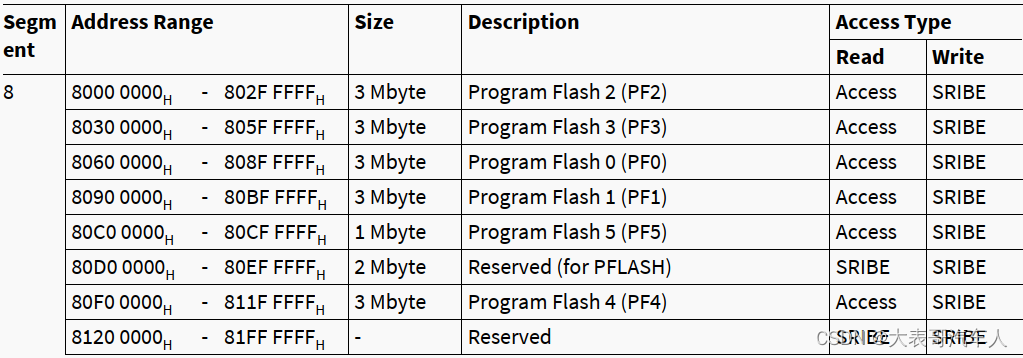

段8

此内存段允许对PFlash和BROM进行缓存访问。

段9

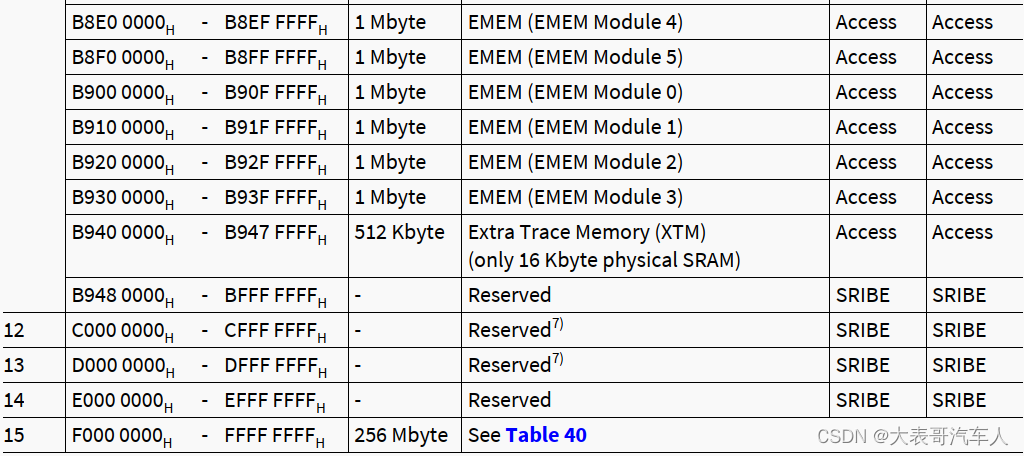

此内存段允许对LMU和EMEM进行缓存访问。

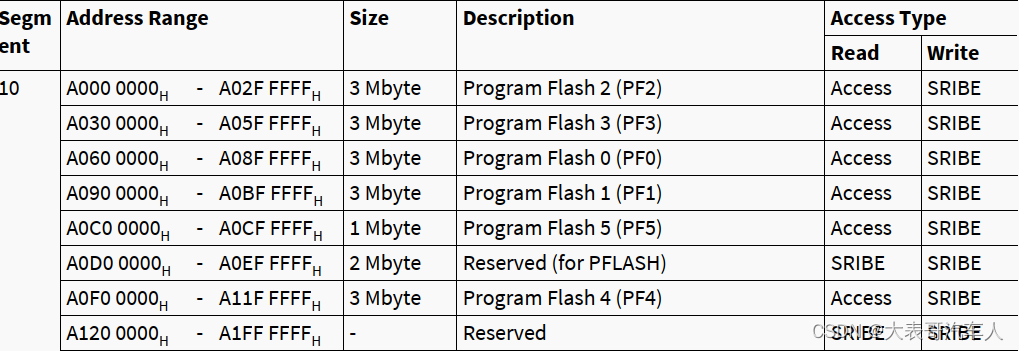

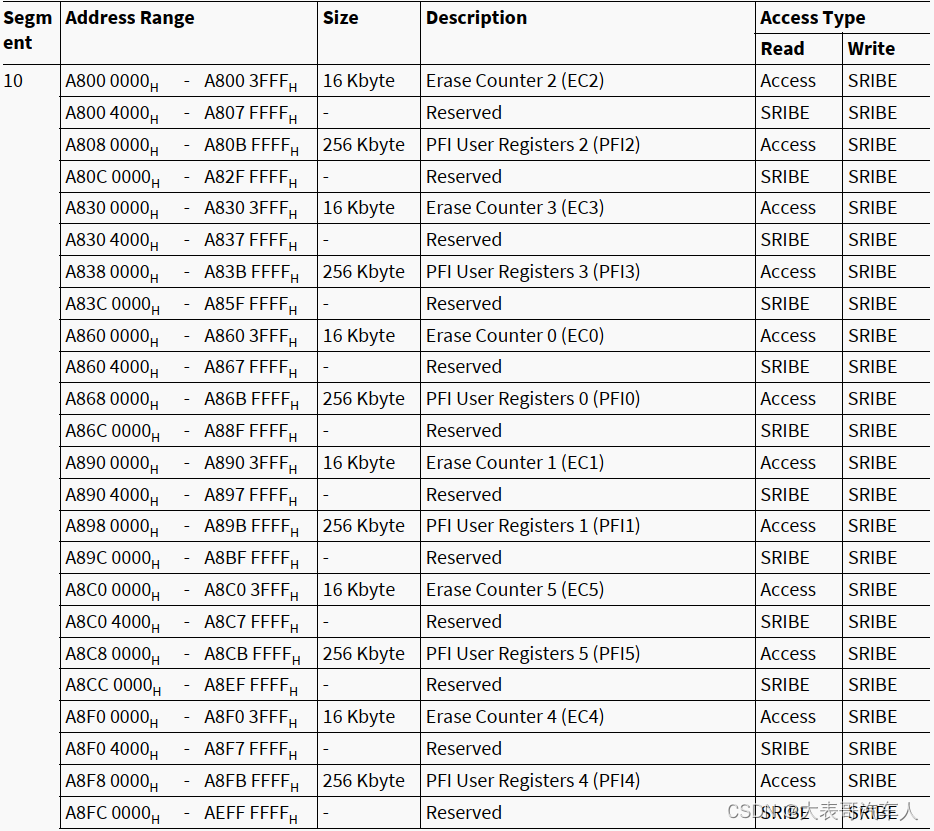

段10

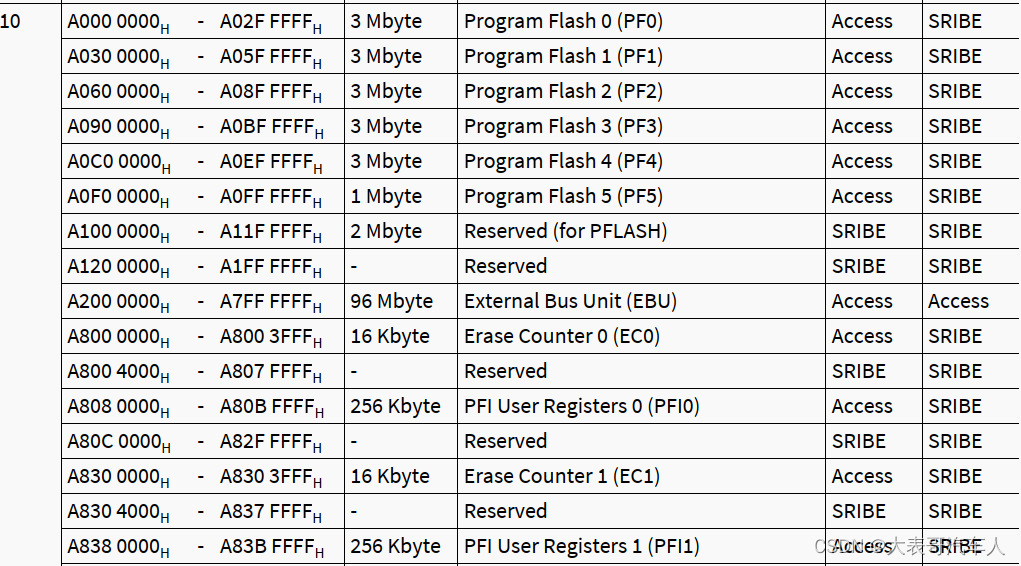

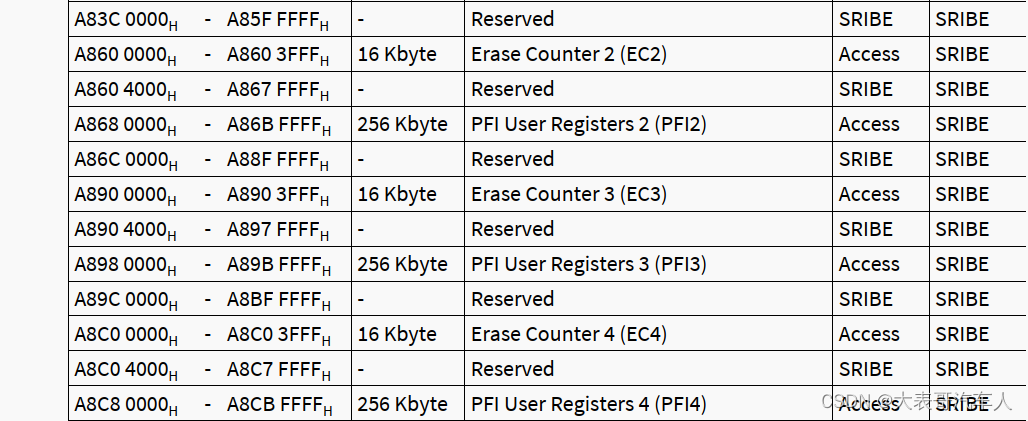

此内存段允许对PFlash、DFlash和BROM进行非缓存访问。

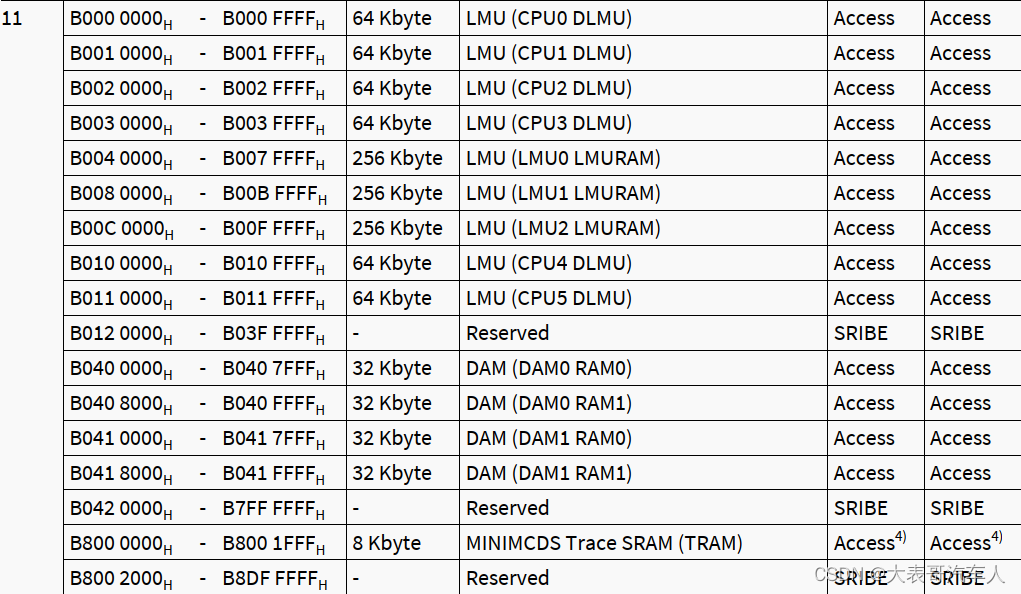

段11

此内存段允许对LMU和EMEM进行非缓存访问。

段12

此内存段是保留的。

段13

此内存段是保留的。

段14

此内存段是保留的。

段15

低128 MByte是SPB地址空间,高128 MByte是SRI地址空间。

2.3.2 On Chip Bus System的地址映射

所有总线主控代理都可以在相同地址访问相同的外设和存储器。系统地址映射对所有CPU可见且有效,这意味着所有外设和资源都可以从所有TriCore CPU和其他芯片上的总线主控代理访问。

多个总线主控代理并行访问一个从属代理会按顺序执行。此外,SRI、SPB和BBB支持来自CPU的原子读修改写序列。

2.3.2.1 段0到14

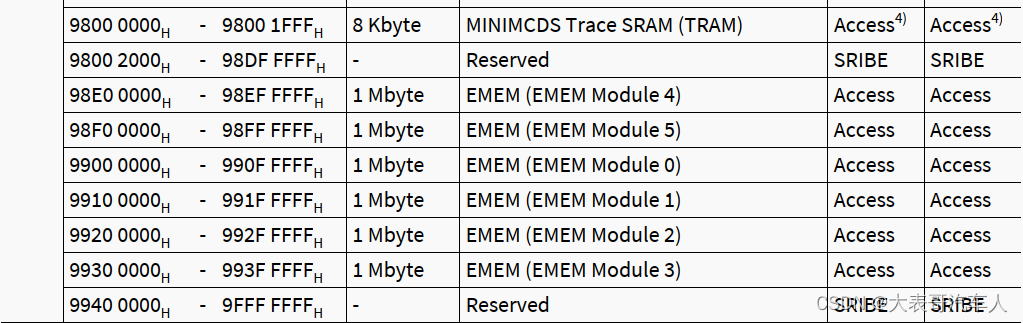

表24显示了段0到14的地址映射。

注

1. 写入访问类型:对Flash资源的写入访问由DMU模块处理(Flash命令序列,请参阅DMU章节获取详细信息)。

表24

1)如果发生SPB访问0000 0000H,则SPB BCU会生成总线错误。

1)如果发生SPB访问0000 0000H,则SPB BCU会生成总线错误。

2)只有在映射到地址空间时(PCACHE / DCACHE禁用。有关详细信息,请参见CPU章节,寄存器SMACON),才能访问PCACHE / DCACHE SRAM(以及相应的TAG SRAM)。

3)TAG SRAM不适用于作为通用SRAM使用,并且只能使用单个数据访问,并且只能使用64位对齐地址进行访问。 TAG SRAM在地址映射中的映射可以用作内存测试的附加选项。

4)TRAM不应用作通用SRAM,并且只有在启用OCDS时才能访问。

5)主机命令序列解释器

6)HSM命令序列解释器

7)有关CPU本地视图到段C和段D的信息,请参见章节“CPU,本地和全局寻址”。

表格25 TC39x备用地址映射,用于段8 PFLASH的SOTA

表格26 TC39x备用地址映射,用于段10 PFLASH的SOTA

表格26 TC39x备用地址映射,用于段10 PFLASH的SOTA 表格27 TC39x备用地址映射,用于段10擦除计数器和寄存器的SOTA

表格27 TC39x备用地址映射,用于段10擦除计数器和寄存器的SOTA

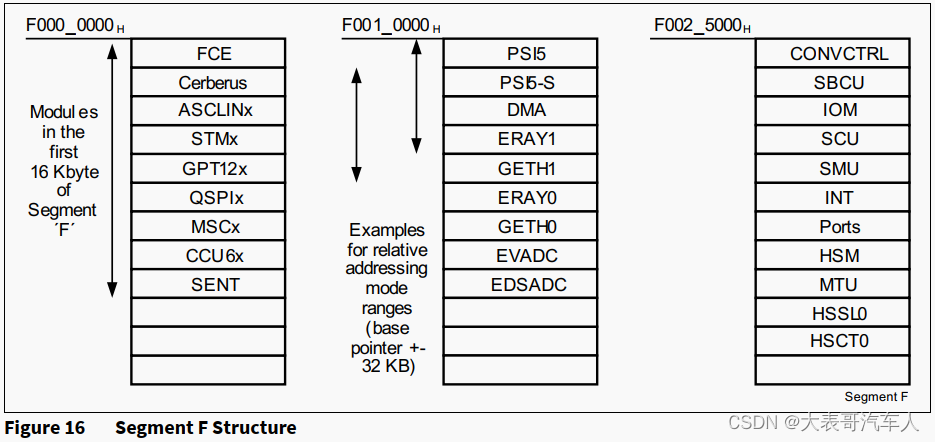

2.3.2.2 段15

表40显示了从SRI和SPB总线主机(总线主机代理在芯片总线系统章节中有描述)所看到的段´F´的地址映射。它描述了模块到段F的映射。模块地址范围的详细信息可以在模块章节的寄存器概述中找到。

表40(略)

图16概述了模块地址范围的地址映射:

• 绝对寻址范围

- 如果在段´F´的前16 Kbyte中寻址模块,则CPU可以使用绝对寻址模式访问该模块。

• 其他

- 如果在段´F´的前16 Kbyte之上寻址模块,则CPU可以使用基址+偏移量访问该模块。

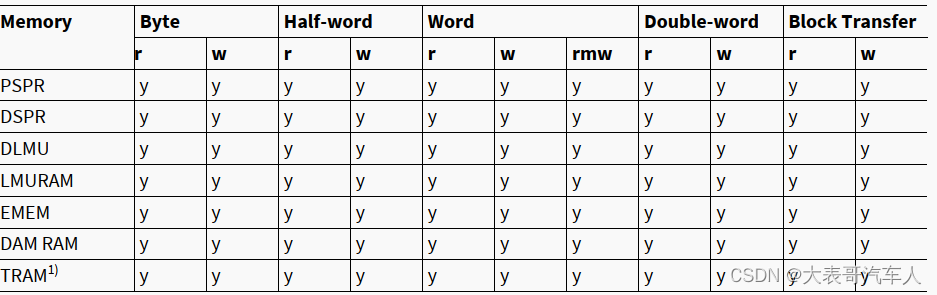

2.3.3 内存访问

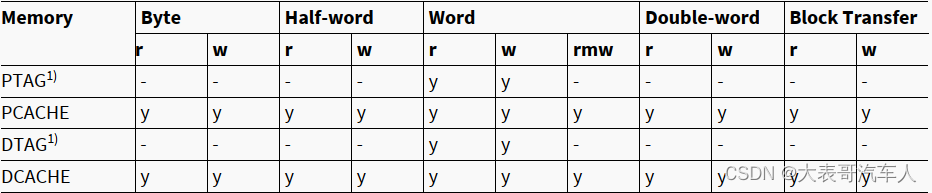

以下表格列出了支持的内存类型和访问大小1):

表41。 标准读写存储器(C变量)

1)TRAM不得用作通用SRAM,只有在启用OCDS时才能访问。

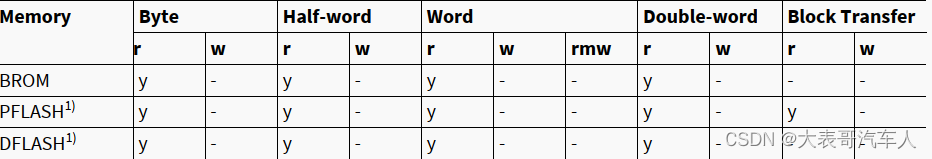

表42 标准只读存储器(C常量)

1)FLASH存储器应通过命令序列进行编程和擦除。

表43 非标准存储器

1)标签SRAM不应用作通用SRAM,只能通过32位数据访问和64位对齐地址进行访问。将标签SRAM映射到地址映射中可用作内存测试的附加选项。标签SRAM的大小低于24位,因此32位写入或读取的8个最高有效位无关紧要。

718

718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?