93.D触发器和多选器复合子模块

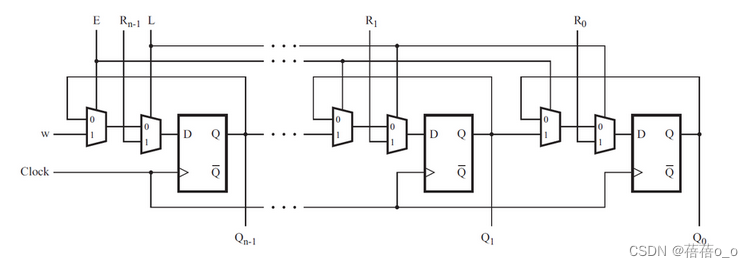

写出该电路的可用于实例化的子模块

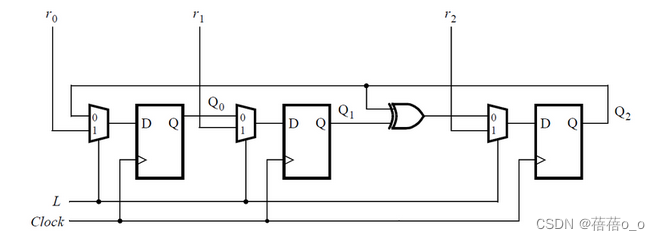

94.D触发器和多选器复合子模块

95.D触发器和门复合

注意重置状态。确保每个D触发器的Q输出实际上与其Q输出相反,甚至在模拟的第一个时钟沿之前。

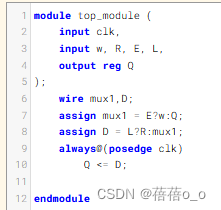

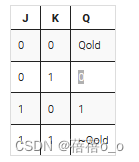

96.JK触发器:用D触发器和门来实现

JK触发器真值表如下所示

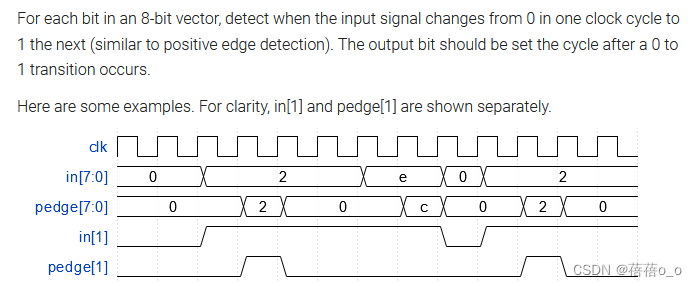

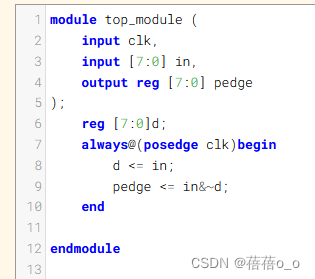

97.检测输入每个位的上升沿

98.检测输入每个位的双边沿

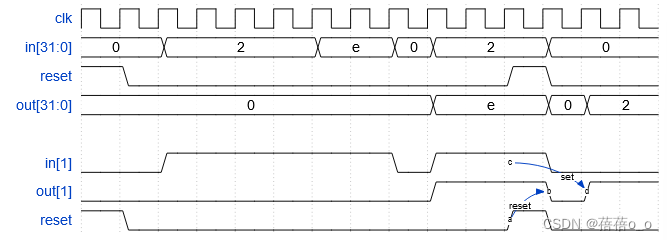

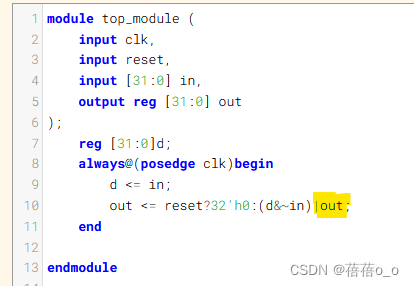

99.边缘截取

对于32位矢量中的每一位,捕捉输入信号何时从一个时钟周期中的1变为下一个时钟循环中的0。“捕获”意味着输出将保持1,直到寄存器复位(同步复位)。

每个输出位的行为类似于SR触发器:输出位应在1到0转换发生后的周期内设置(为1)。当复位为高时,输出位应在正时钟沿复位(为0)。如果以上两个事件同时发生,则重置优先。在下面示例波形的最后4个周期中,“重置”事件比“设置”事件早一个周期发生,因此此处没有冲突。

在下面的示例波形中,为了清楚起见,再次单独显示了reset、In[1]和out[1]。

我的理解:输出out在reset为1时复位,在reset为0且检测到in下降沿是为一直置位(除非reset才复位)

一开始没写荧光区域导致错误,这里要注意检测到下降沿后会一直置位。

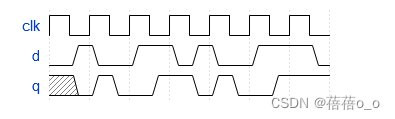

100.双边沿触发的D触发器

您熟悉在时钟的正沿或负沿触发的触发器。双边沿触发触发器在时钟的两个边沿上被触发。然而,FPGA没有双边缘触发触发器,并且始终@(posedge clk或negedge clk)不被接受为法律敏感性列表。

这题好难,再悟悟!!

9842

9842

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?