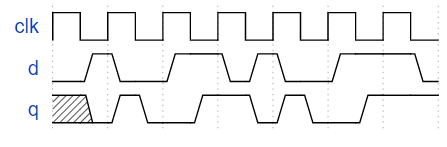

双沿触发触发器在时钟的两个边沿触发。 但是,FPGA没有双沿触发触发器,因此始终不接受@(posedge clk或negedge clk)作为合法敏感性列表。

module top_module (

input clk,

input d,

output q

);

reg q_d1;

reg q_d2;

always@(posedge clk)begin

q_d1 <= d ^ q_d2;

end

always@(negedge clk)begin

q_d2 <= d ^ q_d1;

end

assign q = q_d1 ^ q_d2;

endmodule

(Note: It's not necessarily perfectly equivalent: The output of flip-flops have no glitches, but a larger combinational circuit that emulates this behaviour might. But we'll ignore this detail here.))

3624

3624

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?