题目如下:

我一开始想当然就这样写了

我一开始想当然就这样写了

module top_module (

input clk,

input d,

output q

);

always@(posedge clk)

q <= d;

always@(negedge clk)

q <= d;

endmodule

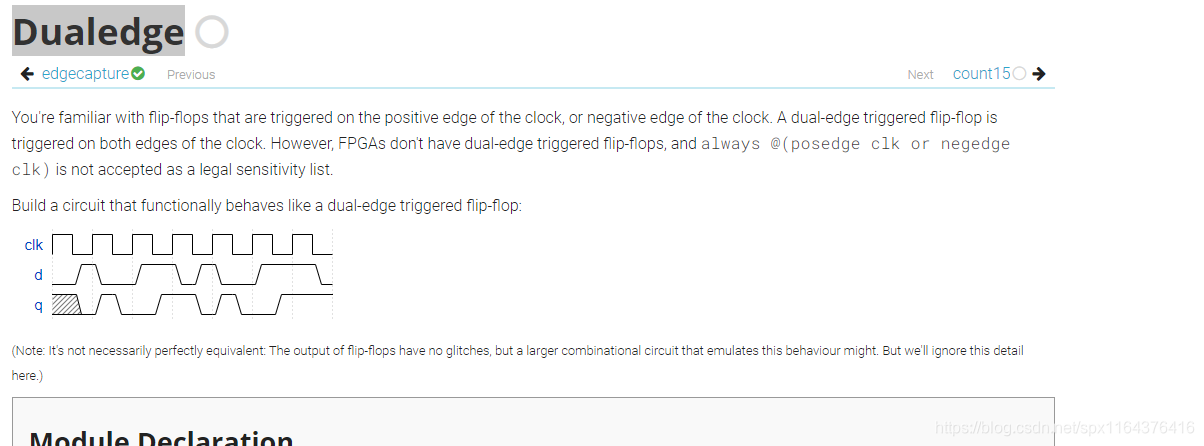

结果报错,后面网上搜了一下,看了下这篇博文

【 Verilog 】always@()的敏感源中为什么不能双边沿触发?为什么不能双时钟触发?,大致意思是说FPGA(以及其他任何地方)上的触发器是一个具有一个时钟且仅对该时钟的一个边缘敏感的器件。 因此,当灵敏度列表始终为@(posedge clk)时,综合工具只能映射到此设备。 我们有触发器的变种,可以进行异步预置/清除,因此将映射到始终@(posedge clk或<posedge / negedge> rst),但就是这样。

没有真正的硬件设备可以完成与你所描述的相同的东西 - 总是@(posedge clk or negedge clk)。

唯一的例外(种类)是IDDR和ODDR,这些需要实例化 - 它们不能从HDL描述中推断出来。

见此博文FPGA中如何实现双边沿采样?

最后网上找了下实现答案:

module top_module (

input clk,

input d,

output q

);

reg p,n;

always@(posedge clk)

p <= d^n;

always@(negedge clk)

n <= d^p;

assign q = p^n;

endmodule

具体是理解上升沿时, q = p^n = d ^n ^n = d;

下降沿时 , q = p^n = p ^ d ^p = d;

本文讨论了在Verilog中使用always @(posedge clk or negedge clk)进行双边沿触发导致的错误,并解释了FPGA硬件不支持这种触发方式的原因。通过实例展示了如何使用两个边沿敏感的always块和中间寄存器来实现双边沿采样的功能。总结了IDDR和ODDR等特殊器件在某些情况下的应用。

本文讨论了在Verilog中使用always @(posedge clk or negedge clk)进行双边沿触发导致的错误,并解释了FPGA硬件不支持这种触发方式的原因。通过实例展示了如何使用两个边沿敏感的always块和中间寄存器来实现双边沿采样的功能。总结了IDDR和ODDR等特殊器件在某些情况下的应用。

1106

1106

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?