一:写一套硬件描述语言,能够在指定的硬件平台上实现相应的功能

1:设计定义(让LED一秒闪烁一次)

2:设计输入(编写逻辑(使用Verilog代码描述逻辑),画逻辑图,使用IP)

3:综合工具(由专业的EDA软件进行,Quartus,Vivado,ISE),对所写的逻辑描述内容进行分析,并得到逻辑门级别的电路内容

4:功能仿真(使用专门的仿真工具进行仿真,验证设计的逻辑功能能够实现)仿真是理想情况,可靠度不是那么高,不要依赖仿真XXX

对于数字电路来说,仿真时基本接近于真实情况的,是可信的。

5:布局布线

6:分析性能:1)时序仿真(非常耗费时间)。2)静态时序分析

下载到目标板上运行,查看运行结果,ILA Signaltap II

7:板级调试:让设计的逻辑在目标板上正常工作,(功能正常,性能稳定)

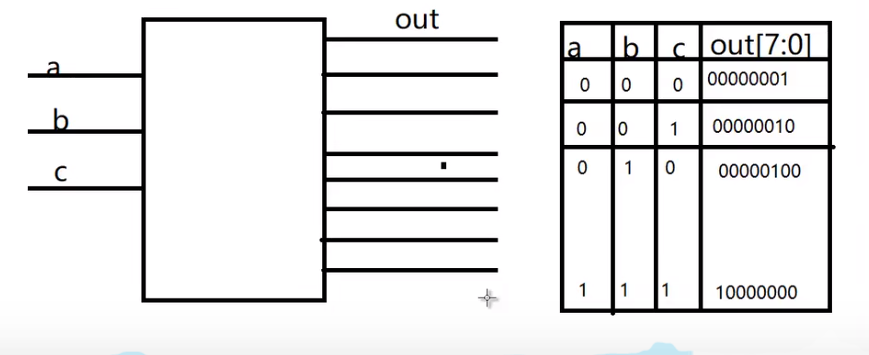

二:三八译码器

module decoder3_8(input a,input b,input c,output reg [7:0]out);

//其中{}表示位拼接,可以用于对输入的数据连在一起判断

//还可以像以下这么用

// wire [3:0]d;

// assign d={a,b,1'b0,c};

always@(a,b,c)begin

case({a,b,c})

3'b000:out=8'b0000_0001;

3'b001:out=8'b0000_0010;

3'b010:out=8'b0000_0100;

3'b011:out=8'b0000_1000;

3'b100:out=8'b0001_0000;

3'b101:out=8'b0010_0000;

3'b110:out=8'b0100_0000;

3'b111:out=8'b1000_0000;

endcase

end

endmodule

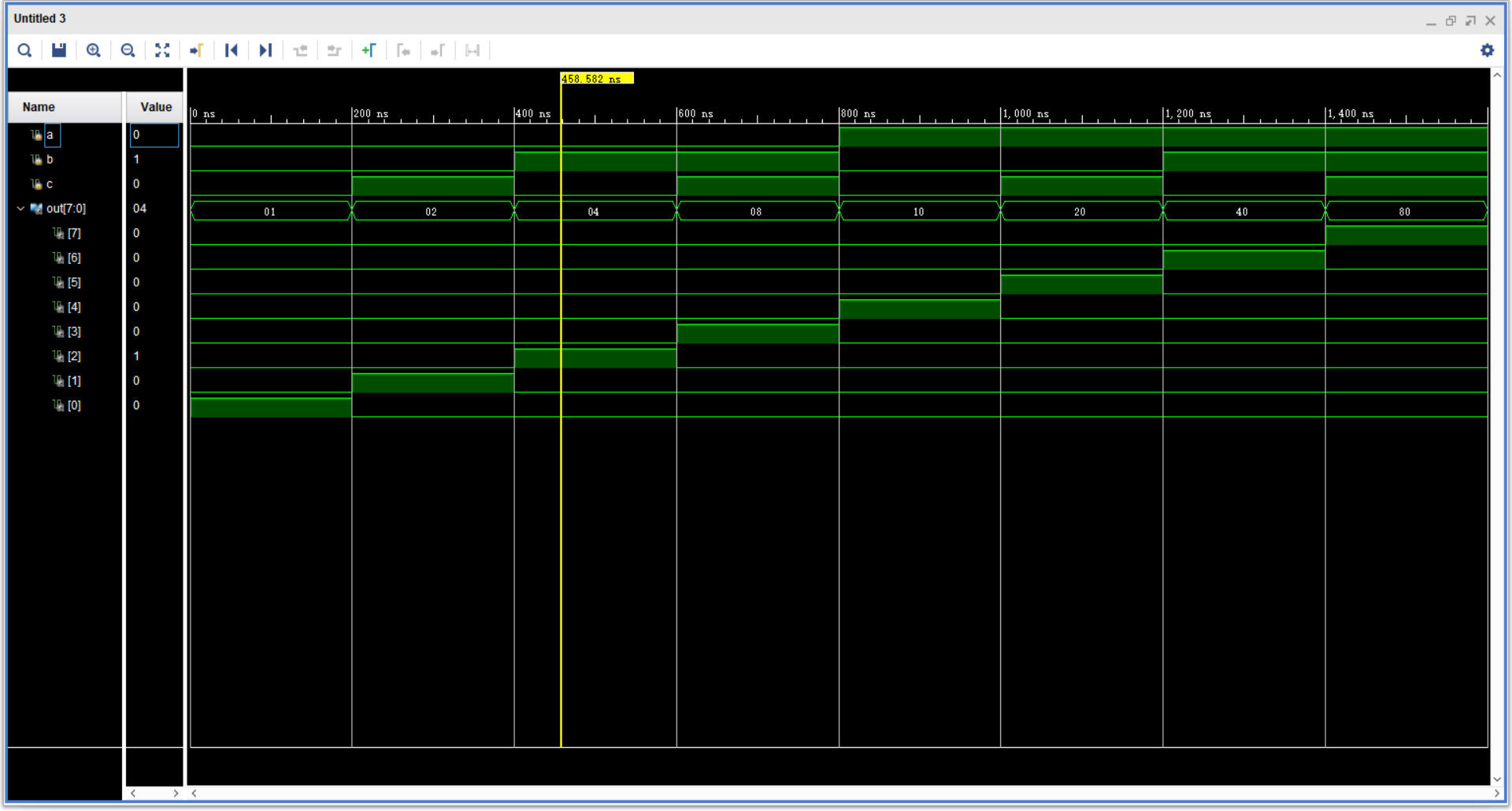

测试文件

`timescale 1ns / 1ns

module decoder3_8_tb();

reg a;

reg b;

reg c;

wire [7:0]out;

decoder3_8 decoder3_8(

.a(a),.b(b),.c(c),.out(out)

);

initial begin

a=0;b=0;c=0;

#200;

a=0;b=0;c=1;

#200;

a=0;b=1;c=0;

#200;

a=0;b=1;c=1;

#200;

a=1;b=0;c=0;

#200;

a=1;b=0;c=1;

#200;

a=1;b=1;c=0;

#200;

a=1;b=1;c=1;

#200;

//这里要记得最后还是要加一个#200,不然仿真的时候显示不出来

$stop;

end

endmodule

小记:

1:在vivado中放在写激励文件的时候不用写$stop,因为它会自己结束,然而在modelsim中要记住在仿真结束位置加上$stop

2:行为级仿真和时序级仿真是有区别的,时序级别仿真可以看出输入改变的时候输出并不会立即改变因为有延时,感觉可以进行延迟测试观察~

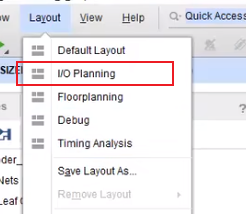

3:配置端口的时候可以选择直接操作控制板设置以及自己编写对应的文件

4:只有在打开分析综合设置才能出现后面的I/O Planning

1526

1526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?