1:CPU、DSP、GPU都算软件可编程的硬件

2:dsp在递归方面有所减弱,在递归方面有所增强,比如递归啊等,GPU可以同时处理多个进程,对于大块数据,流处理比较适用

3:为了提高运算量处理更多的数据,可以要么提高主频,要么由单核变多核,增加并行度,但是随之而来带来的问题是功耗

4:FPGA善于进行并行计算,有大量的乘法器,同时由于ARM的嵌入,在管理方面也增强,功耗相比于CPU低,并且对于软件工程师来说用C/C++编程变成一种可能

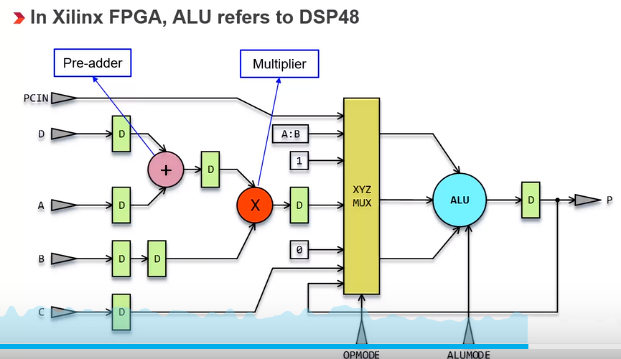

5:对于算法工程师来说,更关注逻辑单元、存储单元、算数逻辑单元

逻辑单元——查找表,DSP48

存储单元:Block RAM、分布式的RAM,对于大块的存储选择Block RAM,小量的<1kb的选择分布式的

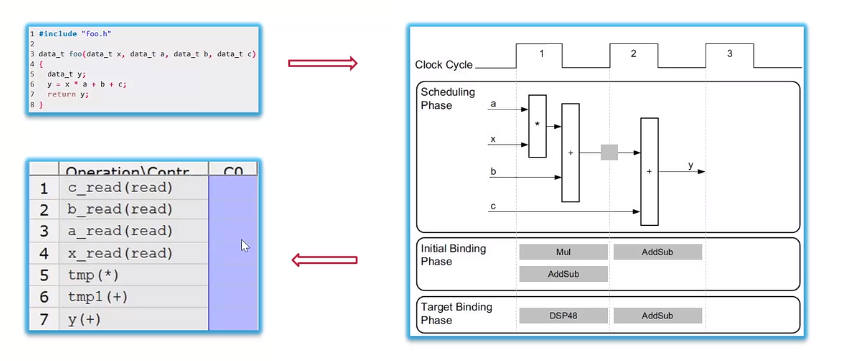

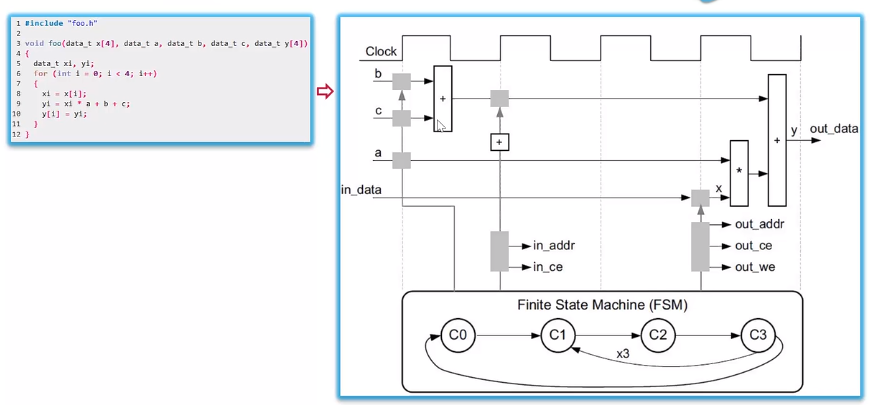

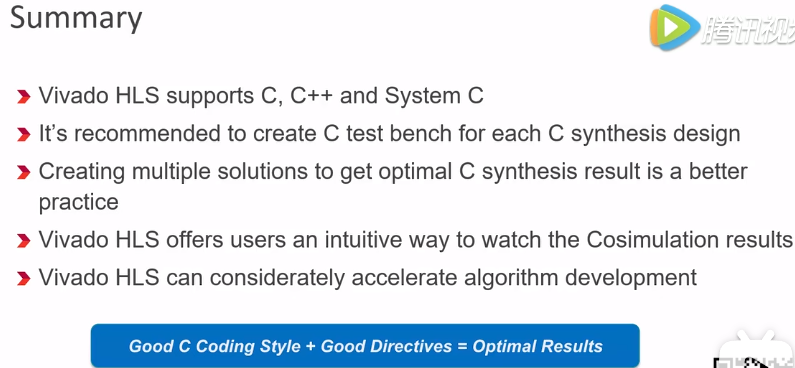

6:vivado hls把高级语言算法转换为hls的过程

调度(每个时钟周期做什么)——控制逻辑提取(状态机)——binding(完成映射过程,每个操作都要在什么器件上执行)

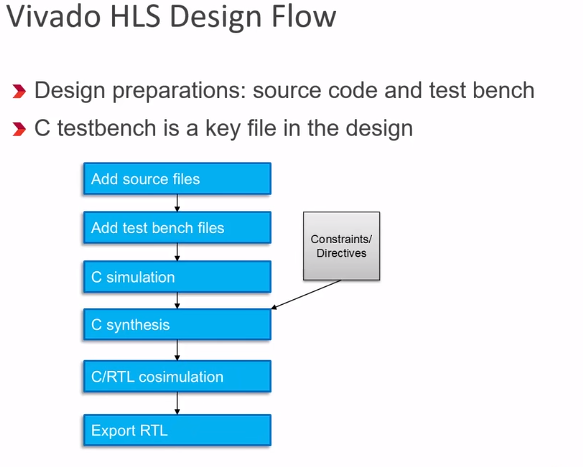

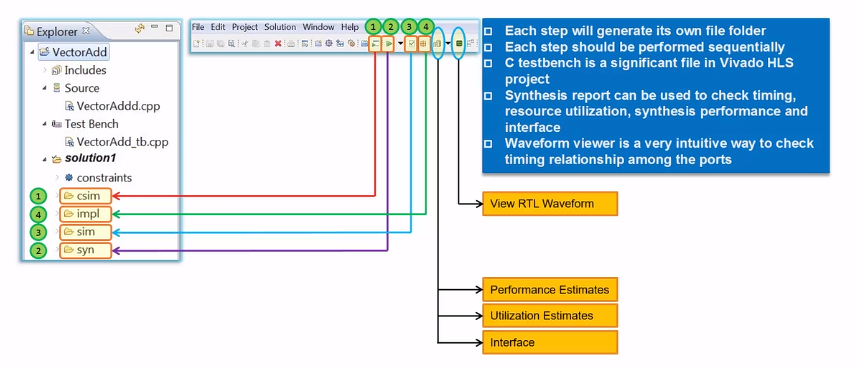

7:Design HLS with Vivado HLS

C_testbench很重要,其不仅用于输入和仿真结果的对比,同时对于生成RTL的testbench也很有用

csim(C仿真)-cyn(C综合)-sim(C和RTL的协同仿真)-impl(export RTL)

性能评估、资源利用率评估、接口信息

439

439

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?