ram初始配置

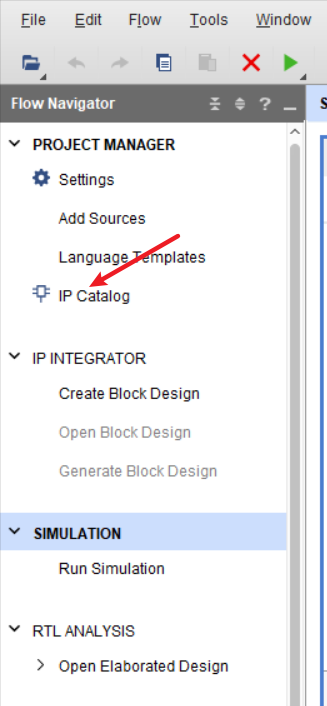

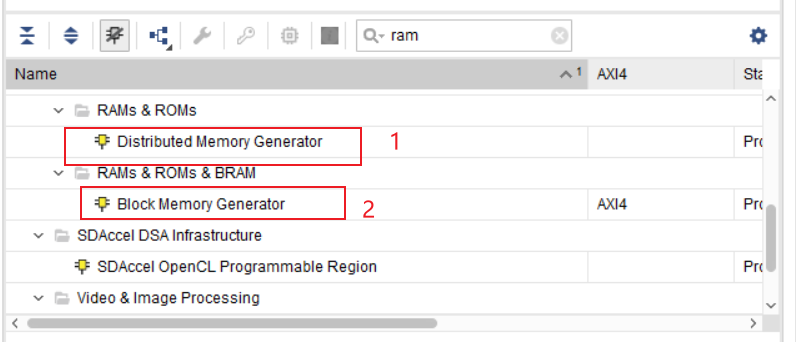

首先点击侧边栏的IP Catalog并在搜索框中搜索ram,有两种ram形式,块状ram更有利于处于数据量比较大的数据,这里我们选择第二种

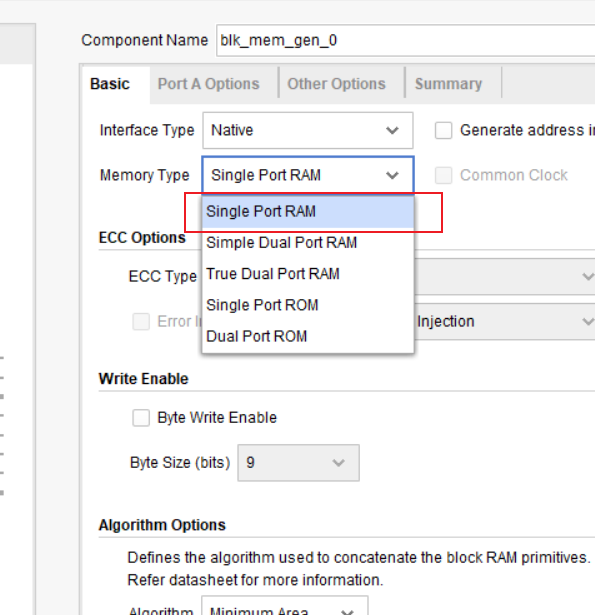

之后根据需要选择单端口的只读存储器,并设置使能为总使能~设置好端口宽度与深度并加入初始化数据后开始编写代码

rom测试代码编写

`timescale 1ns / 1ps

module tbPossRam();

reg clka;

reg ena;

reg wea;

reg[14:0] addra;

reg[15:0] dina;

wire[15:0] douta;

//wire[15:0] douta2;

possRam possRam(

clka,

ena,

wea,

addra,

dina,

douta

);

initial clka=0;

always#10 clka=!clka;

initial begin

ena=0;

wea=0;

addra=0;

dina=0;

#201

repeat(20000)begin

ena=1;

wea=1;

#20;

dina=dina+1;

addra=addra+1;

end

ena=0;

wea=0;

#20000;

addra=19999;

#200;

repeat(20000)begin

ena=1;

#20;

addra=addra-1;

end

#2000

$stop;

end

endmodule

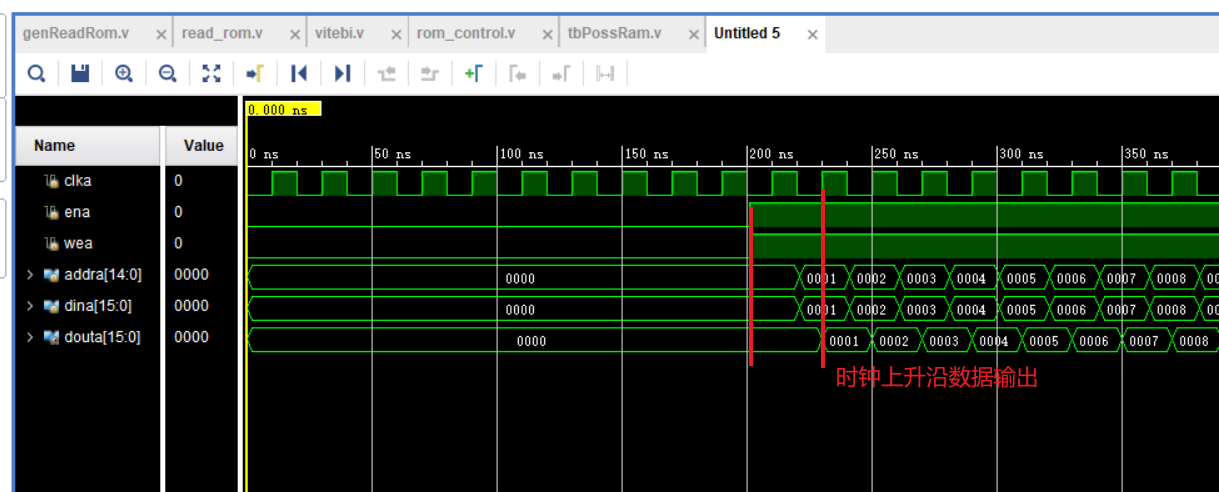

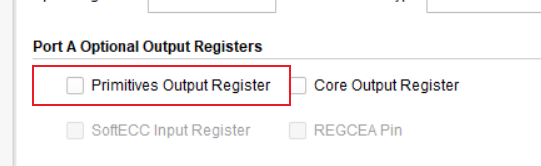

这里在配置寄存器的时候选择没有原始的寄存器输出~

rom实现

rom_control.v文件

`timescale 1ns / 1ps

module rom_control(Clk,Reset,addrA,addrB,addrY,addrPI);

input Clk;

input Reset;

output reg [13:0]addrA;

output reg [14:0]addrB;

output reg [7:0]addrY;

output reg [6:0]addrPI;

always@(posedge Clk or negedge Reset)begin

if(!Reset)

addrA<=0;

else if(addrA>=10000-1)

addrA<=0;

else

addrA<=addrA+1;

end

always@(posedge Clk or negedge Reset)begin

if(!Reset)

addrB<=0;

else if(addrB>=20000-1)

addrB<=0;

else

addrB<=addrB+1;

end

always@(posedge Clk or negedge Reset)begin

if(!Reset)

addrY<=0;

else if(addrY>=200-1)

addrY<=0;

else

addrY<=addrY+1;

end

always@(posedge Clk or negedge Reset)begin

if(!Reset)

addrPI<=0;

else if(addrPI>=100-1)

addrPI<=0;

else

addrPI<=addrPI+1;

end

endmodule

read_rom.v文件

`timescale 1ns / 1ps

module read_rom(Clk,Reset,A,B,Y,PI);

input Clk;

input Reset;

output [15:0]A;

output [15:0]B;

output [15:0]Y;

output [15:0]PI;

wire [13:0]addrA;

wire [14:0]addrB;

wire [7:0]addrY;

wire [6:0]addrPI;

rom_control rom_control

(.Clk(Clk),.Reset(Reset),.addrA(addrA),.addrB(addrB),.addrY(addrY),.addrPI(addrPI));

romA romA (

.clka(Clk),

.addra(addrA),

.douta(A)

);

romB romB (

.clka(Clk),

.addra(addrB),

.douta(B)

);

romY romY (

.clka(Clk),

.addra(addrY),

.douta(Y)

);

romPI romPI (

.clka(Clk),

.addra(addrPI),

.douta(PI)

);

endmodule

测试文件rom_tb.v

`timescale 1ns / 1ps

module rom_tb();

reg Clk;

reg Reset;

wire[15:0]A;

wire[15:0]B;

wire[15:0]Y;

wire[15:0]PI;

read_rom read_rom(Clk,Reset,A,B,Y,PI);

initial Clk=0;

always#10 Clk=!Clk;

initial begin

Reset=0;

#201

Reset=1;

#1000000

$stop;

end

endmodule

2094

2094

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?