Vivado会分析所有XDC约束时钟间的时序路径。通过set_clock_groups约束不同的时钟组(clock group),Vivado在时序分析时,当source clock和destination clock属于同一个时钟组时,才会分析此时序路径;而source clock和destination clock属于不同时钟组时,则会略过此时序路径的分析。下面讲解一下set_clock_groups约束:

Asynchronous Clock Groups

为了判别划分时钟组,将不同的时钟划分成以下两类:

a. Synchronous Clocks

当两个时钟间的相位是固定的,则可以称这两个时钟为同步时钟(synchronous clock)。一般同源,如由同一个MMCM or PLL产生的两个时钟可以称为同步时钟。因此可以将主时钟和与之对应的衍生时钟约束成同一个时钟组。

b. Asynchronous Clocks

无法判定两个时钟间相位时,则可以称这两个时钟为异步时钟(asynchronous clocks)。两个来自不同晶振的时钟,一定是异步时钟。通常情况下设计中不同的主时钟肯定是异步时钟,因此可以将这两个主时钟及其衍生时钟约束成不同的时钟组。

对于异步时钟,由于其两个时钟间相位不固定,时序分析的结果定然不确切,因此这部分的分析可以通过设置时钟组约束忽略,但是这并不意味着这部分的设计能工作正常;对于异步时钟间的设计,必须做跨时钟域处理,避免亚稳态的产生。

异步时钟组约束命令如下:

set_clock_groups-asynchronous-group [get_clocks {clk_Aclk_B}]

-group [get_clocks {clk_C}]-group …

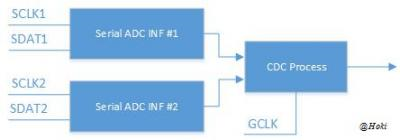

如图1中结构,串行AD1和串行AD2接口都带有随路时钟SCLK1和SCLK2,SCLK1和SCLK2属于异步时钟;ADC串并转换后的数据需要经过跨时钟域处理(CDC),转到GCLK主时钟域,GCLK与ADC的时钟也属于异步时钟,因此约束命令如下:

set_clock_groups-asynchronous -group [get_clocks {SCLK1}]

-group [get_clocks {SCLK2}] -group [get_clocks {GCLK}]

(图1)

Exclusive Clock Groups

在有些设计中,可能需要不同的工作模式,对应需要不同的时钟输入,通过时钟选择模块选择需要的时钟,如BUFGMUX,BUFGCTRL or A LUT。但是这些输入的不同时钟间是互斥的,即一个模式只允许一个时钟输入,不同时钟间是没有时序关系,因此只需单独对每个时钟做时序分析即可,添加互斥时钟组可使Vivado进行时序分析时忽略互斥时钟组间的时序路径,约束命令如下:

set_clock_groups -logically_exclusive -group{clk_A} -group {clk_B}

或

set_clock_groups –physically_exclusive -group{clk_A} -group {clk_B}

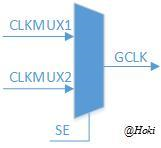

如图2中结构,可将CLKMUX1,CLKMUX2约束成互斥时钟组,约束命令如下:

set_clock_groups - physically_exclusive -group [get_clocks {CLKMUX1}]

-group [get_clocks {CLKMUX2}]

(图2)

442

442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?