敲黑板:set_clock_groups组内会进行时序分析,组间不会进行时序分析!

一、时钟间关系及如何查看

(一)时钟关系

同步时钟: 两个时钟的相位关系是可预知的,常见的是两个时钟来源于相同的根时钟或者共同的周期,如生成时钟和主时钟。

异步时钟:当两个是时钟的相位关系不可预知时,则为异步时钟,例如来源两个晶振的时钟,通过不同的输入端口进入到FPGA内部,无法知道两者的相位关系。

(二)如何查看

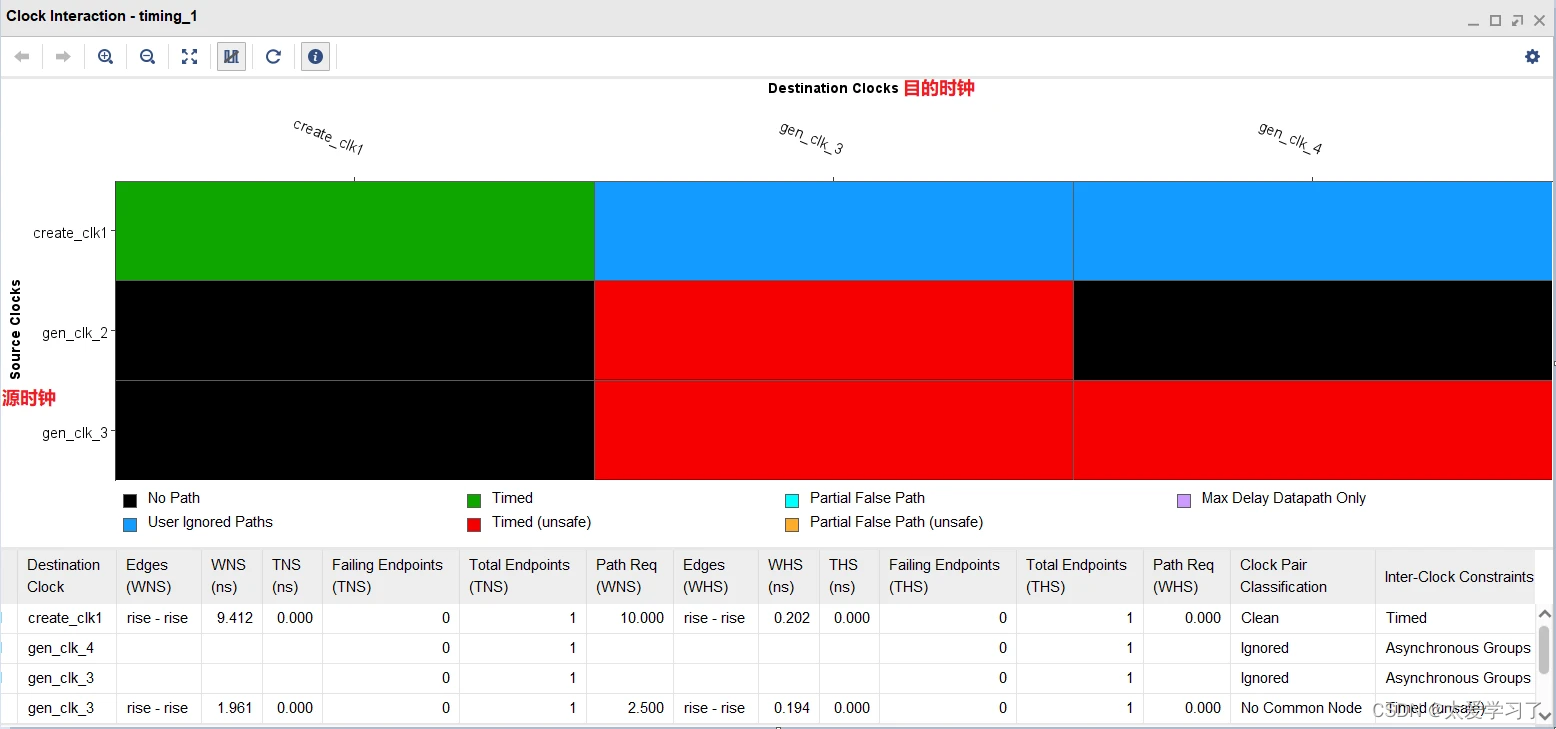

时钟Vivado中Report Clock Interaction可以查看时钟间的关系。

下图颜色方块中,横坐标表示目的时钟,纵坐标表示源时钟,黑色No path表示不存在时序路径,蓝色User ignored Paths为用户设置了不分析的约束,红色Timed(Unsafe)表示异步时钟或非扩展的时钟,颜色块下方的列表也显示了时序的详细信息。

二、时钟约束语句解释

get_clocks [-regexp] [-nocase] [-filter <arg>] [-of_objects <args>]

[-match_style <arg>] [-include_generated_clocks] [-quiet]

[-verbose] [<patterns>]

三、举例

set_clock_groups -name async0 -asynchronous -group [get_clocks -of_objects [get_pins u_rst_clk_top/u_clk_wiz_0/inst/plle2_adv_inst/CLKOUT1]]

set_clock_groups -name async1 -asynchronous -group [get_clocks -include_generated_clocks com_clk]

set_clock_groups -name async2 -asynchronous -group [get_clocks ad_fpga_glblclk_p]

3910

3910

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?