EMC、磁珠、磁环、ESD

1.1概念

EMC-电磁兼容性,是指设备在其电磁环境中符合要求运行并且不对其环境中的任何设备产生无法忍受的电磁干扰的能力。

EMC包括两个方面的要求:

①、设备在正常运行过程中对所在环境产生的电磁干扰不能超过一定的限值

②、设备对所在环境中存在的电磁干扰具有一定程度的抗扰度

1.2三要素

电磁强扰源

任何形式的自然或电能装置所发射的电磁能量,能使共享同一环境的人或其它生物受到伤害,或使其它设备、分系统或系统发生电磁危害,导致性能降低或失效,即称为电磁强扰源。

耦合途径

即传输电磁强扰的通路或媒介。

敏感设备

是指当受到电磁强扰源所发射的电磁量的作用时,会受到伤害的人或其它生物,以及会发生电磁危害,导致性能降低或失效的器件、设备、分系统或系统。许多器件、设备、分系统或系统可以既是电磁骚扰源又是敏感设备。

电磁强扰源产生的电磁强扰通过耦合途径,传输给敏感设备,即造成电磁强扰。

1.3各类信号频谱

重要知识:

时域:电压信号随时间变化曲线图,代表仪器为示波器

频域:谐波幅度随频率变化曲线图,代表仪器为频谱仪

2.磁珠

2.1概念

磁珠,英文 Ferrite bead,缩写 FB,中文全称为铁氧体磁珠滤波器。是一种电感型EMI静噪滤波器。

磁珠对高频信号具有较高的阻碍作用,专用于抑制信号线、电源线上的高频噪声和尖峰干扰,还具有吸收静电脉冲的能力。一句话:消除传输线结构(电路)的噪声。吸收噪声并转换为热能。

2.2选型

阻抗

标称阻抗 100R@100MHz,指的是在100MHz频率下,磁珠的阻抗是100R。

阻抗越大,抑制噪声的效果越好。

不同的信号经过磁珠时,表现的阻抗不同,选型时,通过示波器测量干扰频率,再选择此干扰频率下,阻抗较高的磁珠。

DCR

特别是磁珠用于电源线时DCR会导致电源线上的压降。比如3.3V电源,如果电流1A,DCR超过0.3欧时,压降会超过0.3V,导致电压低于3V,导致IC工作异常。

通常来说,DRC阻抗越小,封装越大。 DCR一般越小越好,对有用信号的衰减越小。

额定电流(Ir)

指磁珠正常工作时允许的最大电流。

直流重叠特性:当磁珠的温度超过 85℃时,它的额定电流也会急剧下降,因此在使用磁珠时,务必关注磁珠的温度做降额处。超过额定电流20%的直流偏置电流,使用铁氧体磁珠。

2.3磁珠损耗

主要为铁芯损耗,铁芯损耗=磁滞损耗+涡流损耗。

2.4频率特性

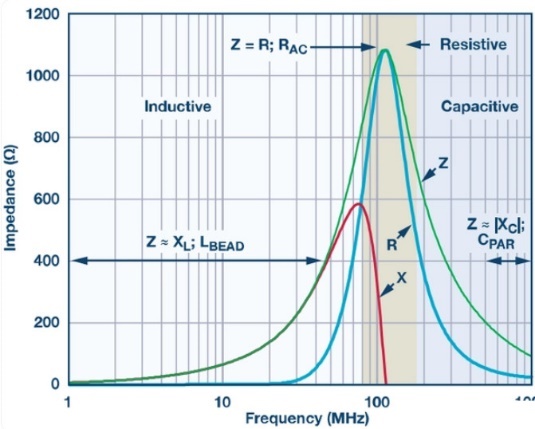

等效为一个电感和一个电阻串联。

当在低频时,磁珠表现为感性,起反射噪声的作用;当在高频时,磁珠表现为阻性,吸收噪声并转变为热能的作用。

2.5应用:

隔离模拟和数字电源

2.6选型

①当用于滤除噪声时,噪声的频带范围要大于转折点的频率,让噪声频带的范围都处于磁珠电阻特性起主要作用的范围内,从而吸收噪声并转化为热能;

②当用于信号滤波时,信号频带的范围要小于转折点的频率,让信号的频带范围落于磁珠感性作用的范围内,从而减少信号的衰减。

磁珠和电感区别

磁珠,能量转换(消耗)器件,多用于信号回路,消耗高频能量,抑制高频噪声,降低EMI辐射值。某一些高频电路如RF、振荡电路、DDR SDRAM等都需要在电源输入部分加磁珠。

电感,储能元件,多用于电源滤波回路,主要解决传导干扰问题。高频电感主要用于中低频滤波电路,功率电感主要用DC-DC电路中。

滤波区别

电感的滤波是反射式滤波。电感滤波将电能转换为磁能,磁能通过两种方式影响电路,一种是重新转换成电能,表现为噪声,另一种方式为向外部辐射,表现为 EMI。

磁珠是将电能转换为热能,不会对电路产生二次干扰。

电容滤波属电压滤波,是直接储存脉动电压来平滑输出电压:输出电压高,接近交流电压峰值:适用于小电流,电流越小滤波效果越好。电容的频率和阻抗成反比,电容通高频。

器件直流电阻不同

同样级别的器件,磁珠的直流电阻要小于电感的直流电阻,因而磁珠的压降也小于电感的压降。

滤波的频率范围不同

电感应用于不超过50MHz的低频段,磁珠利用电阻特性吸收高频噪声。

3.磁环

磁环,又称铁氧体磁环。它是电子电路中常用的抗干扰元件,对于高频噪声有很好的抑制作用,一般使用铁氧体材料(Mn-Zn)制成。磁环在不同的频率下有不同的阻抗特性,一般在低频时阻抗很小,当信号频率升高磁环表现的阻抗急剧升高。

3.1选型

阻抗

不同的信号经过磁环时,表现的阻抗不同,选型时,通过示波器测量干扰频率,再选择此干扰频率下,阻抗较高的磁环。

尺寸

磁环通过用于导线,选用的尺寸,确保导线可以穿过,此外,尺寸也符合符合结构要求。

4.EMC优化

如果产品做好了,经过测试超标,测试需要进行优化,从3个方向考虑:

1、干扰源

①对于BUCK.BOOST等功率环路引起的干扰,PCB设计时尽量减小环路,另外,可以选择开关频率较低的IC,比如MP2451的开关频率2M,而MP1584可以设置为100k,频率低,EMC会好些。

②满足要求的情况下,尽量降低系统时钟频率,也可以充分利用时钟电路的倍频器。比如系统时钟72M,采用8M×9倍频或4M*18倍频。

2、耦合路径

对于高速电路,可以使用屏蔽罩,阻断路径。

对于导线,可以使用磁环。

3、设备

尽量远离干扰源

5.静电放电

静电放电ESD产生原理:

具有不同静电电位的物体由于直接接触或静电感应所引起的物体之间静电电荷的转移(Electro-Static-Discharge),通常指在静电场的能量达到一定程度之后,击穿其间介质而进行放电的现象。

7309

7309

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?