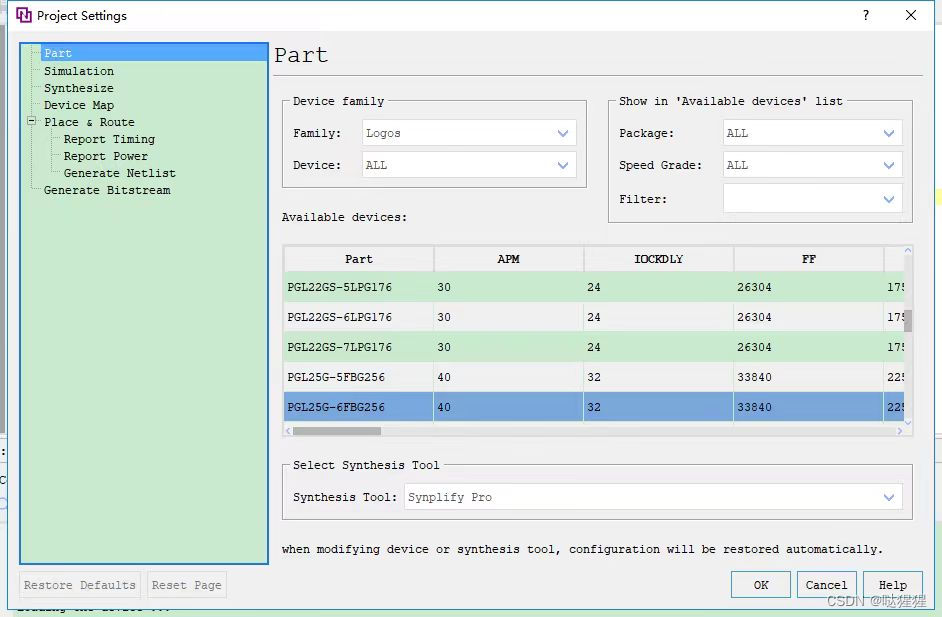

最近使用紫光的PDS移植代码时遇到了引脚分配的问题,简单分享一下,本次使用的软件版本为Pango Design Suite 2022.2 - SP2,由于工程中含有VHDL文件,所以综合工具只能选择Synplify Pro,如果选择自带的ADS,综合时会报错,好像2023.2之后的版本ADS才支持综合VHDL文件。

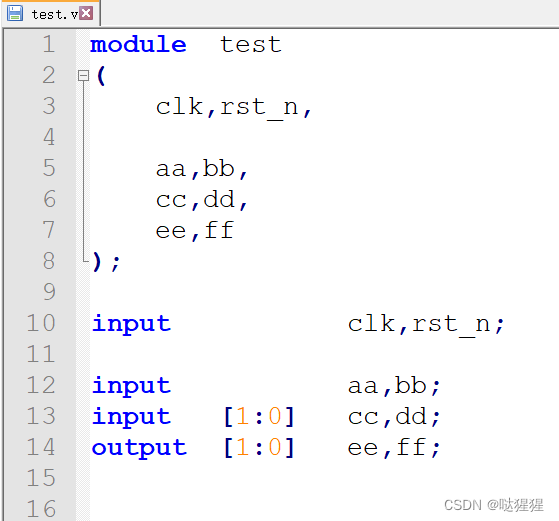

新建完工程后,添加源文件,打开UCE,发现顶层定义多位宽的端口一个也没有,在I/O分配界面只有单位宽的信号,没有多位宽的信号,刚开始怀疑是综合工具把一些没有使用的端口信号给优化掉了,所以在顶层一些怀疑被优化的信号后面增加防止综合被优化的语句(/* synthesis syn_keep=1 */),但是发现没有作用,接着做了一些其它尝试,重新加载顶层文件,重新创建工程,均没有效果。其中一些多位宽信号直接通过assign直接赋值,还是在UCE中没有该端口,接着进行布局布线后,在report summary中查看IO report,而该界面是有所有端口信号的,说明软件是识别到了所有端口,但是在UCE中不显示,同时如果在生成的.fdc文件直接写约束语句,发现在IO report中该端口被使用,说明可以通过在.fdc写约束语句约束多位宽IO,但该方式有些繁琐。之后在各种尝试中找到了解决方法,修改顶层端口定义的写法,本来端口定义是如下图所示的:

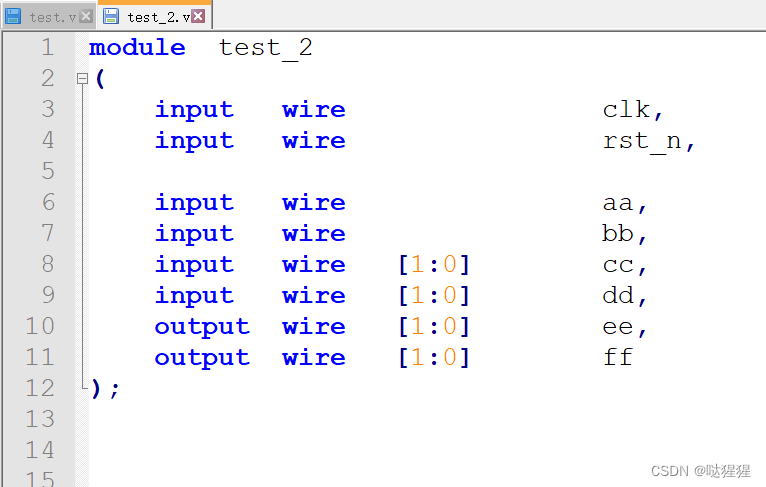

修改之后,改为如下所示:

顶层端口定义由Verilog-1995标准改为Verilog-2001标准后,UCE中显示所有的端口信号,均可分配。虽然问题解决了,但是不知道具体原因,感觉应该是软件Bug。

2199

2199

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?