参考博客:

https://zhuanlan.zhihu.com/p/95751537

这是我人生的第一个blog,从现在开始记录遇到的技术问题!

这个项目是我的本科毕设,途中遇到了很多问题,但最后也还算完成,感谢xw学长对我的耐心帮助,这个log记录一下整个过程中遇到的问题。

开发板 : ZYNQ 7010.

平台 : Vivado和Vitis(standalone).

一.动态部分重构

这一部分直接跟着赛灵思官方文档UG947完成。Vivado 2022.2版已经把原来Dynamic Partial Reconfiguration改成了Dynamic Function Exchange(DFX),但是大体的流程不变。具体是参照lab3做的,还是图形界面比较得我心意,TCL命令操作我无能为力。

安装Vivado的时候在网上找了许可证,但是软件一直不能正确读取,后面发现是因为license文件放在了带有中文名的文件下。悔不当初高三拿到电脑的时候给自己设了一个中文用户名,痛了我整整四年。把lic直接放在D盘之后就好了。

在DFX流程中,从综合到生成比特流的这个过程,需要手动给重构模块绑定物理约束划分PBLOCK,因为我本人对FPGA开发和Zynq非常小白,对硬件完全不熟悉,所以画PBLOCK的时候非常简单粗暴画得很大,最后能用就行。我是手工在图形界面画的,也可以直接在XDC文件添加约束。手工画PBLOCK要注意不能把PLOCK的边界画在背靠背的成对资源上(学长是这么说的我有点不理解这是啥意思,大概就是那种对称的资源要划到一起去),否则会出现报错。

绑定时钟引脚的时候一定要注意绑定到相应的管脚,不然重构也不能成功,这是我的血泪教训。

二.PS与PL交互

这一部分应该是问题最多的。

由于我的系统架构中需要实现PS与PL的交互,因此自定义了PL的带AXI协议的从机IP,然后需要修改自定义IP的Verilog代码。修改的时候犯了大错,把IP自带的读写部分删掉了,导致后续跑重配程序的时候Done灯亮但是没有相应的LED灯响应,然后在这一部分卡了很久都找不到原因,后面发现了之后加回来就可以正常运行了。

另外,经过十多次实验,我发现修改IP核硬件配置并不会改变动态模块的部分比特流文件,只要不改这一部分的物理约束和引脚,部分比特流文件可以用到老,哈哈。

三.PS重配PL

重配采用的是PCAP处理器访问实现,代码是官方的xdevcfg_roll例程,用这个就可以直接完成一个完成的重配过程,具体的代码可以看注释配合UG585的6.4节理解。

由于想把部分比特流存在DDR中,NON-CABLE配置需要用bin文件。Vivado在完整流程中生成的bin文件不能用于PS重配,需要加相关的头文件和约束,需要采用命令行实现,并且只能用这一方式生成需要的bin文件。我用notepad看过两种方式生成的bin文件,是有很大区别的。

write_cfgmem -format bin -loadbit “up 0x0 filename.bit” -file filename.bin -size 128 -force -interface SMAPx32 -disablebitswap在运行软件时的配置,需要取消勾选reset entire system和program system,不然会出现每次运行软件都重启ARM核然后用XSA文件自带的比特流对PL编码的过程。

在Vitis裸机运行程序的时候,需要先bulid project。在这个过程中,由于我的硬件有自定义IP核Vitis不能创建platform导致工程一直out of date,make时编译会出现如下的报错。

make[2]: *** [Makefile:18: libs] Error 1

make[1]: *** [Makefile:46: ps7_cortexa9_0/libsrc/ps_r_pl_v1_0/src/make.libs] Error 2

make : *** [Makefile:18: all] Error 2这是因为我自定义了IP核,需要修改自定义IP核的makefile文件。感谢学长救我狗命,学长之前也出现过这种问题,参考了学长给的博客:

修改之后就可以正常Build了。

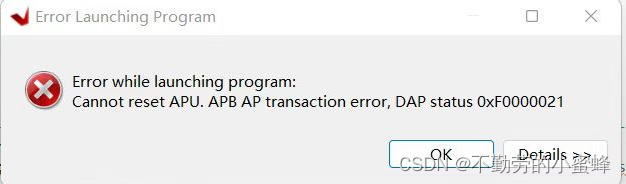

接下来遇到了这个问题。造成这个error的原因可能是因为硬件配置有问题,需要检查PS IP核配置的时候的DDR型号。但是我们检查更换之后还是有这个问题不能解决。后面发现重启电脑再打开VITIS就没有这个问题了,但是每次只能跑一次,第二次Launch program又出现这个问题了,于是我们又重启重启再重启,后面修改了自定义IP之后又莫名其妙好了,总之就是一个很莫名其妙的过程。

检测PS重配时间用的是C语言的时间函数XTime_GetTime。因为是毫秒级的时间,用了很多函数跑出来都是0即使运行十万次也没有一个tiktock的时间哈哈,最后找了很久才发现这个函数能用,那就凑合用吧。测量的时候依然把程序跑了一万次,测得的重构时间约为90ms。有学姐用ICAP做重构只要500us,慢了180倍。不过她把部分比特流存在PL块上BRAM,一个BRAM只有36KB,DDR有512MB,能够存更大的,也不用额外写硬件ICAP控制器,整体过程我觉得还是比ICAP要简单很多的。PCAP真的很方便,直接用软件跑就行,不过这个软硬件交互的过程会出现很多bug,也是很头疼啊。

四.心得体会

感觉我的本科真的很失败,但是我发现做PJ才是真正学习知识和实践的过程,以后也继续加油做PJ吧!

做这个PJ读了Xilinx的用户手册不下20篇,现在看英文文档已经很适应没那么抗拒了,果然还是得多练。并且在这个过程中进一步掌握了Verilog,感觉现在写电路已经不是一件很痛苦的事情了。

另外,赛灵思的官方论坛真的很好用。虽然没有收到最正确的解决方案,但是官方的技术人员回消息的效率真的很高!感谢我在论坛上找到的一位和我遇到相同问题的学长的无私解答。

研究生加油嘿嘿!毕业快乐!

3802

3802

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?