1、通过时钟相或实现奇数分频

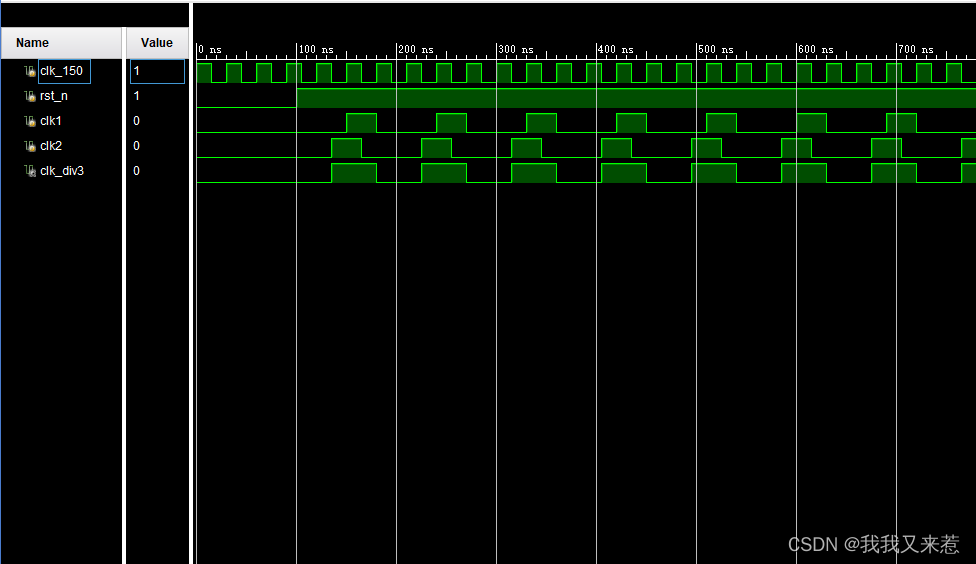

原时钟clk通过上升沿和下降沿计数产生时钟clk1和clk2,clk1和clk2相或产生clk三分频的clk_div3时钟。

clk1:原时钟clk的上升沿产生。

clk2:原时钟clk的下降沿产生。

clk1和clk2的特征:

3分频——高电 : 低电平 = 1 : 2

2N+1分频——高电 : 低电平 = N : N+1

代码:

`timescale 1ns/1ns

module test(

input clk_150 ,

input rst_n ,

output clk_div3

);

reg [3:0] cnt_1; //上升沿计数

reg [3:0] cnt_2; //下降沿计数

reg clk1;

reg clk2;

assign clk_div3 = clk1 | clk2;

always@(posedge clk_150 or negedge rst_n)

begin

if (!rst_n)

cnt_1 <= 4'd0;

else

cnt_1 <= (cnt_1 == 4'd2) ? 4'd0 : cnt_1 + 4'd1;

end

always@(posedge clk_150 or negedge rst_n)

begin

if (!rst_n)

clk1 <= 1'b0;

else

clk1 <= (cnt_1 == 4'd1) ? 1'b1 : 1'b0;

end

always@(negedge clk_150 or negedge rst_n)

begin

if (!rst_n)

cnt_2 <= 4'd0;

else

cnt_2 <= (cnt_2 == 4'd2) ? 4'd0 : cnt_2 + 4'd1;

end

always@(negedge clk_150 or negedge rst_n)

begin

if (!rst_n)

clk2 <= 1'b0;

else

clk2 <= (cnt_2 == 4'd1) ? 1'b1 : 1'b0;

end

endmodule仿真图:

2、通过时钟相与实现奇数分频

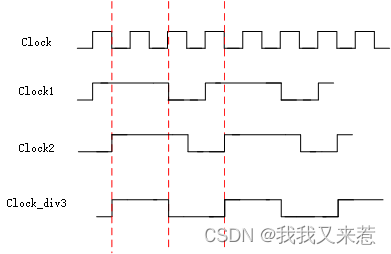

原时钟clk通过上升沿和下降沿计数产生时钟clk1和clk2,clk1和clk2相与产生clk三分频的clk_div3时钟。

clk1:原时钟clk的上升沿产生。

clk2:原时钟clk的下降沿产生。

clk1和clk2的特征:

3分频——高电 : 低电平 = 2 : 1

2N+1分频——高电 : 低电平 = N+1 : N

代码:

`timescale 1ns/1ns

module test(

input clk_150 ,

input rst_n ,

output clk_div3

);

reg [3:0] cnt_1; //上升沿计数

reg [3:0] cnt_2; //下降沿计数

reg clk1;

reg clk2;

assign clk_div3 = clk1 & clk2;

always@(posedge clk_150 or negedge rst_n)

begin

if (!rst_n)

cnt_1 <= 4'd0;

else

cnt_1 <= (cnt_1 == 4'd2) ? 4'd0 : cnt_1 + 4'd1;

end

always@(posedge clk_150 or negedge rst_n)

begin

if (!rst_n)

clk1 <= 1'b0;

else

clk1 <= (cnt_1 <= 4'd1) ? 1'b1 : 1'b0;

end

always@(negedge clk_150 or negedge rst_n)

begin

if (!rst_n)

cnt_2 <= 4'd0;

else

cnt_2 <= (cnt_2 == 4'd2) ? 4'd0 : cnt_2 + 4'd1;

end

always@(negedge clk_150 or negedge rst_n)

begin

if (!rst_n)

clk2 <= 1'b0;

else

clk2 <= (cnt_2 <= 4'd1) ? 1'b1 : 1'b0;

end

endmodule仿真图:

3、通过时钟相异或实现奇数分频

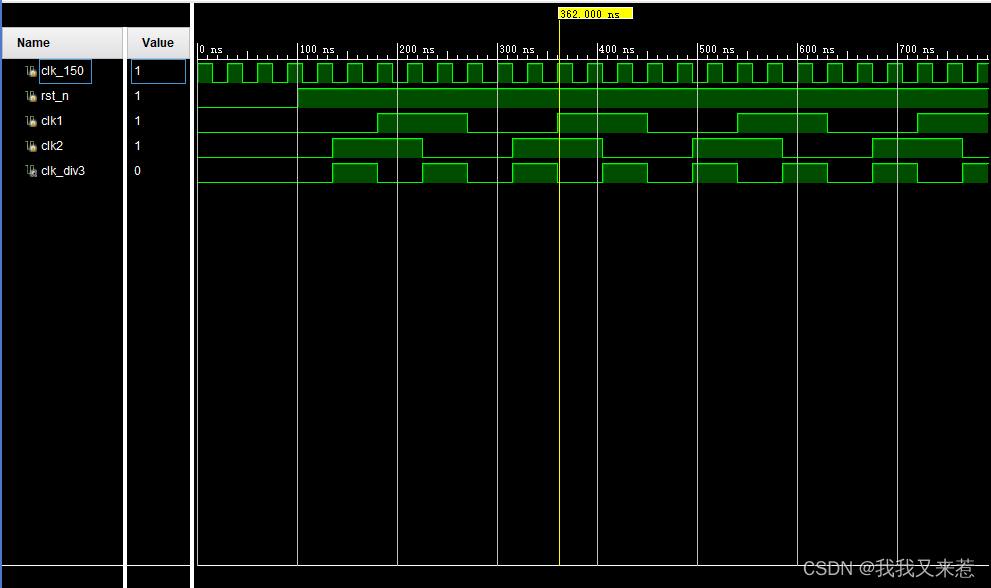

原时钟clk通过上升沿和下降沿计数产生时钟clk1和clk2,clk1和clk2相异或产生clk三分频的clk_div3时钟。

clk1:原时钟clk的上升沿产生。

clk2:原时钟clk的下降沿产生。

clk1和clk2的特征:

3分频:clk1以原时钟clk的3个周期为单位翻转,clk2在clk1时钟的中间点发生翻转。

2N+1分频:clk1以原时钟clk的2N+1个周期为单位翻转,clk2在clk1时钟的中间点发生翻转。

代码:

module test(

input clk_150 ,

input rst_n ,

output clk_div3

);

reg [3:0] cnt_1; //上升沿计数

reg clk1;

reg clk2;

assign clk_div3 = clk1 ^ clk2;

always@(posedge clk_150 or negedge rst_n)

begin

if (!rst_n)

cnt_1 <= 4'd0;

else

cnt_1 <= (cnt_1 == 4'd2) ? 4'd0 : cnt_1 + 4'd1;

end

always@(posedge clk_150 or negedge rst_n)

begin

if (!rst_n)

clk1 <= 1'b0;

else

clk1 <= (cnt_1 == 4'd2) ? ~clk1 : clk1;

end

always@(negedge clk_150 or negedge rst_n)

begin

if (!rst_n)

clk2 <= 1'b0;

else

clk2 <= (cnt_1 == 4'd1) ? ~clk2 : clk2;

end

endmodule仿真图:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?