苦于实现三次样条久已。在参考了两篇博主的文章之后,完成了算法的基本实现。

首先是理论上的推导,参考的是: 三次样条插值算法及推导过程_三次样条计算例子-CSDN博客

其次是Matlab部分的代码,参考的是: 三次样条Cubic Spline简介-CSDN博客

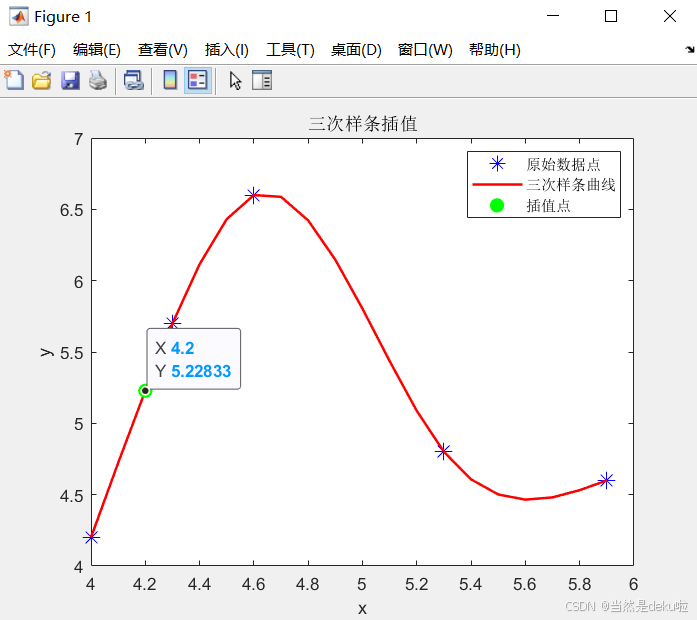

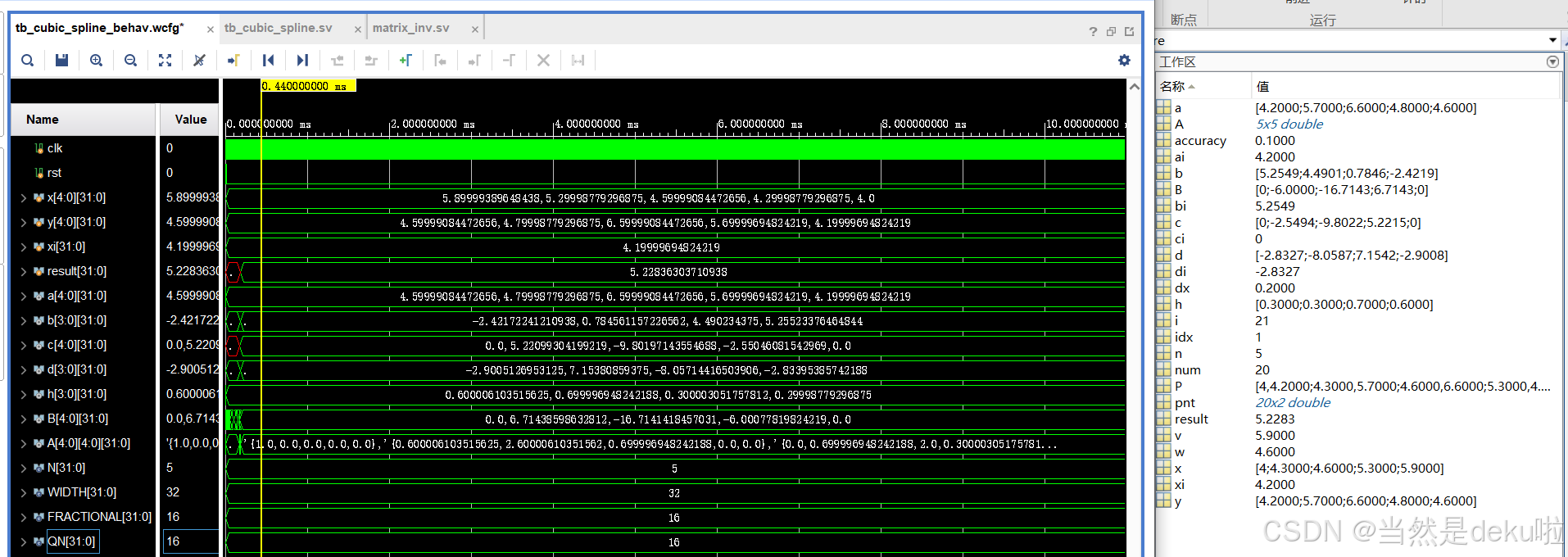

简单地说,就是在已知的几个点中求出分段之间的三次函数。个人认为用到的各个模块(矩阵求逆、高精度乘除法等等)都不是很难,最难的地方应该是误差积累,由于verilog特殊的定点计算方式,使得数据流转的次数越多就会出现越多的误差,所以先是尝试了16位8.8定点格式来算,发现误差巨大,后改为32位16.16的格式,才极大地缓解了这个问题,在这里也是花费了最多的时间,话不多说,直接上Matlab和Verilog的结果对比。

对比中间参数和最后的结果,差误基本可以忽略。

欢迎交流,咸鱼:cllllll28

2217

2217

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?