异步FIFO相比与同步FIFO,其实用性更为广泛,因其可以解决不同时钟域之间的数据传输。

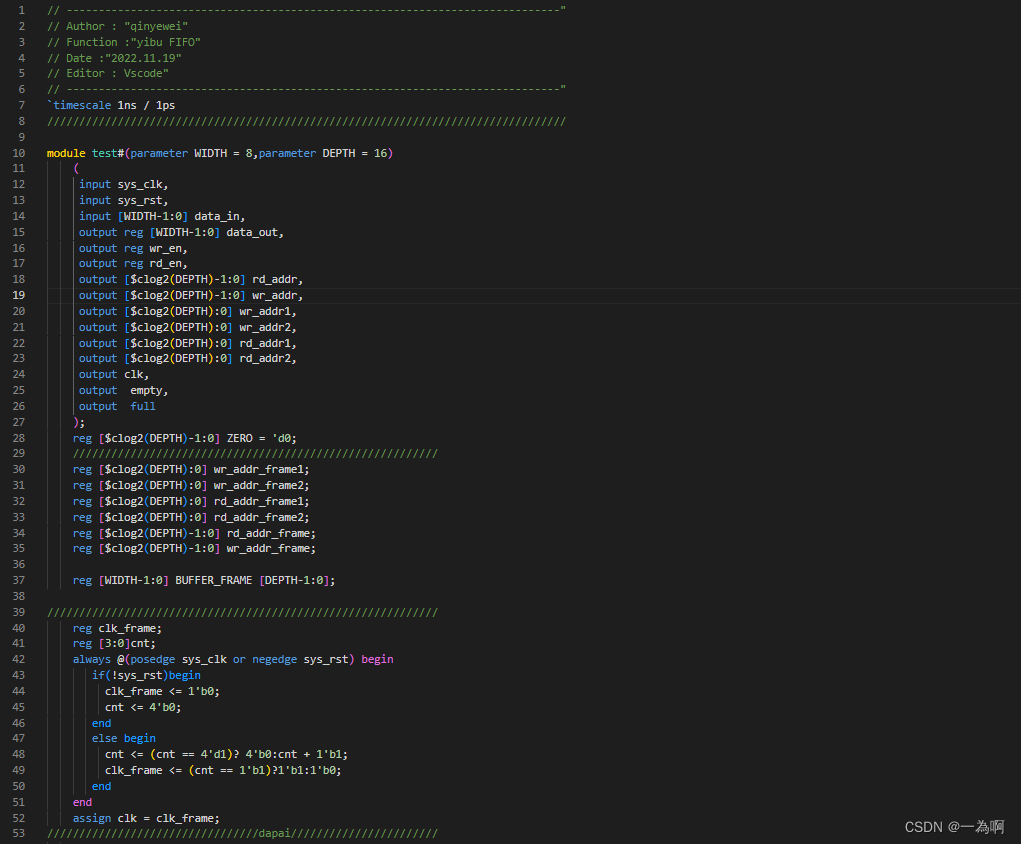

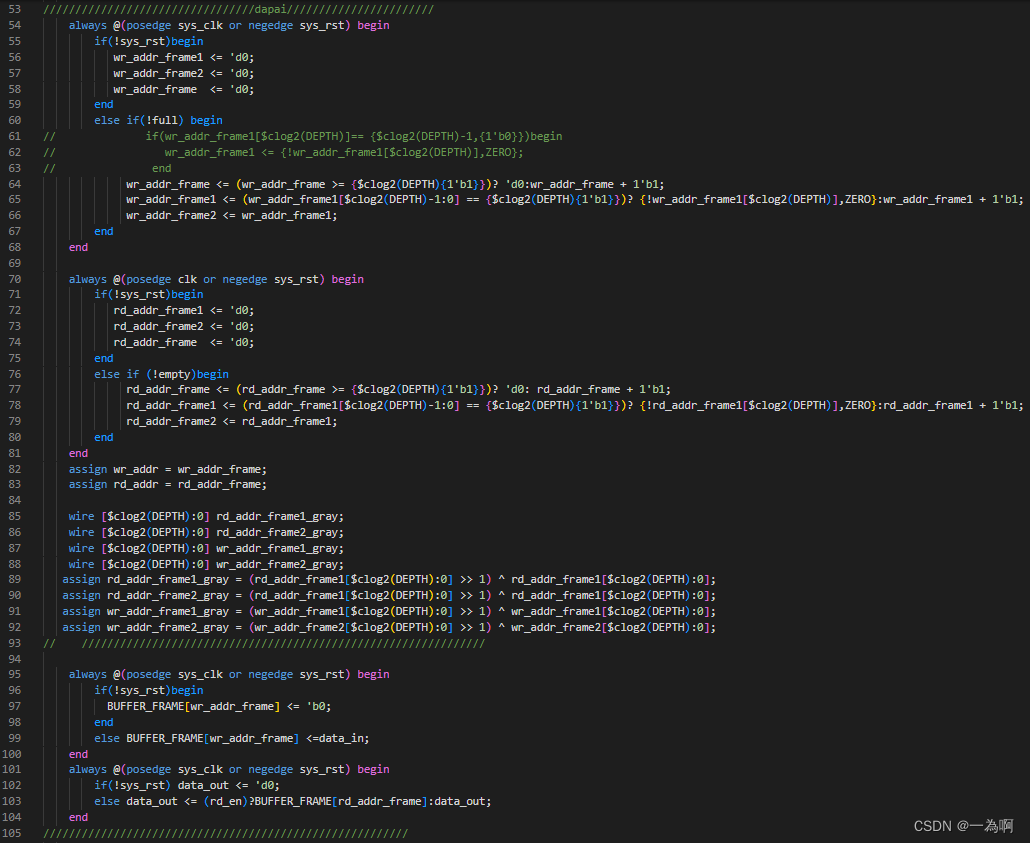

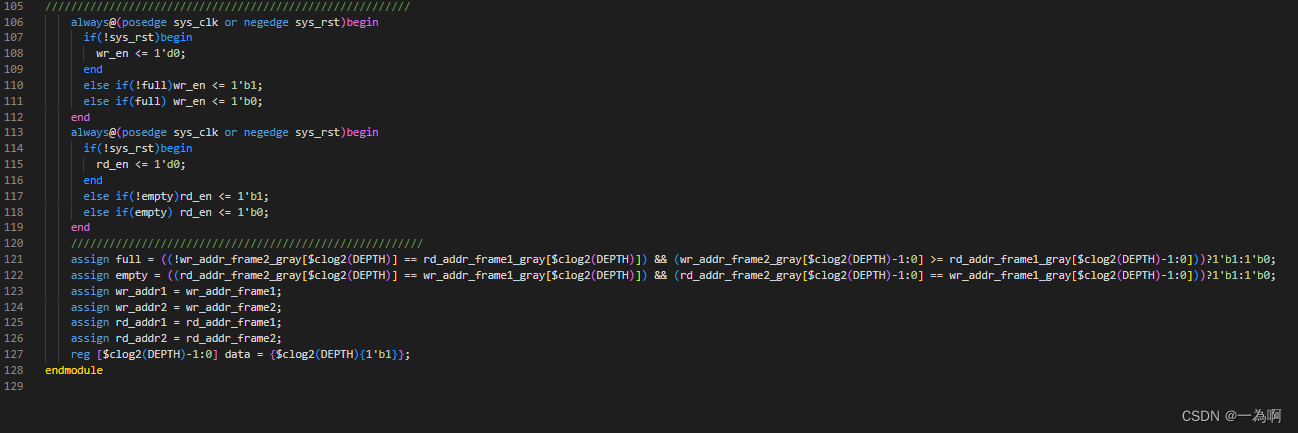

编译代码:

Testbench:

`timescale 1ns / 1ps

module tb_FIFO;

// FIFO Parameters

parameter PERIOD = 10;

parameter WIDTH = 8;

parameter DEPTH = 16;

// FIFO Inputs

reg sys_clk = 0 ;

reg sys_rst = 0 ;

reg [WIDTH-1:0] data_in = 0 ;

// FIFO Outputs

wire [WIDTH-1:0] data_out ;

wire wr_en ;

wire rd_en ;

wire [$clog2(DEPTH)-1:0] rd_addr ;

wire [$clog2(DEPTH)-1:0] wr_addr ;

wire empty ;

wire full ;

wire clk ;

wire [$clog2(DEPTH):0] wr_addr1 ;

wire [$clog2(DEPTH):0] wr_addr2 ;

wire [$clog2(DEPTH):0] rd_addr1 ;

wire [$clog2(DEPTH):0] rd_addr2 ;

initial

begin

forever #(PERIOD/2) sys_clk=~sys_clk;

end

initial

begin

#(PERIOD*2) sys_rst = 1;

end

test u_test (

.sys_clk ( sys_clk ),

.sys_rst ( sys_rst ),

.data_in ( data_in [WIDTH-1:0] ),

.clk ( clk ),

.data_out ( data_out [WIDTH-1:0] ),

.wr_en ( wr_en ),

.rd_en ( rd_en ),

.rd_addr ( rd_addr [$clog2(DEPTH)-1:0] ),

.wr_addr ( wr_addr [$clog2(DEPTH)-1:0] ),

.empty ( empty ),

.full ( full ),

.wr_addr1 ( wr_addr1 [$clog2(DEPTH):0] ),

.wr_addr2 ( wr_addr2 [$clog2(DEPTH):0] ),

.rd_addr1 ( rd_addr1 [$clog2(DEPTH):0] ),

.rd_addr2 ( rd_addr2 [$clog2(DEPTH):0] )

);

initial

begin

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 10101010;

#20

data_in = 8'b 11001010;

#20

data_in = 8'b 01101010;

#20

data_in = 8'b 10001010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101011;

#20

data_in = 8'b 11111111;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 10101010;

#20

data_in = 8'b 11001010;

#20

data_in = 8'b 01101010;

#20

data_in = 8'b 10001010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101011;

#20

data_in = 8'b 11111111;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 10101010;

#20

data_in = 8'b 11001010;

#20

data_in = 8'b 01101010;

#20

data_in = 8'b 10001010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101011;

#20

data_in = 8'b 11111111;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 10101010;

#20

data_in = 8'b 11001010;

#20

data_in = 8'b 01101010;

#20

data_in = 8'b 10001010;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101110;

#20

data_in = 8'b 11101010;

#20

data_in = 8'b 11111010;

#20

data_in = 8'b 11101011;

#20

data_in = 8'b 11111111;

#20

data_in = 8'b 11101010;

$finish;

end

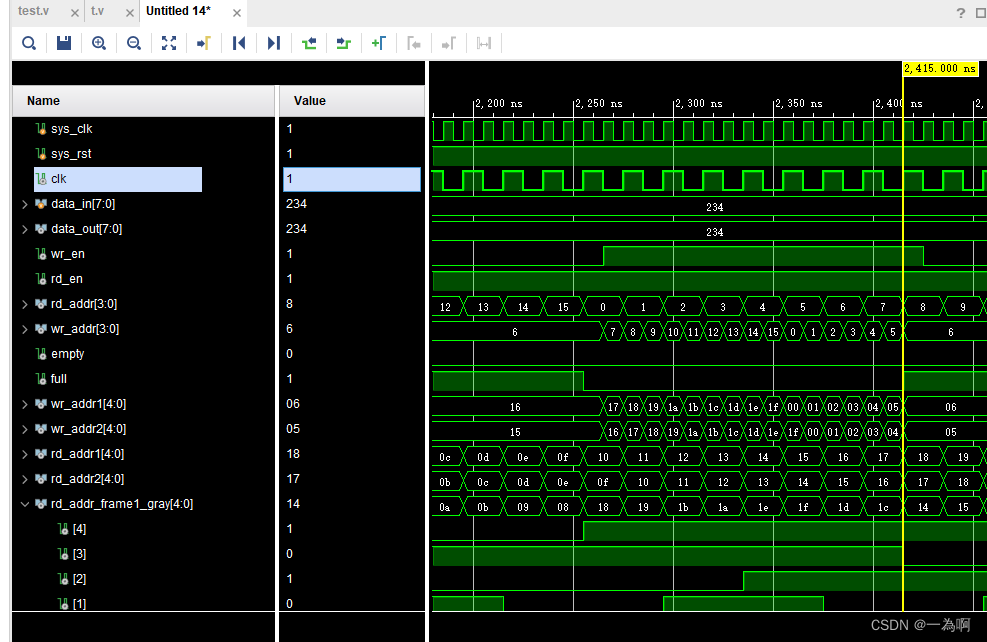

endmodule仿真结果:

总结:读时钟是写时钟的一半,使能信号可根据自己需求进行更改。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?