1、构成

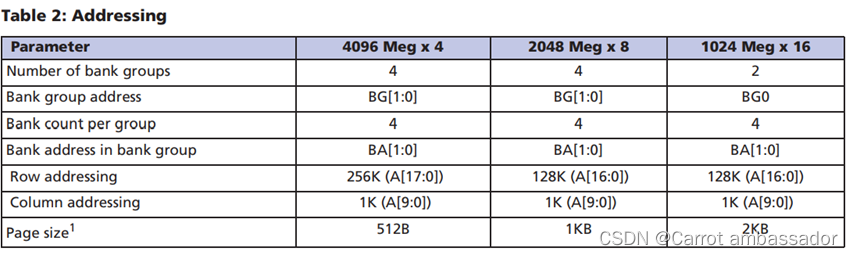

DDR4 SDRAM是一种高速动态随机存取存储器,内部配置为x16bit的8bank DRAM, x4bit和x8bit配置的16bank DRAM。Bank数量根据Bank Group和每个Bank Group中的Bank数量决定。

DDR4 SDRAM采用8n预取架构,实现高速运行。8n预取架构与一个接口相结合,该接口设计为在I/O引脚处每个时钟周期传输两个数据字(时钟上升沿和下降沿各传输一次)。DDR4 SDRAM的单个读或写操作包括在内部DRAM核进行一次8n位宽的四时钟数据传输,以及在I /O pin上进行两次相应的n位宽的半时钟周期数据传输。

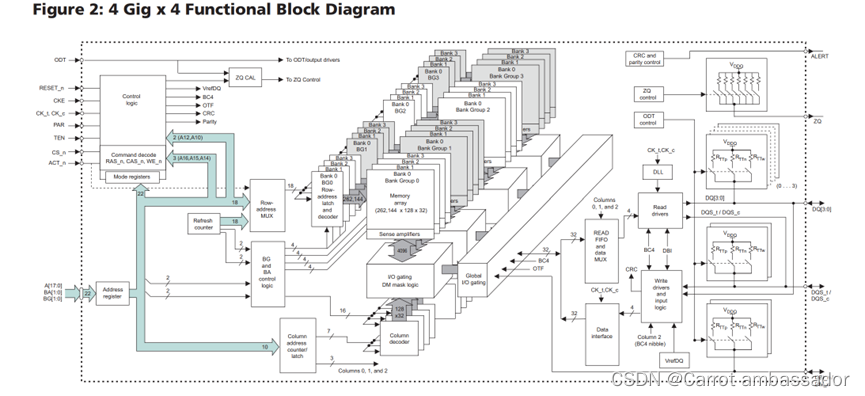

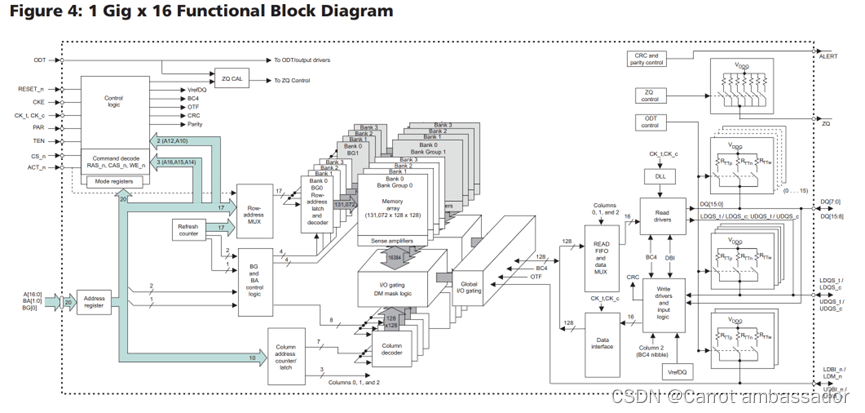

如下图为2GB的DDR4,具有4Gb的深度和4bit的数据位宽。其中有4个Bank Group,每个Bank Group中有4个Bank。其中每个Bank都可以看作是立体结构,行地址宽度为18(2^18=262144),列地址宽度为7(2^7=128),对于每个bank的行列对应的每个地址单元,有3bit的深度,也即2^3=8个地址空间,每个地址中存放4bit的数据(与接口位宽对应)。由此可以算出共有(2^2)*(2^2)*(2^18)*(2^7)*(2^3)=4294967296bit=4Gb的存储空间,再乘以每个存储空间中的4bit数据,也即16Gbit=2GB的存储容量。

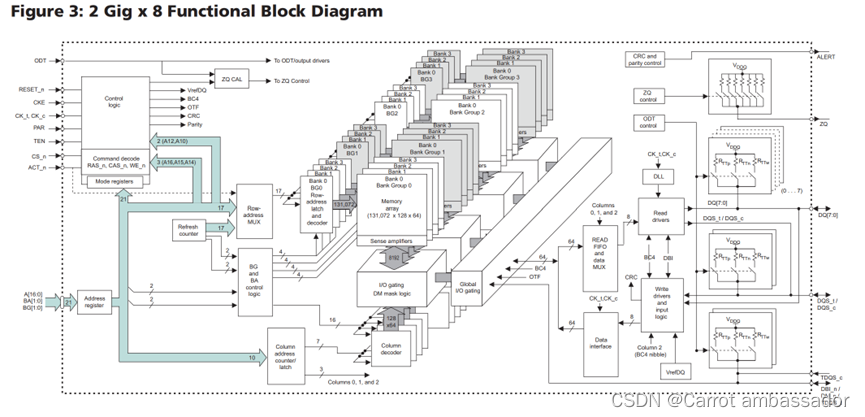

如下图为2GB的DDR4,具有2Gb的深度和8bit的数据位宽。

如下图为2GB的DDR4,具有1Gb的深度和16bit的数据位宽。

2、部分引脚及功能介绍

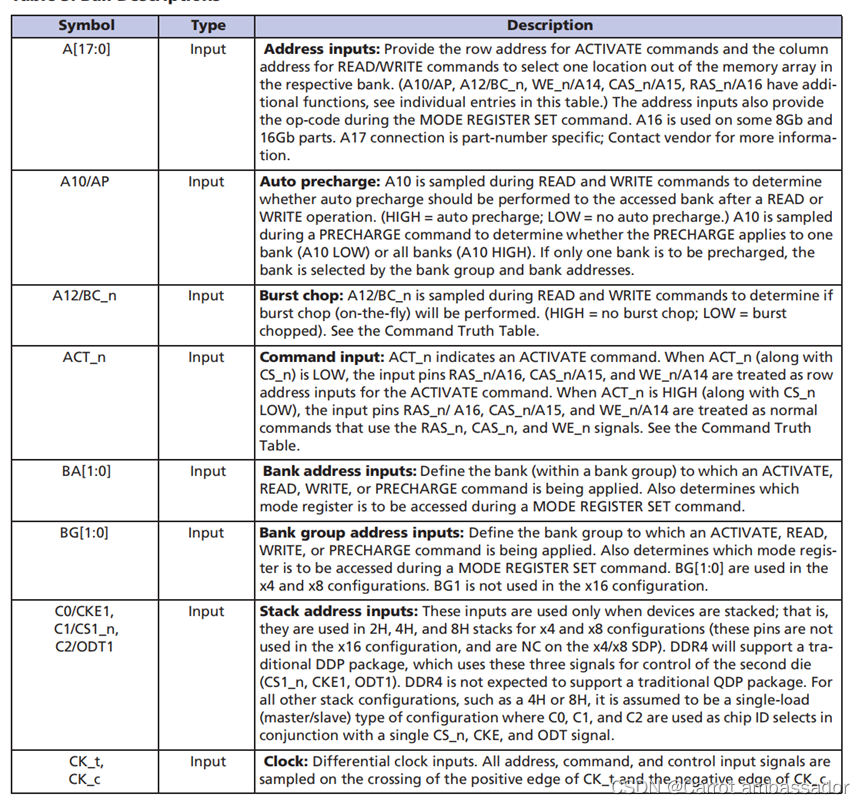

1、地址引脚:

为ACTIVATE命令提供行地址,为READWRITE命令提供列地址,以便从各自BANK的内存数组中选择一个位置。(A10/AP、A12/BC_n、WE_n/A14、CAS_n/A15、RAS_n/A16有附加功能)。地址输入也提供MODE REGISTER SET命令期间的运算码。A16用于一些8Gb和16Gb的部件。A17连接是部件编号特定的。

2、自动充电引脚:

在READ和WRITE命令期间采集A10状态,以确定在READ或WRITE操作后是否应该对被访问的BANK进行自动充电。(HIGH=自动充电;LOW=无自动充电。)在PRECHARGE命令期间对A10进行采样以确定PRECHARGE是适用于一个BANK (A10LOW)还是所有BANK (A10HIGH)。如果只对一个BANK进行充电,则由BG和BA选择该BANK。

注:由于SDRAM的特殊结构,是通过电容的充放电及电荷的存储来储存数据,但是由于漏电流等原因,需要定期的对电容进行充电,避免数据丢失。

3、burst chop:

在READ和WRITE命令期间采样A12/BC n以确定是否将执行burst chop(即时)。(HIGH =无burst chop;LoW =burst chop)。

4、ACT_n命令输入:

“ACT_n”表示ACTIVATE命令。当ACT_n(连同CS_n)为LOW时,输入引脚RAS_n/A16、CAS_n/A15和WE_n/A14被视为ACTIVATE命令的行地址输入。当ACT_n为HIGH(连同CS_n为LoW)时,输入引脚RAS_n/ A16、CAS_n/A15和WE_n/A14被视为使用RAS_n、CAS_n和WE_n信号的正常命令。

5、BA:BANK地址;

6、BG:BANK GROUP地址;

7、堆栈地址输入:

这些输入仅在设备堆叠时使用;也就是说,它们在x4和x8配置的2H, 4H和8H堆栈中使用(这些引脚在x16配置中不使用,并且在x4/x8 SDP上是NC的)。DDR4将支持传统的DDP封装,它使用这三个信号来控制第二个die (CS1_n, CKE1, ODT1)。DDR4不支持传统的QDP包。对于所有其他堆栈配置,例如4H或8H,假设它是单负载(主/从)类型的配置,其中CO, C1和C2被用作芯片ID选择,并与单个CS_n, CKE和ODT信号一起使用。

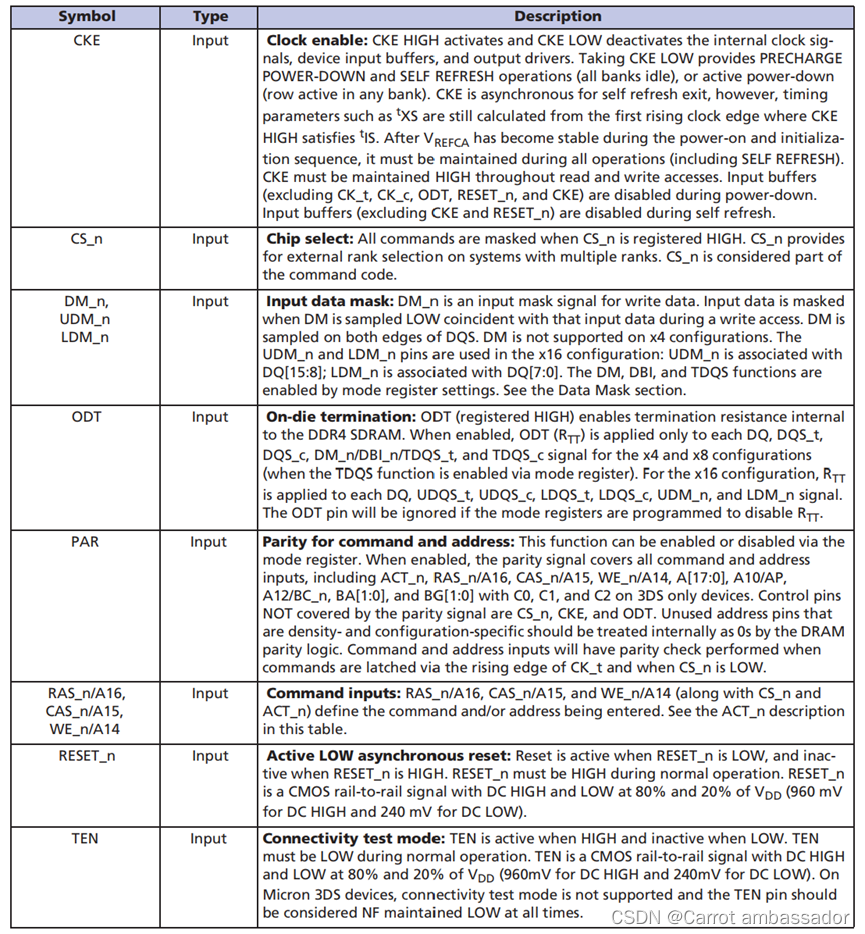

8、时钟:

差分时钟输入。所有的地址、命令和控制输入信号在CK_t的正沿和CK_c的负沿的交叉处采样。

9、片上端接:

ODT(寄存器为高)使DDR4 SDRAM内部的终止电阻成为可能。当启用时,ODT (Rtt)仅应用于x4和x8配置的每个DQ、DQS_t、DQS_c、DM_n/DBI_n/TDQS_t和TDQS_c信号(当TDQS功能通过模式寄存器启用时)。对于x16配置,Rtt应用于每个DQ、UDQS_t、UDQS_c、LDQS_t、LDQS_c、UDM_n和LDM_n信号。如果模式寄存器被编程为禁用Rtt,则ODT引脚将被忽略。

注:信号到达线路末端的时候,波形会有反射,从而影响到信号的完整性;因此需要加上终端电阻,进行阻抗匹配。以前的DDR端接电阻做在板子上,但是因为工艺及PCB空间限制等种种原因,效果不是太好,到了DDR2,把端接电阻做到了DDR颗粒内部,也就称为On Die Termination,( Die是硅片的意思,这里也就是DDR颗粒)。使用ODT的目的是为了让DQS、RDQS、DQ和DM信号的阻抗匹配,防止这些信号在电路上形成反射,进而增强信号完整性。

正常使用该功能时,DDR需要在ZQ引脚外接一个精度较高的参考电阻,以作为内部端接调整的基准,通常该电阻为1%精度的240Ω电阻。

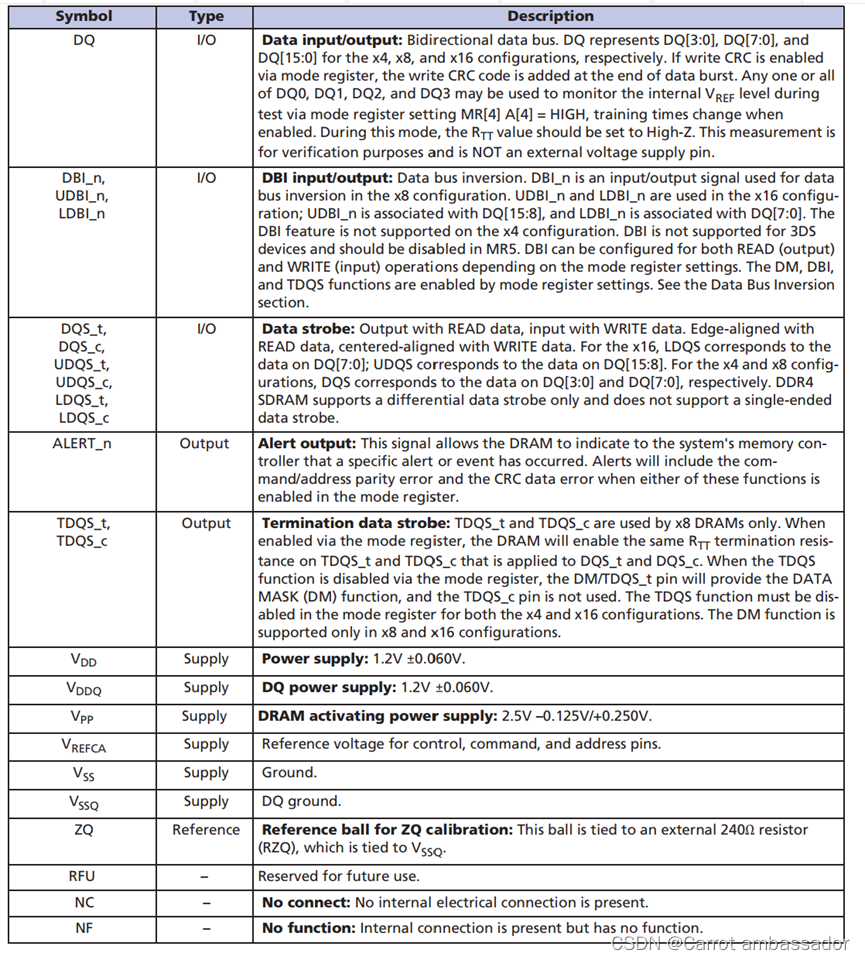

10、DBI引脚:

数据总线翻转功能,这个功能在8bit和16bit的DDR上用的比较多,4bit的DDR不支持该功能也没必要;

注:数据翻转功能主要应用于数据跳变比较大的场景,比如前一个数据传输的是2’b1000 0000,下一个数据需要传输2’b1111 1111,通过对比可以看出如果是常规操作则在数据传输时,数据线中有7个数据需要翻转。由于DDR的速率比较高,正常都在2000MT/s以上,过多的数据翻转,容易引起较大的串扰,造成误码率升高,因此引入了数据翻转功能。在此情况下,DDR或者主控经过判断,需要翻转的数据位数超过了规定值(比如4),此时应该开启数据翻转功能,也就是将DBI信号置位。2’b1111 1111因为要传输翻转后的数据,所以实际传输的数据位2’b0000 0000,这样对比前一次传输的数据2’b1000 0000,只需要将最高位翻转就可以了。因为DQR传输的接口位宽比较高,这个功能在QDR中应用比较普遍。

想到什么了再补充吧,内容会有点多,需要结合控制器;

207

207

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?