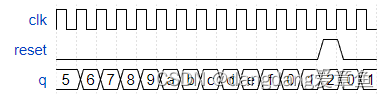

Count15

创建一个位宽为4 的二进制计数器计数从0到15,周期为16,复位信号是同步的,复位为0

代码如下:

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always @(posedge clk)begin

if(reset)

q <= 4'd0;

else if(q == 4'd15)//计数满16位归零

q <= 4'd0;

else

q <= q + 4'd1;

end

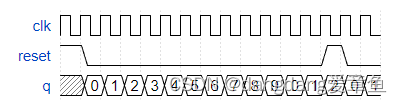

endmoduleCount10

构建一个从 0 到 9(包括 0 和 9)的十进制计数器,周期为 10。复位输入是同步的,应将计数器复位为 0。

代码如下:

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always @(posedge clk)begin

if(reset)

q <= 4'd0;

else if(q == 4'd9)

q <= 4'd0;

else

q <= q + 4'd1;

end

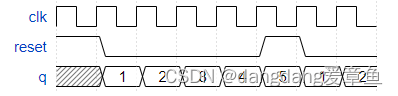

endmoduleCount1to10

制作一个计数为 1 到 10(包括 1 和 10)的十进制计数器。复位输入是同步的,应将计数器复位为 1。

代码如下:

module top_module (

input clk,

input reset,

output [3:0] q);

always @(posedge clk)begin

if(reset)

q <= 4'd1;

else if(q == 4'd10)

q <= 4'd1;

else

q <= q + 4'd1;

end

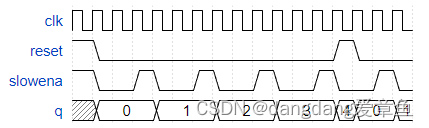

endmoduleCountslow

构建一个从 0 到 9(包括 0 和 9)的十进制计数器,周期为 10。复位输入是同步的,应将计数器复位为 0。我们希望能够暂停计数器,而不是总是增加每个时钟周期,因此slowena输入指示计数器何时应递增。

代码如下:

module top_module (

input clk,

input slowena,

input reset,

output [3:0] q);

//首先判断复位信号是否为0,如果是0则再判断使能信号是否为0

//如果非0则判断q的值是否计满,如果计满则重置为0,未计满则加1

always @(posedge clk)begin

if(reset)

q <= 4'd0;

else if(slowena)

if(q == 4'd9)

q <= 4'd0;

else

q <= q + 4'd1;

else

q <= q;

end

endmoduleExams/ece241 2014 q7a

设计具有以下输入和输出的1-12 计数器:

Reset同步高电平有效复位,强制计数器为1

enable设置为高以使计数器运行

clk正边沿触发时钟输入

Q[3:0]计数器的输出

c_enable, c_load, c_d[3:0]控制信号进入提供的4位计数器,因此可以验证操作是否正确。

用4位二进制计数器(Count4),负载信号优先级高于是能信号;

代码如下:

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

); //

assign c_enable = enable;

assign c_load = (Q == 4'd12 && enable) || reset ? 1'b1:1'b0;

//计满或者复位信号非0时进行置1的操作

assign c_d = 4'd1;

count4 the_counter (clk, c_enable, c_load, c_d , Q);

endmoduleExams/ece241 2014 q7b

从 1000 Hz 时钟中,导出一个 1 Hz 信号,称为OneHertz,可用于驱动一组小时/分钟/秒计数器的使能信号以创建数字挂钟。由于我们希望时钟每秒计数一次,因此必须每秒正好对OneHertz信号进行一个周期的置位。使用模 10 (BCD) 计数器和尽可能少的其他门构建分频器。同时从您使用的每个 BCD 计数器输出使能信号(最快的计数器c_enable[0],最慢的计数器c_enable[2])。

为您提供了以下 BCD 计数器。启用必须为高电平,计数器才能运行。复位是同步的,并设置为高以强制计数器为零。电路中的所有计数器必须直接使用相同的 1000 Hz 信号。

代码如下:

module top_module (

input clk,

input reset,

output OneHertz,

output [2:0] c_enable

); //

wire [11:0] Q;

//使用BCD计数器来计数,每个十进制数字用4位进行编码,最终输出1赫兹的信号

assign c_enable[0] = 1'b1;//计数加1部分

assign c_enable[1] = (Q[3:0] == 4'h9);//输出Q最低的4位代表十位,如果计满就向前进1

assign c_enable[2] = (Q[7:0] == 8'h99);

assign OneHertz = (Q[11:0] == 12'h999);

bcdcount counter0 (clk, reset, c_enable[0], Q[3:0]);

bcdcount counter1 (clk, reset, c_enable[1], Q[7:4]);

bcdcount counter2 (clk, reset, c_enable[2], Q[11:8]);

endmoduleCountbcd

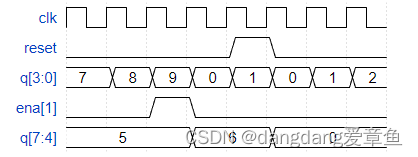

生成 4 位 BCD(二进制编码十进制)计数器。每个十进制数字使用 4 位进行编码:q[3:0] 是个位,q[7:4] 是十位,依此类推。对于数字 [3:1],还要输出一个使能信号,指示何时应递增前三位数字中的每一个。

代码如下:

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

BCD_cnt counter0 (clk, reset, 1'b1, q[3:0]);

BCD_cnt counter1 (clk, reset,ena[1], q[7:4]);

BCD_cnt counter2 (clk, reset, ena[2], q[11:8]);

BCD_cnt counter3 (clk, reset, ena[3], q[15:12]);

assign ena[3:1] = {(q[11:0]==12'h999),(q[7:0] == 8'h99),(q[3:0] == 4'h9)};

endmodule

module BCD_cnt(

input clk,

input reset,

input ena,

output [3:0] q);

always @(posedge clk)

if(reset)

q <= 4'h0;

else if(ena)

q <= (q == 4'h9) ? 4'h0:q+4'h1;

else

q <= q;

endmoduleCount clock

创建一组适合用作 12 小时制的计数器(带 am/pm 指示器)。您的计数器由一个快速运行的clk 计时,只要您的时钟增加(即每秒一次),ena就会有一个脉冲。

重置会将时钟重置为上午 12:00。pm对于 AM,为 0,对于 PM.hh,mm 为 1,ss是两个BCD(二进制编码十进制)数字,分别表示小时 (01-12)、分钟 (00-59) 和秒 (00-59)。重置的优先级高于启用,即使未启用,也可能发生。

以下时序图显示了从上午11:59:59 到下午 12:00:00的翻转行为以及同步复位和启用行为。

代码如下:

module top_module(

input clk,

input reset,

input ena,

output pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

always@(posedge clk )

if (reset) ss <= 8'h00;

else if(ena) begin

if(ss == 8'h59)

ss <= 8'h00;

else begin

if(ss[3:0] < 4'h9)

ss[3:0] <= ss[3:0] + 1'h1;

else

begin

ss[3:0] <= 0;

ss[7:4] <= ss[7:4] + 1'h1;

end

end

end

always@(posedge clk)

if (reset) mm <= 8'h00;

else if(ena) begin

if(ss == 8'h59)

if(mm == 8'h59)

mm <= 8'h00;

else

if(mm[3:0] < 4'h9)

begin

mm[3:0] <= mm[3:0] + 1'h1;

end

else

begin

mm[3:0] <= 0;

mm[7:4] <= mm[7:4] + 1'h1;

end

end

always@(posedge clk )

if (reset) hh <= 8'h12;

else if(ena) begin

if(mm == 8'h59 && ss == 8'h59) begin

if(hh == 8'h12)

hh <= 8'h01;

else

if(hh[3:0] < 4'h9)

begin

hh[3:0] <= hh[3:0] + 1'h1;

end

else

begin

hh[3:0] <= 0;

hh[7:4] <= hh[7:4] + 1'h1;

end

end

end

always@(posedge clk )

if (reset) pm <= 0;

else if(hh == 8'h11 && mm == 8'h59 && ss == 8'h59)

pm =!pm;

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?