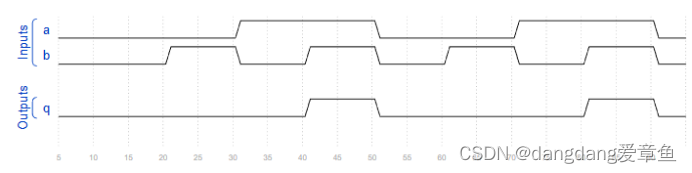

Sim/circuit1

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input a,

input b,

output q );//

assign q = a & b; // Fix me

endmoduleSim/circuit2

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = a&b&~c&~d | a&~b&c&~d | a&~b&~c&d | ~a&b&c&~d | ~a&b&~c&d | ~a&~b&c&d | ~a&~b&~c&~d | a&b&c&d; // Fix me

endmoduleSim/circuit3

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b&d | b&c | a&d | a&c; // Fix me列真值表,画卡诺图

endmoduleSim/circuit4

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b | c; // Fix me

endmoduleSim/circuit5

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input [3:0] a,

input [3:0] b,

input [3:0] c,

input [3:0] d,

input [3:0] e,

output [3:0] q );

always@(*)begin

case(c)

0: q = b;

1: q = e;

2: q = a;

3: q = d;

default: q = 4'hf;

endcase

end

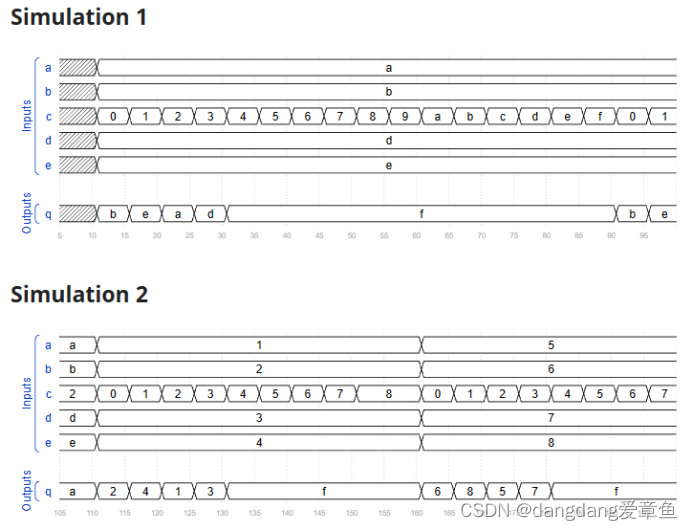

endmoduleSim/circuit6

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input [2:0] a,

output [15:0] q );

always@(*)begin

case(a)

0: q = 16'h1232;

1: q = 16'haee0;

2: q = 16'h27d4;

3: q = 16'h5a0e;

4: q = 16'h2066;

5: q = 16'h64ce;

6: q = 16'hc526;

7: q = 16'h2f19;

endcase

end

endmoduleSim/circuit7

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input clk,

input a,

output q );

always@(posedge clk)

q <= ~a;

endmoduleSim/circuit8

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input clock,

input a,

output p,

output q );

always@(negedge clock)

q <= p;

always@(*)

if(clock)

p = a;

else

p = p;

endmoduleSim/circuit9

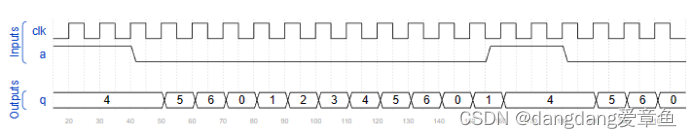

这是一个组合电路。读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input clk,

input a,

output [3:0] q );

//a相当于复位信号,置为4,;计数器计到6

always@(posedge clk)

if(a)

q <= 4'd4;

else if(q == 4'd6)

q <= 4'd0;

else

q <= q + 1'd1;

endmoduleSim/circuit10

这是一个时序电路。该电路由组合逻辑和一位存储器(即一个触发器)组成。触发器的输出已通过输出状态进行观察。

读取仿真波形以确定电路的作用,然后实现它。

代码如下:

module top_module (

input clk,

input a,

input b,

output q,

output state );

always@(posedge clk)begin

state <= a & b | state & a | state & b;

end

assign q = ~state & ~a & b |

~state & a & ~b |

state & ~a & ~b |

state & a & b;

endmodule

2237

2237

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?