写在前面

我自己使用Questasim仿真的时候,每次修改源代码都需要重新退出Questasim,然后再仿真,才能仿出来。

而脚本化仿真是不需要这么麻烦的,修改源代码或者仿真后只需要按上键,引出do sim.do,然后enter运行就可以了,非常方便快捷,不需要每次打开都重新进入vivado然后从里面打开Questasim。

在编写逻辑代码的过程中,我们常常会面对繁琐的验证,这个过程需要我们不断回到代码,进行修改,然后重新仿真……

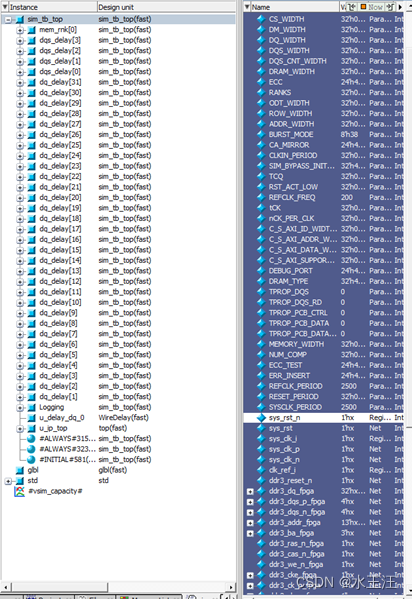

如果面对的是非常复杂的IP,面对几十上百条信号,比如说GTX,MIG,PCIE等,信号数量庞大。

这就导致,每次验证,我们都需要从非常多,而且可能是命名不规范的信号中寻找几条有用的信号,将它添加到波形框中。

尤其是命名不规范,这个非常折磨,自己写的代码,往往过些时候就忘记了,如果不看注释根本不知道这个信号有什么用。

而且,每次重新验证添加信号的过程太麻烦了,太花时间了。

想想看,自己看到一个信号出现了问题,回到代码将verilog错误改正后,然后run simulation——等待——添加波形——restart——修改运行时间——等待……

等波形出来,中饭都吃完了,结果发现问题还在,忙了半天白忙活。

所以验证其实是一个比较折磨的过程。

接下来我会讲述如何利用Questasim进行脚本化仿真。

(本文可以从邪道仿真开始看)

常用的tcl语言介绍

Tcl语言还挺复杂的,有兴趣的可以看看B站上西南交大坻志雄老师的课程,有一个初步的了解,这里只介绍本文中用到的语法。

- vlog

vlog语法可以用来编译用verilog的代码文件,对于QuestaSim,vlog还能编译system verilog文件

vlog +initreg+0 +initwire+0 +initmem+0 -f ./dut.f

比如说这段代码,我们首先定义了起始信号(比如说复位信号)为0,然后进入“dut.f”文件,这个文件中的内容如下。、

#源文件

D:/PRO/light/src/light.v

#仿真文件

D:/PRO/light/sim/tb_light.v

#glbl文件

D:/PRO/light/light.sim/sim_1/behav/xsim/glbl.v

这个文件中必须包括所有的源文件、仿真文件和“glbl”文件地址,如果存在简单IP核的的话,需要将IP核对应的“netlist.v”文件地址也添加进来。

注意这里的简单ip核指的是。

RAM,PLL,FIFO等一些功能简单的IP核。

如果工程中含有MIG这些IP,那就是另一套玩法,可以直接看邪道仿真的部分。

- vsim

我也没搞懂这个语法是什么意思,我只知道它可以直接跟仿真器联系,加载一些仿真需要的设计文件,但是具体怎么用我是真的不知道,非常抱歉。

有兴趣的朋友可以自行查阅相当文档。

这里提供一种通用的用法,我认为可以涵盖所有的需求了。

#加载需要用的编译库,这个库就是使用Vivado的时候,

#绑定第三方仿真器时系统加载的编译库,

#这一块儿地方直接复制粘贴就好

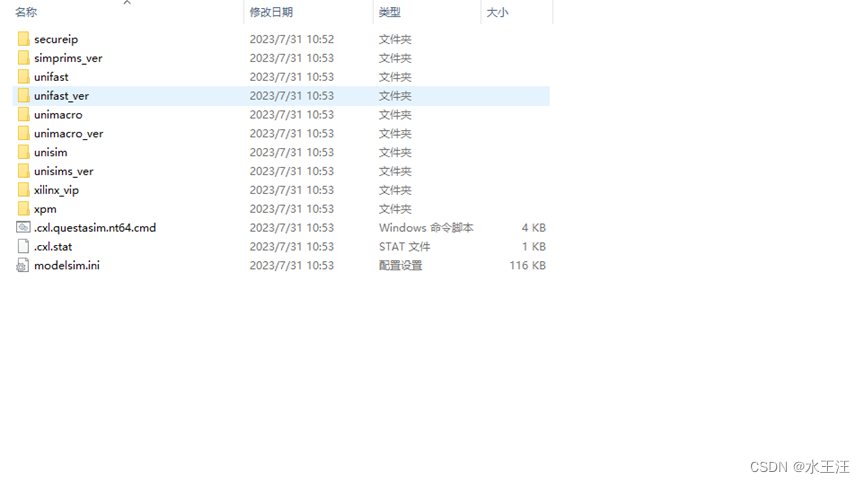

vsim -t ps -l vsim.log -novopt +notimingchecks \

-L secureip -L simprims_ver -L unifast -L unifast_ver \

-L unimacro -L unimacro_ver -L unisim -L unisims_ver -L xilinx_vip -L xpm \

#分割线

work.tb_light work.glbl

这个“work.”是什么意思我也不太懂,但是没关系,只需要注意的是,“work.tb_light”后缀需要改成你自己的仿真文件名称。

- view

可以显示数据和波形,我只会这么多……哦不是,是只能说这么多了。

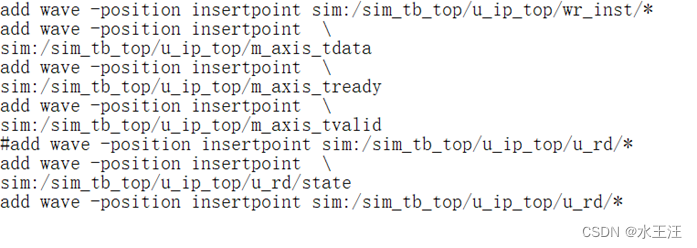

- add

紧接着view,我们需要添加一些波形,通常情况下,我们会把波形添加到一个名为wave.do的文件中,然后我们执行do wave.do。

之所以要怎么做,是因为不同工程需要观察的信号波形是不一样的,与其在头文件中修改,不如单独在wave.do文件中进行简单修正。

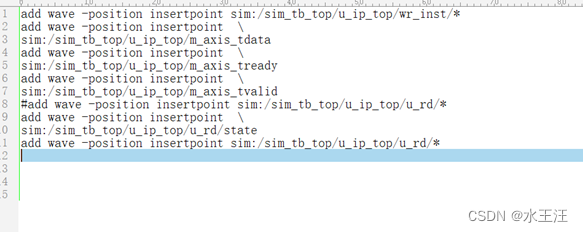

这里其实可以提一嘴,波形的添加其实是非常复杂的,比如说我想添加我在工程中例化的FIFO的stream接口的tdata信号,那么我需要这样添加。

add wave -position insertpoint \

sim:/sim_tb_top/u_ip_top/m_axis_tdata

根本看不懂这个关键词在干什么0.o。

之所以这样去写,其实是因为我不希望你去手敲这个wave信号,我们有简单的方法这个之后再提。

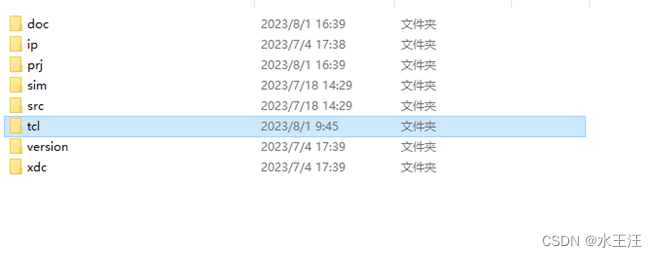

文件分类和创建

在进行本次尝试之前,本人的建议是,在自己的工程文件夹下面创建一个文件夹tcl。

tcl文件夹至少应该有如下文件。

- dut.f

里面放着的是所需文件的地址,就是这个工程用到的所有源文件,仿真文件,IP核的“netlist.v”文件,此处不再详述。

- sim.do

vlib work

#编译所有需要的文件

vlog +initreg+0 +initwire+0 +initmem+0 -f ./dut.f

#加载我们需要的所有的编译库

vsim -t ps -l vsim.log -novopt +notimingchecks \

-L secureip -L simprims_ver -L unifast -L unifast_ver \

-L unimacro -L unimacro_ver -L unisim -L unisims_ver -L xilinx_vip -L xpm \

work.tb_fifo work.glbl

#打开波形框图

view wave signals

#将所有信号的进制改为16进制

radix Hexadecimal

#记录执行日志,这个可以不要

log -r/*

#执行波形文件,往波形框中添加自己想要的波形文件

do wave.do

#执行仿真,跑5ms,这里跑多少可以自己设置

run 5ms

3.wave.do

该文件中存放着你需要的信号,如下所示。

这里建议直接add wave *,一键查看所有波形……

好吧开玩笑的。

这里介绍一种实用而且简单的办法来添加波形。

首先自己使用Questasim把文件仿真一遍。

然后,我们在Questasim上把需要的波形添加到wave框中。

这里添加的波形信号是sys_rst_n。

这时候回到Transcript。

重点来了,我们按键盘上的“上指示键”,就是4399双人游戏中第二个角色使用的方向键的上键,接着就会出现如下内容。

我们复制内容粘贴到wave.do文件中即可。

像这样粘贴几次。

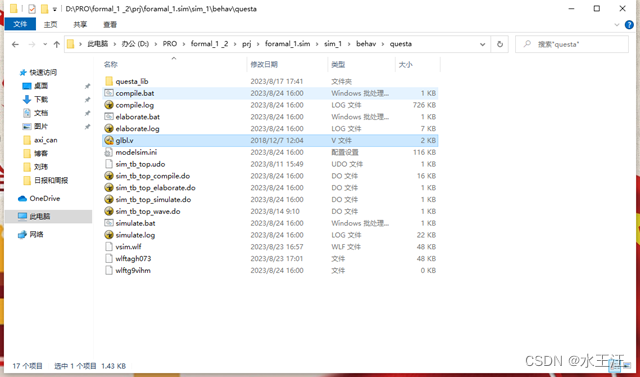

4.glbl.v、modelsim.ini和testbench.v文件

对于这三个文件,glbl.v和modelsim.ini文件的存放路径如图所示。

这个文件存放在经过一次仿真产生的Questasim仿真文件夹下。直接复制粘贴就好了。

其中,modelsim.ini也可以在自己自己的仿真library下找到。

而testbench.v文件则是你自己的仿真文件,直接复制粘贴就好了。

当然,你也可以不把他们放在这里,在dut.f文件中,添加上这两个文件的路径即可。,

实际操作

在Questasim中,我们首先打开Transcript。

接着我们查看sim.do文件的位置。

我们可以右键点击属性查看,如图所示。

所以,我们在Transcript框中,输入如下代码

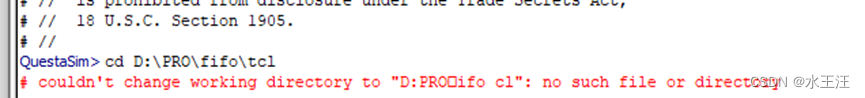

cd D:\PRO\fifo\tcl

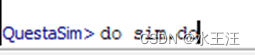

然后,运行文件。

do sim.do

接着Questasim就会自动执行,你想要的波形会呈现在wave框中。

好吧,开玩笑的,其实根本运行不起来。

如果你按照上面的步骤进行的话,Questasim会报错,报错内容是

这是Questasim非常反常的地方,你不能

cd D:\PRO\fifo\tcl

而应该

cd D:/PRO/fifo/tcl

没错,就是正斜杠与反斜杠的区别。什么?你问我为什么会这样?

我也不知道啊,这是我试了很多次蒙出来的错误,如果有兴趣的话可以去查官方的资料,我反正没有在中文互联网上找到这个问题的答案。

说回正题,你就简单地理解为,Questasim无法识别这个“\”。

它只能识别两种斜杠,一个是“/”,另一个是“\\”。

在dut.f文件中,所有的地址必须使用这两种斜杠去表示,如图所示

(这个图缺少一个fifo的netlist文件,仿真的时候是要添加上的)

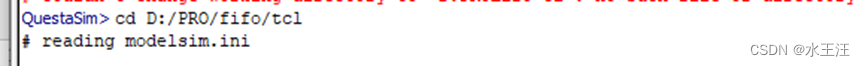

如果你改正了这个错误,并且cd成功了。

Transcript框中会出现如下提示。

它会自动识别你的modelsim.ini库

接着,进行do sim.do操作

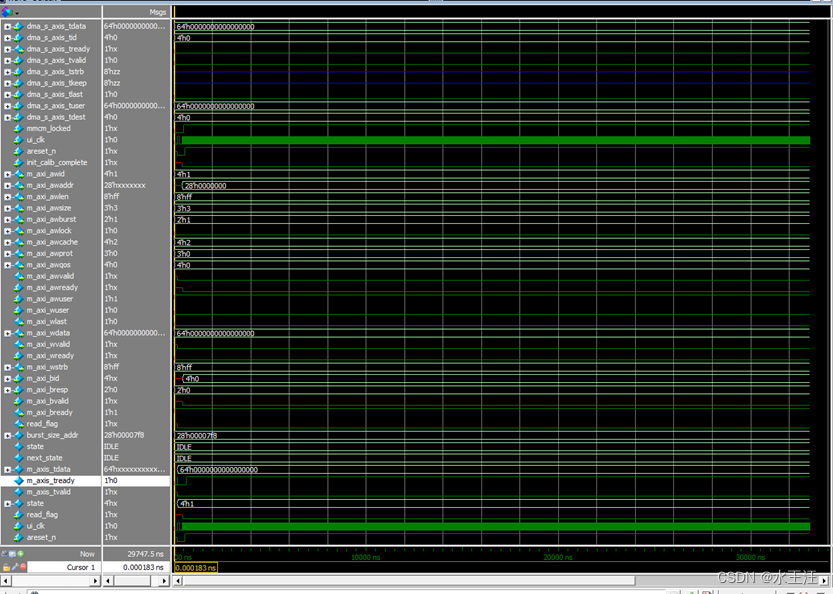

然后你就能看到波形了

到这里所有的操作就已经结束了

之后你只需要每次都按上键,接着enter就能重置仿真。

邪道仿真

其实……我有一句很重要的话要说,那就是……

本文可以直接从这里开始看

这是我结合魏老师的方法,琢磨出来的,比较邪道。

首先我们用Questasim仿一遍。

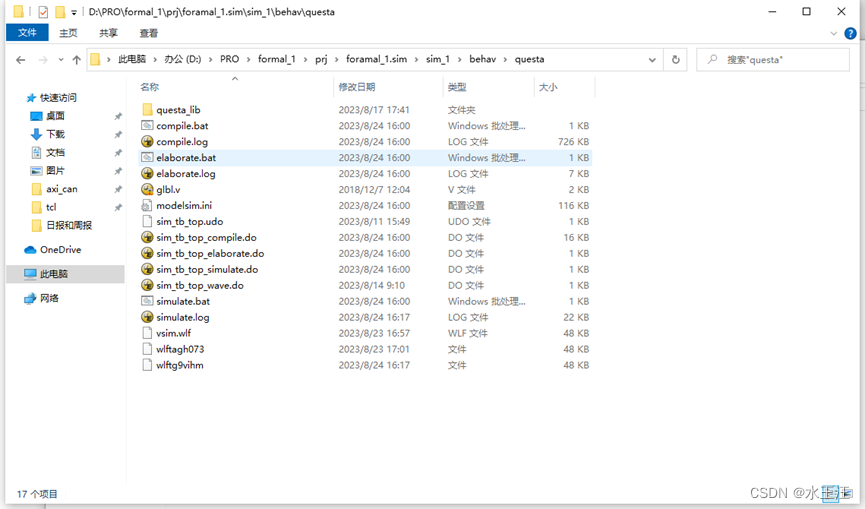

之后来到这个文件夹下面。

这个就是我们使用Questasim后,由Questasim产生的一些tcl类型的文件。

我们将所有文件全部复制,粘贴到自己创立的tcl文件夹下面,如果不懂,点这里。

Tcl文件夹里面什么也不放,上面的文件已经足够了。

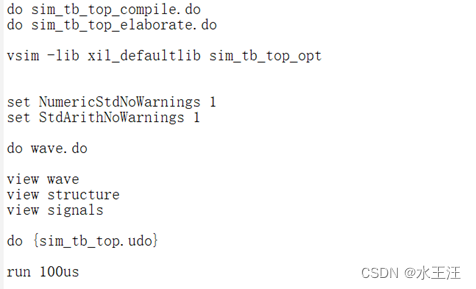

然后,修改sim_tb_top_simulate.do为sim.do

在sim.do最上面添加(一定是最上面最上面!!!前面不能有任何有效执行文件)

do sim_tb_top_compile.do

do sim_tb_top_elaborate.do

使用modelsim的朋友没有sim_tb_top_elaborate.do这个文件。

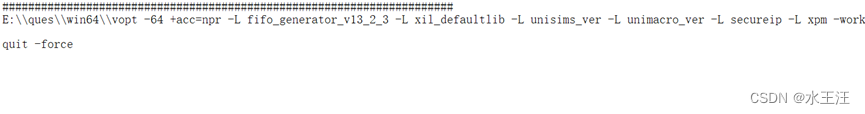

可以自己创建一个出来,里面写上这些东西。

E:\\ques\\win64\\vopt -64 +acc=npr -L fifo_generator_v13_2_3 -L xil_defaultlib -L unisims_ver -L unimacro_ver -L secureip -L xpm -work xil_defaultlib xil_defaultlib.sim_tb_top xil_defaultlib.glbl -o sim_tb_top_opt

第一个地址可能是modelsim的安装文件,因人而异。

如果这样还不行的话,那……

那你就安装Questasim吧。

说回正题。

接着删去sim_tb_top_compile.do和sim_tb_top_elaborate.do里面最后一行的quit –force

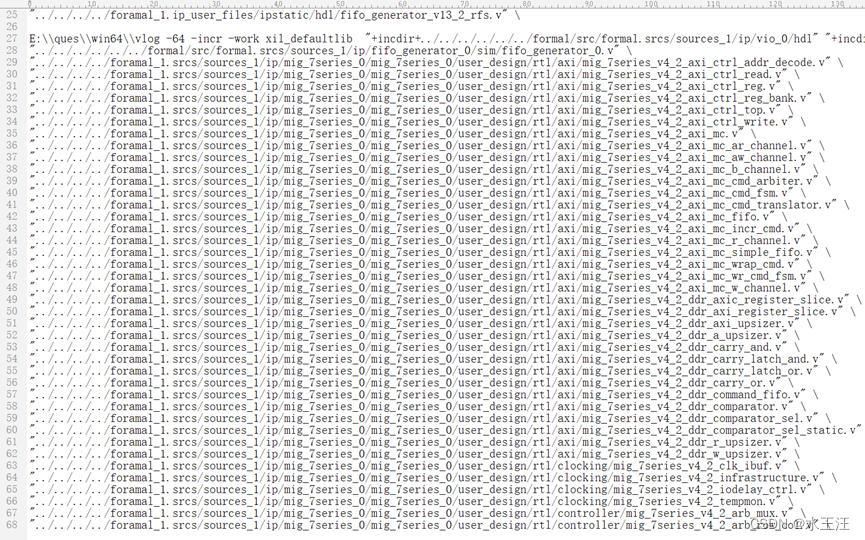

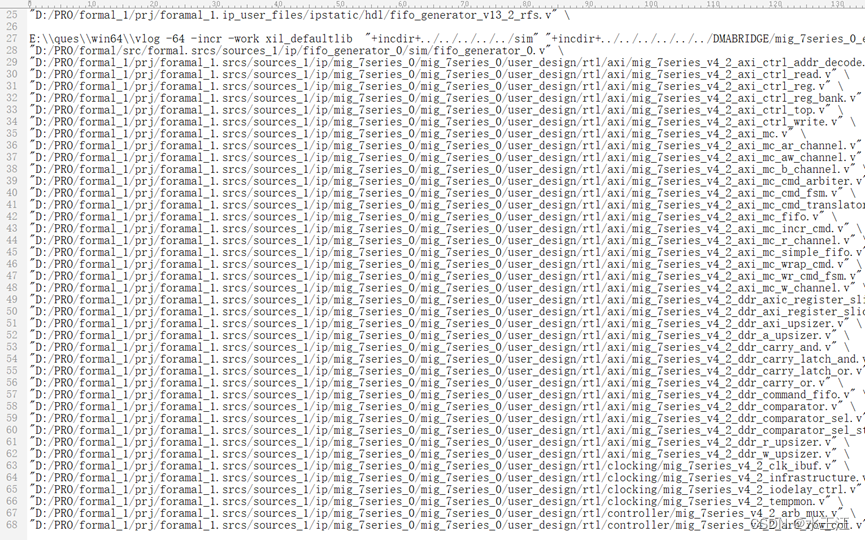

接着,打开sim_tb_top_compile.do文件。

大家可以看到,这个文件所有的地址全是省略了前面的内容。

添加上。

这个过程大概要5~10分钟,一般。

然后就是修改wave文件的内容,方法和前面的一样,可以去看看wave.do

然后,接下来就跟实际操作的部分一样了。

我没有试过,这个方法适用于复杂ip的仿真,但是我觉得应该也适用所有的仿真吧。

写在最后

其实tcl是很好用的东西,如果能好好使用的话,你甚至可以在这个基础上考虑真正意义上的一步到位。

比如说进一步省去修改信号名称前缀的时间,省去按crtl+G的时间等。

这篇文章写的其实不是很好,我也有很多不太懂的地方,如果给你造成了困扰,十分抱歉。

最后特别感谢一下我的指导老师魏老师,他的脚本仿真给了我很多启发。

1828

1828

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?