1. 概况

MIPI RFFE是一种专门针对当前及未来无线系统在射频(RF)前端控制界面规范。随着手机射频系统日趋复杂,业界需要一个单一控制界面解决方案。MIPI联盟的RF前端控制界面(RFFE)规范通过提供一个可连接到收发器或无线电的总线界面解决了这一难题,可用于给多种射频前端设备,如低噪声放大器(LNA)、功率放大器(PA)、天线开关、天线调谐器、DC/DC转换器、滤波器、感测器等。

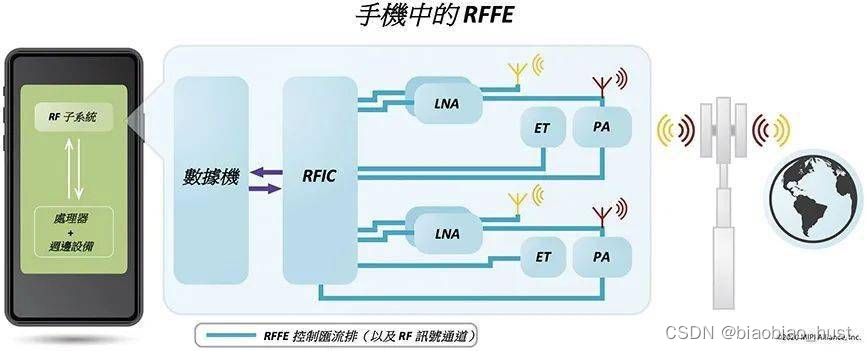

对5G而言,几乎没有什么比RF前端(RFFE)控制基础架构更为重要。任何影片数据、任何应用程序数据(基本上以无线方式传输或接收的任何内容皆然)都仰赖RFFE来控制RF前端模块(FEM)或子系统,包含所有功率放大器、天线调谐器、滤波器、低噪声放大器(LNA)、交换器等等,这些子系统均链接至调制解调器基频和/或射频集成电路(RFIC)收发机。

MIPI RFFE(MIPI RF Front-end,MIPI射频前端)是MIPI联盟RFFE工作组在2010年推出的用于移动终端射频前端控制的控制接口标准。MIPI RFFE协议总线由一根电源线(VIO)以及两根控制线(SCLK和SDATA)共3根线构成,实现简单,易于部署,可实现时序范围要求内的近实时控制。

在MIPI RFFE推出之前,射频前端的控制解决方案复杂,如果用并行的GPIO口进行控制,需要接口过多,系统成本无法承载;一些厂商开始自定义串口控制,不过由于通信协议复杂,需要考虑复杂的软件控制和时序控制,实现困难,并且自定义串口也不利于不同厂商器件的通信。

目前,MIPI协议已演进至V3.0版本,支持多种Trigger模式,适应5G通信系统中更多器件以及更严苛的时序控制要求。各个MIPI版本演进时增加的主要特性如下:

2. MIPI RFFE的系统架构

一个MIPI RFFE的架构通常包含:

-

Signal Bus:包含SCLK和SDATA两条信号线

-

RFFE Master Device:控制系统MIPI signal bus的器件,一般为手机系统中的RFIC(transceiver),单个MIPI系统最多可支持4个Master device

-

BOM:Bus Own Master,任一时刻只能有一个BOM被激活

-

RFFE Slave Device:MIPI受控

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

172

172

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?