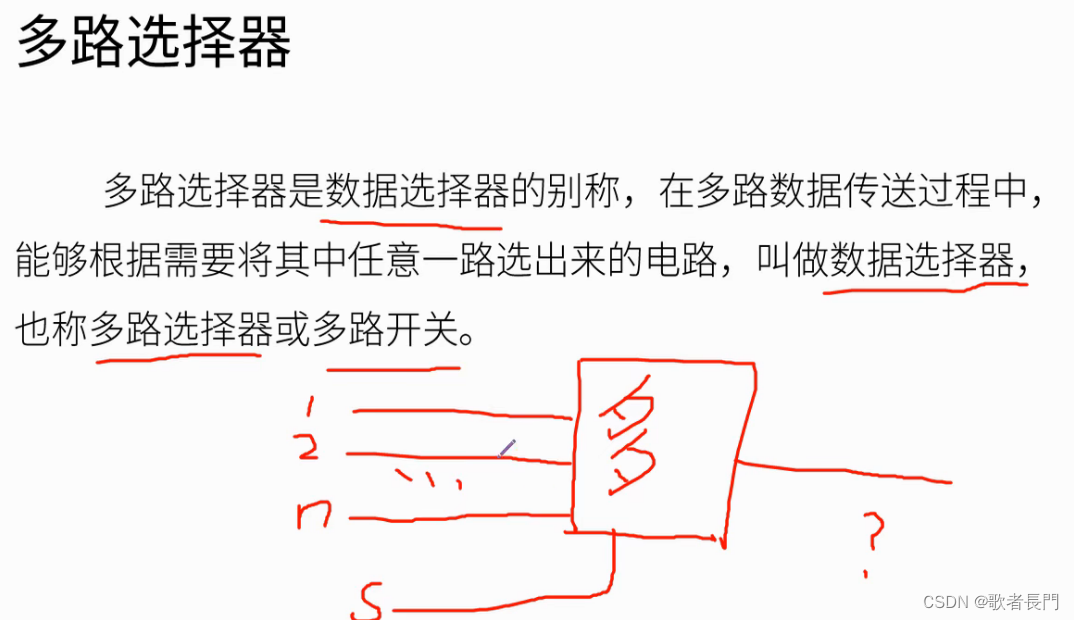

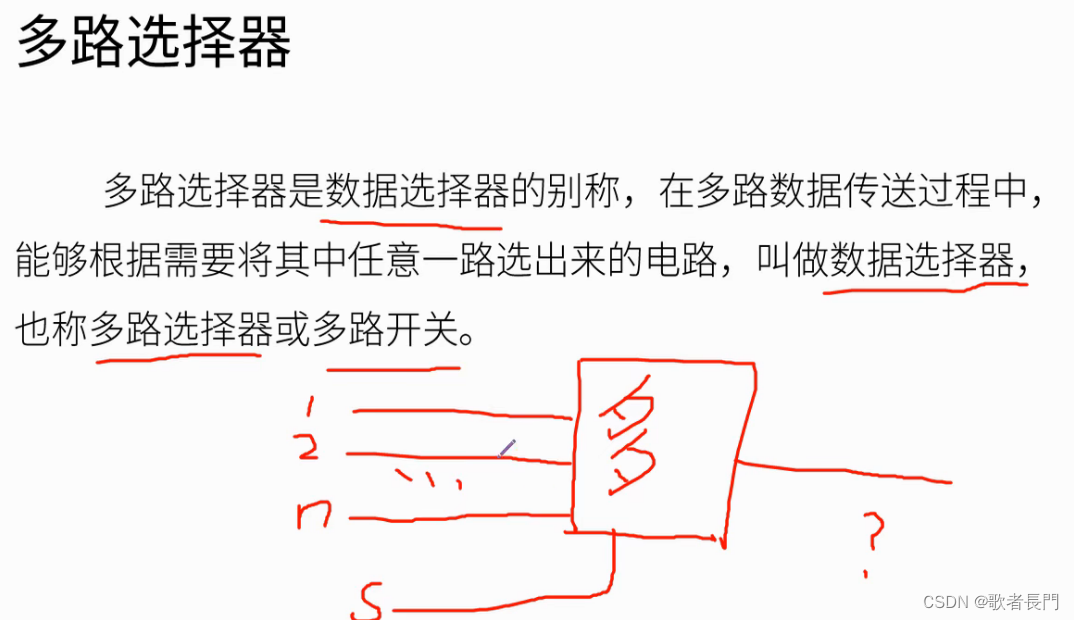

1.多路选择器

(1 框图

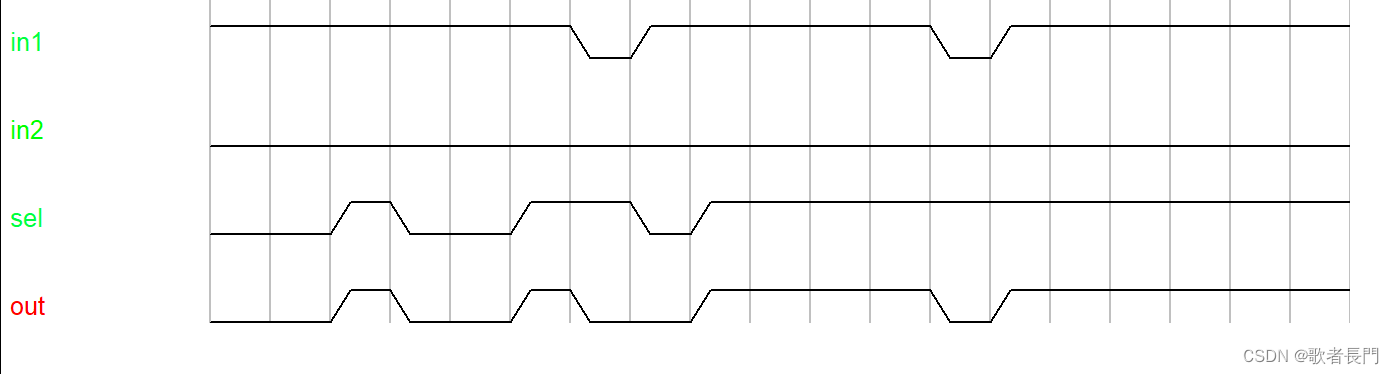

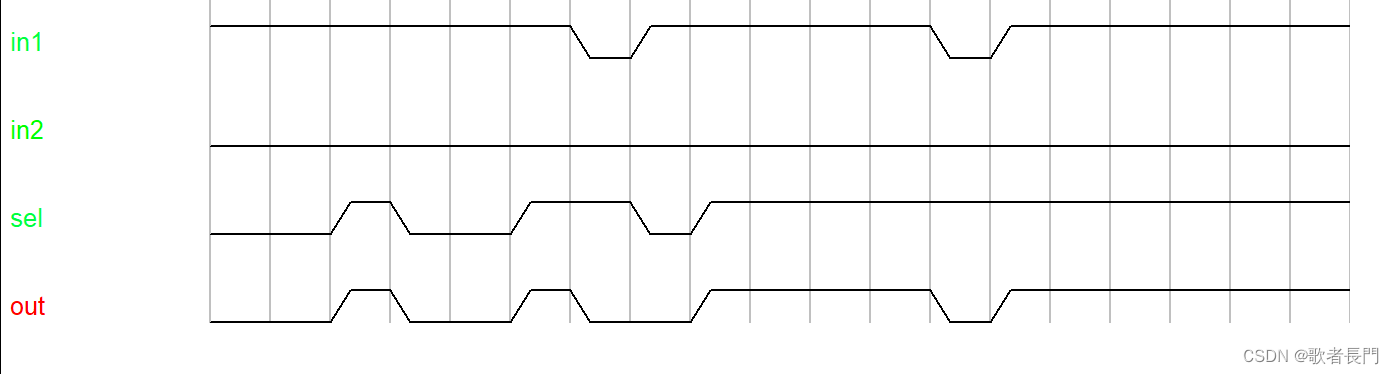

(2 波形图

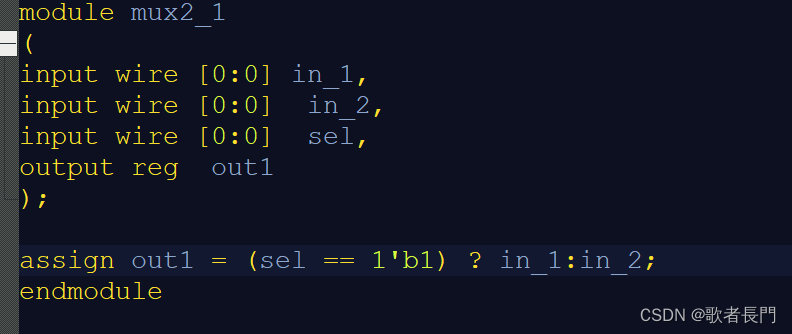

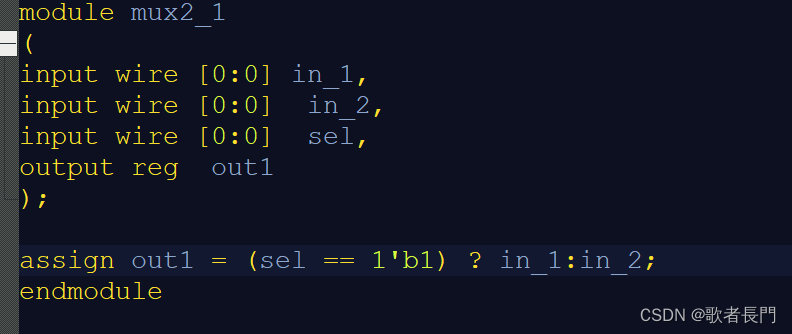

(3 编辑代码

`timescale 1ns / 1ns

module tb_mux2_1();

reg[0:0] in_1;

reg[0:0] in_2;

reg[0:0] sel;

wire[0:0] out1;

initial//这个语句表示整个上电过程只执行一次内容,作用是初始化信号,否则就是未定态了

begin

in_1 <= 1'b0;

in_2 <= 1'b0;

sel <= 1'b0;

forever

begin

#10 in_1 <= {$random} % 2;

#10 in_2 <= {$random} % 2;

#10 sel <= {$random} % 2;

end

end

//每经过10ns就会执行一次always,{$random}是系统函数产生随机数,{$random} % 1'd2表示随机数除以2取余数不是0就是1

mux2_1 mux2_1_inst //此操作为模块例化,格式是模块名加例化名称,并且把里面的信号名称和外面顶层模块的信号名称对应起来,

//注意顶层模块的信号名称写在括号里面,这样可以调用mux模块

(

.in_1(int_1),

.in_2(int_2),

.sel(sel),//alt+鼠标左键,可以进行列选择以及列输入

.out1(out1)

);

endmodule

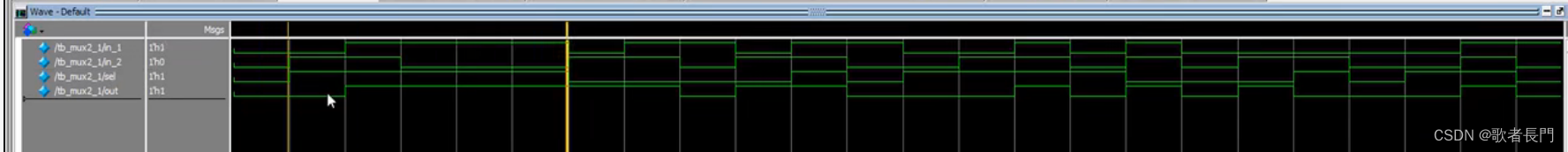

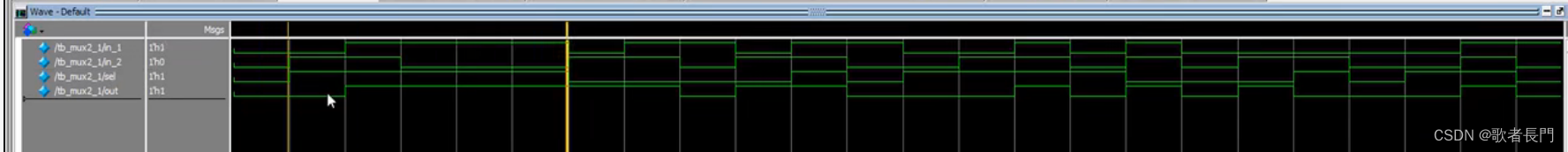

(4 波形仿真

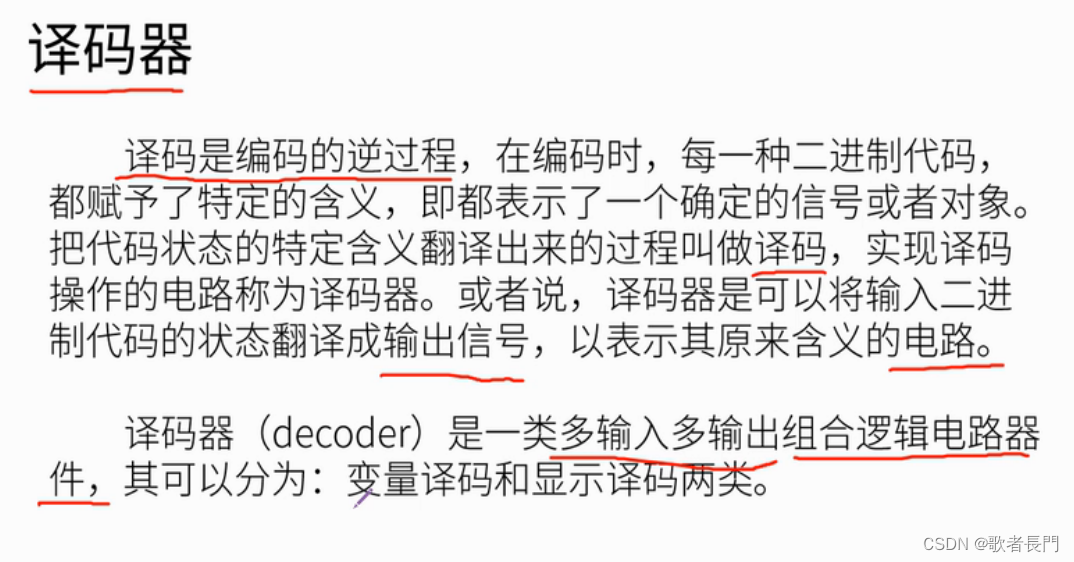

2.译码器

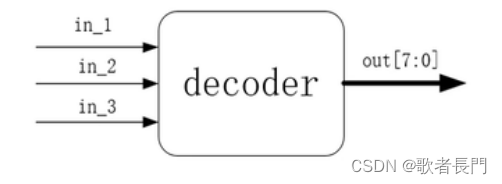

(1 原理与框图

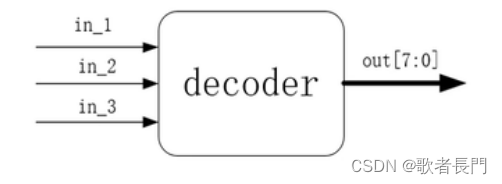

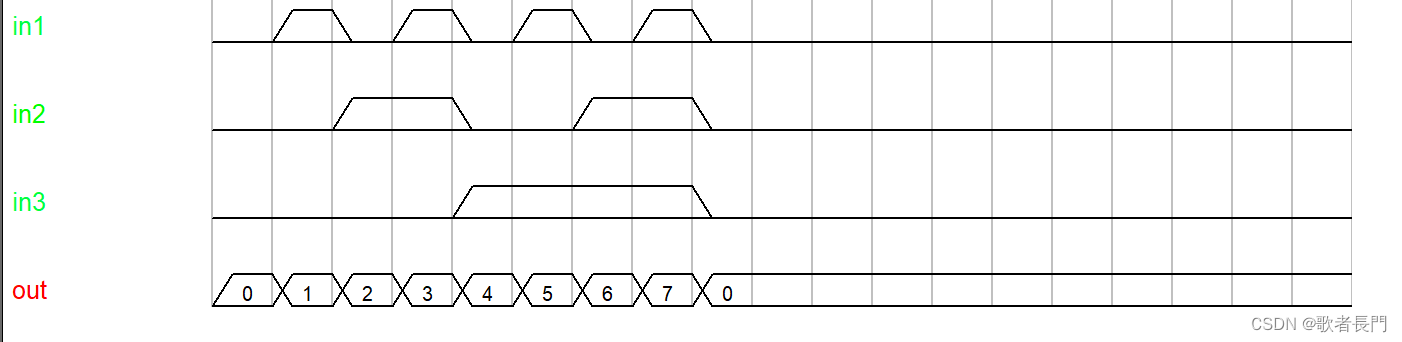

(2 波形图

(3代码(含测试代码)

module decoder

(

input wire in1,

input wire in2,

input wire in3,

output reg [2:0] out

);

always@(*)begin

case({in1,in2,in3})

3'b000 : out=0;

3'b001 : out=1;

3'b010 : out=2;

3'b011 : out=3;

3'b100 : out=4;

3'b101 : out=5;

3'b110 : out=6;

3'b111 : out=7;

endcase

end

endmodule

`timescale 1ns / 1ps

module tb_decoder();

reg in1;

reg in2;

reg in3;

wire [2:0] out;

initial

begin

in1 <= 1'b0;

in2 <= 1'b0;

in3 <= 1'b0;

forever

begin

#10 in1 <= {$random} % 2;

#10 in2 <= {$random} % 2;

#10 in3 <= {$random} % 2;

end

end

decoder decoder_inst

(

.in1(in1),

.in2(in2),

.in3(in3),

.out(out)

);

endmodule

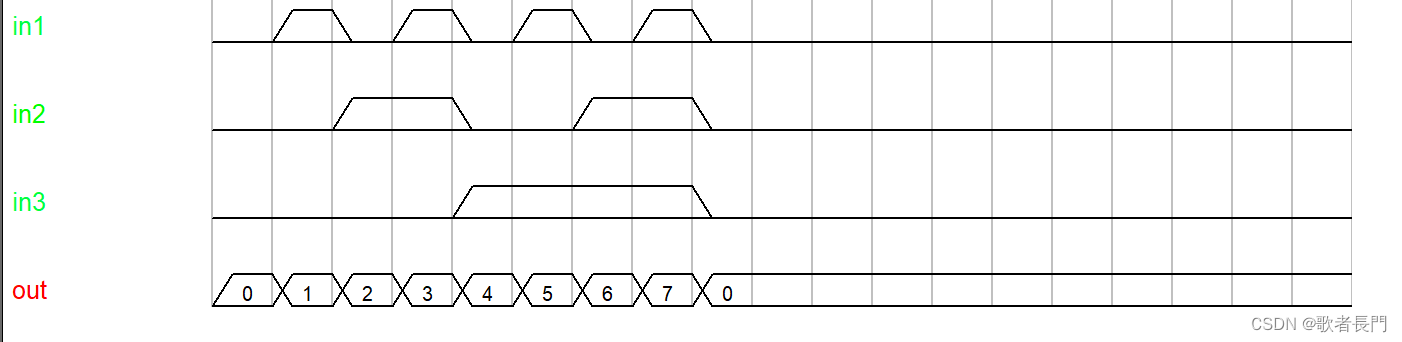

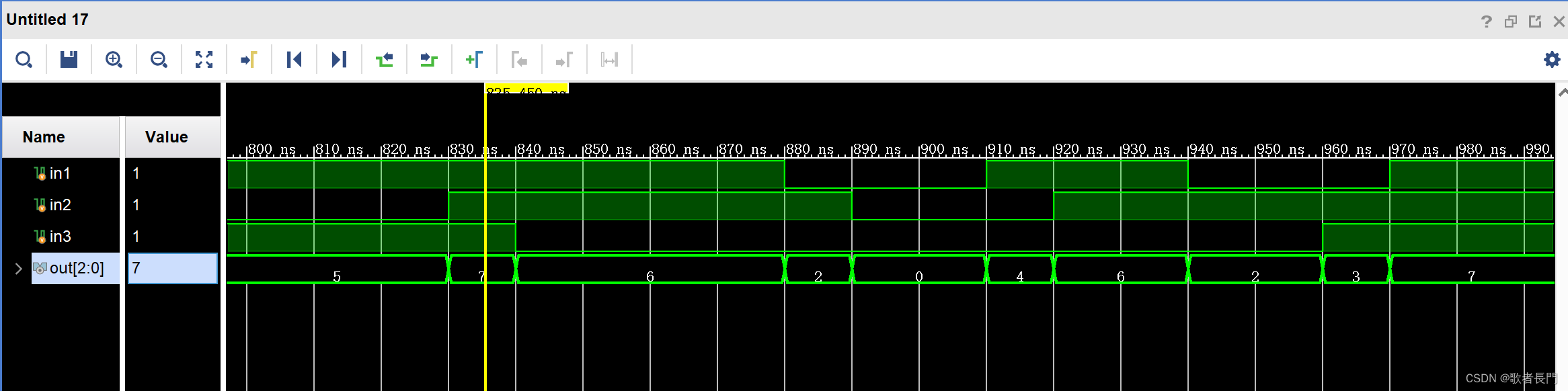

(4 仿真结果

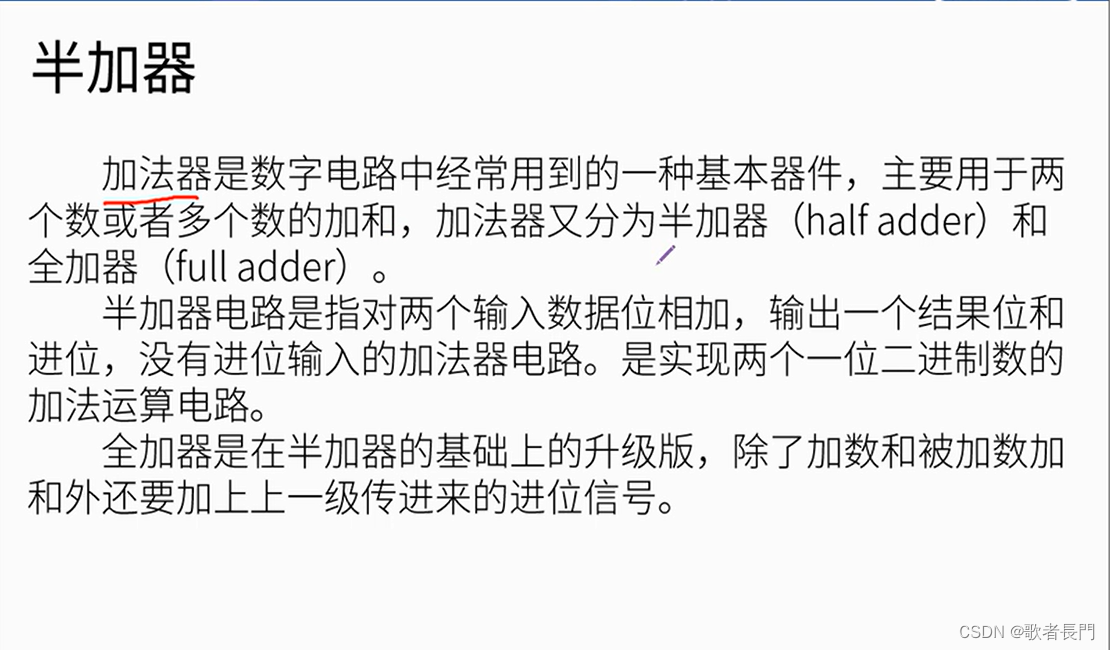

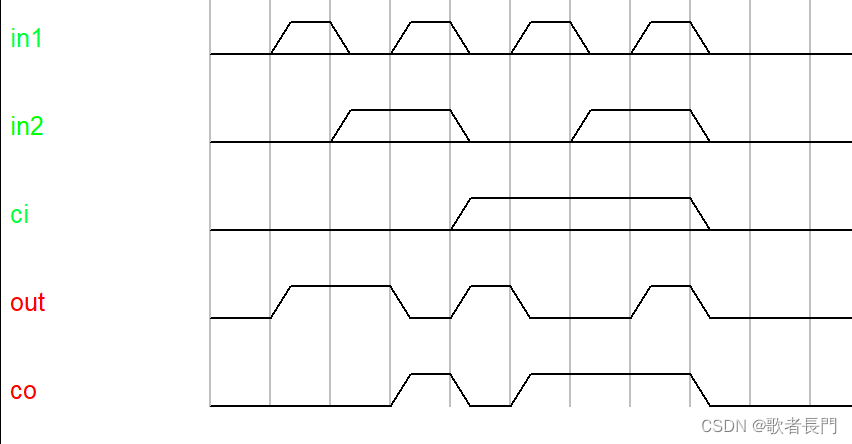

3.全加器(半加器的介绍,全加器的代码与仿真)

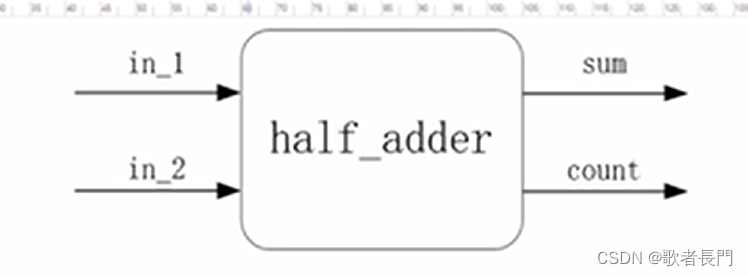

(1 框图

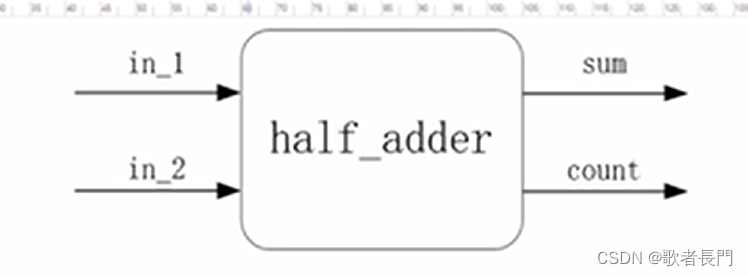

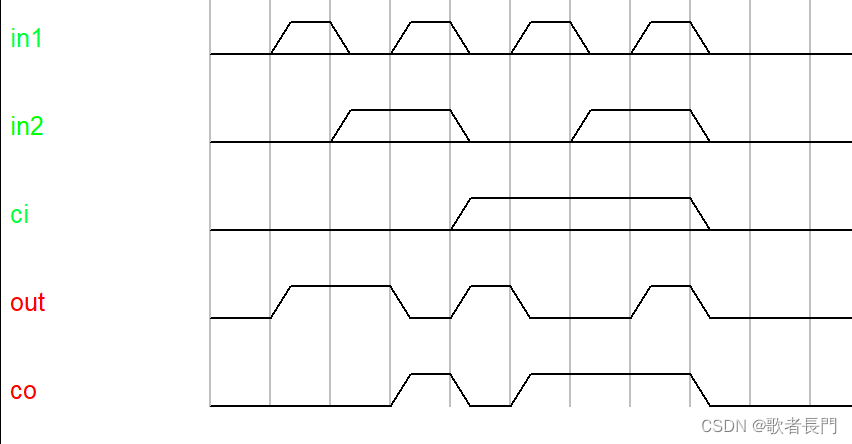

(2波形图(全加器)

(3 代码(附带testbench)

module addr

(

input wire in1,

input wire in2,

input wire ci,

output reg out,

output reg co

);

always@(*)

begin

{co,out} <= {0,in1}+{0,in2}+{0,ci};

end

endmodule

`timescale 1ns / 1ns

module tb_addr();

reg in1;

reg in2;

reg ci;

wire out;

wire co;

initial begin

in1 <= 1'b0;

in2 <= 1'b0;

ci <= 1'b0;

forever begin

#10 in1 <= {$random} % 2;

#10 in2 <= {$random} % 2;

#10 ci <= {$random} % 2;

end

end

addr addr_inst

(

.in1(in1),

.in2(in2),

.ci(ci),

.out(out),

.co (co)

);

endmodule

(4仿真结果

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?