萌新的FPGA学习之快速回顾 水 水

上一条FPGA的更新在9 25 并且2个礼拜没写 verilog 了 正好 刷新一下记忆

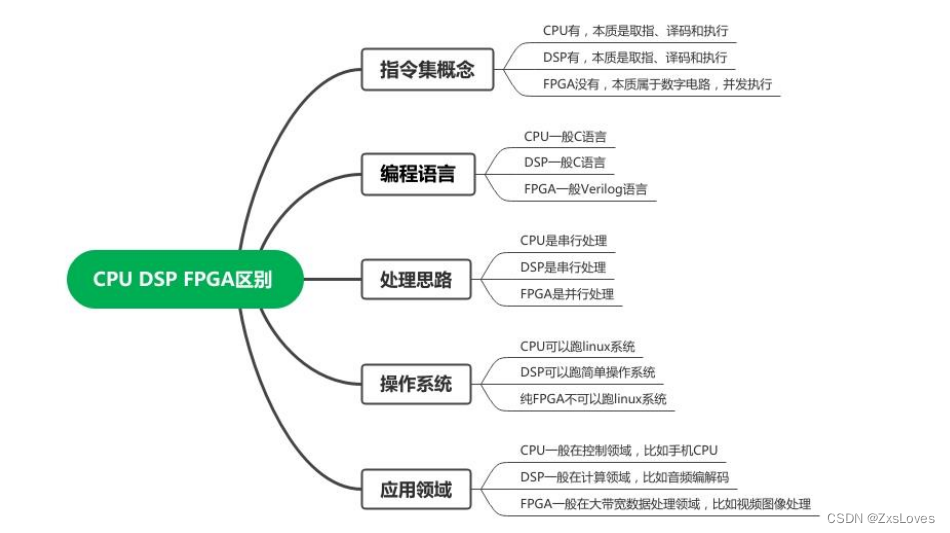

FPGA CPU DSP 的对比

在数字电路发展多年以来,出现了 CPU、DSP 和 FPGA 三种经典器件,每个都是具有划时代意义的器件。CPU、DSP 和 FPGA 都有各自的擅长领域,很多新人对这三个器件到底有啥区别,到底应该学习哪个有点懵。为此,我们梳理了三个器件的概念和区别。由于我们前面已经介绍过 FPGA,此处我们只介绍 CPU和 DSP。

我们先来了解下 CPU:

CPU 一般都是基于指令流水线的架构,从存储器中进行指令的读取,指令的解析,指令的执行这样的流程。因此,在了解 CPU 之前,我们需要去了解 CPU 的指令集,再去了解指令的具体执行方式,然后针对具体的芯片了解其外围电路。

指令集是 CPU 用来计算和控制计算机系统的一套指令的集合。目前常用的指令集主要分为两种,一个是复杂指令集(CISC),另一个是精简指令集(RISC)。其中复杂指令集是早期 intel 使用的指令集,即使到现在,大部分的 PC 中使用的依然是复杂指令集。与其相对的是精简指令集,业界普遍认为精简指令集具有较高的执行效率。

CPU 一般包括几种:

1、单片机(也叫微处理器),比如早期的 intel 8051 单片机,近几年比较火的 ST 的 STM32 单片机。

2、通用 CPU,比如 intel 和 AMD 的台式机 CPU。

3、高性能 ARM CPU,比如 ARM Coretex A53/57 内核,一般用在手机或者手持设备中。

4、RISC-V 处理器,近期 RISC-V 比较火,优势是开源且高性能,吸引了国内外很多家公司在研究。

ARM 目前还是占了很大的市场份额,甚至很多人常常使用 ARM 代替 CPU,下面单独说下 ARM:ARM 设计了大量的高性能、廉价、功耗低的 RISC 处理器,相关的技术以及软件。ARM 架构是面向低预算市场设计的第一款 RISC 微处理器,它能够提供一系列的内核、体系扩展、微处理器和系统芯片方案,这四个功能模块可供生产商根据不同的用户要求来配置生产。ARM 是 32 位单片机,其内部的硬件资源性能较高,可以加载操作系统是其主要特点,加载操作系统之后,可以向 PC 一样进行多任务的实时处理,不会相互影响。

我们再来了解下 DSP:DSP 通常负责数字信号(视频、音频和其他的传感器获得的数字信号)处理,在日常生活中,常见的数字电视机机顶盒、MP3、MP4 和光模块等都广泛使用了 DSP。由于设计的专一化,DSP 可以在较低的成本下,执行比较复杂的编解码信号处理工作。DSP 其实是一种独特的 CPU,只是拥有自己的完整指令系统,是可以处理大量数字信号的器件。最大的特点就是 DSP 内部有专门的硬件乘法器和哈佛总线结构,对大量的数字信号处理速度比较快。DSP 处理器包括有控制单元、运算单元、各种存储器、以及一定数量的存储单元,并能够与一定数量的外部设备互相通信。DSP 采用的是哈佛设计,数据总线与地址总线分开,这样程序和数据能够分别存储在两块独立的空间中,允许取指令与执行指令完全重叠,就是说在 CPU 在执行上一条指令的同时也取出了下一条指令,并完成了译码工作,提高微处理器的执行速率。此外还允许在程序空间和数据空间进行数据传输,增加器件的灵活性,具体的工作原理是将接收到的模拟信号转换成 01 的数字信号,再对数据信号进行修改、删除、强化等工作,最终在其他芯片中把数字信号解读回实际环境需要的格式,运行速度可以达到每秒千万调复杂的指令,其主要特点如下:

⚫ 在一个指令周期内可以完成一次乘法和加法运算

⚫ 程序和数据分开,同时访问指令和数据

⚫ 片内具有快速 RAM,通常能够通过独立的数据总线在两块中同时访问

⚫ 具有低开销或无开销循环以及跳转指令的硬件支持

⚫ 快速的中断处理以及硬件 IO 支持

⚫ 能够在单周期内操作多个硬件地址产生器

⚫ 可以并行执行多个操作

⚫ 支持 pipeline 操作,取值译码和执行操作可以同时执行在了解了 CPU、DSP 和 FPGA 基本概念后,我们再来看下 CPU、DSP 和 FPGA 的区别:CPU 具有比较强的事务管理功能,可以用来跑 UI 以及应用程序,CPU 优点主要在于擅长控制。DSP 主要是来做计算,例如加解密算法,调制解调等,其优势是强大的数据处理能力和较高的运行速度。FPGA 主要使用 Verilog 进行编程,灵活性强,并行处理度高,可编程,可以做到很高的带宽处理。

CPU DSP FPGA 的区别

CPU 具有比较强的事务管理功能,可以用来跑 UI 以及应用程序,CPU 优点主要在于擅长控制。DSP 主要是来做计算,例如加解密算法,调制解调等,其优势是强大的数据处理能力和较高的运行速度。FPGA 主要使用 Verilog 进行编程,灵活性强,并行处理度高,可编程,可以做到很高的带宽处理。

AXI 突发传输的意思 : 本篇文章我们将讨论有关 AXI 总线的突发传输机制( burst ),在 AXI 总线中的突发传输是指,在地址总线上进行一次地址传输后,进行多次数据传输( transfer,这个有点搞,突发传输 and 传输?)。第一次地址传输中的地址作为起始地址,根据突发传输类型的不同,后续数据的存储地址在起始地址的基础上递增(INCR 模式);或者首先递增,到达上限地址后回到起始地址,继续递增(WRAP 模式);又或者后续数据都将不断写入起始地址,刷新起始地址上的数据。(FIXED 模式)

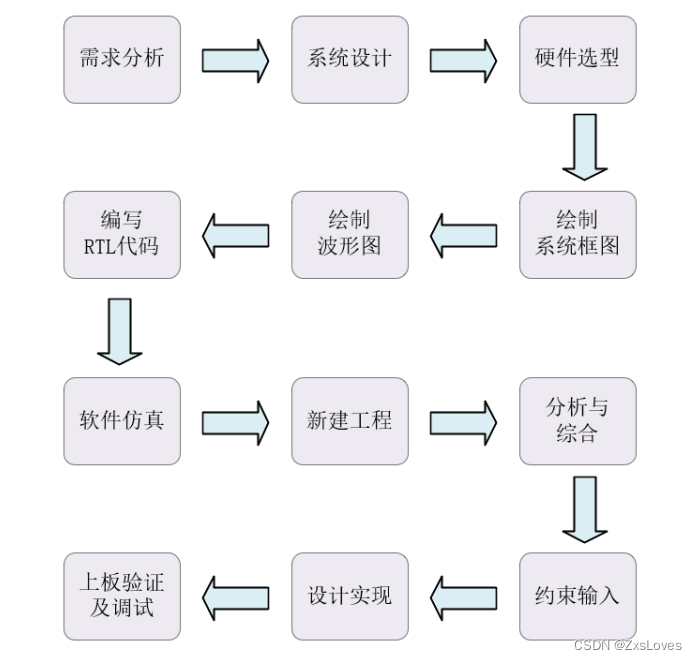

FPGA 开发流程 基本步骤

1)需求分析:做一个项目之前,我们首先需要对项目需求进行详细分析,提取项目需求需要实现什么功能;

2)系统设计:根据项目需求我们就可以进行系统架构设计,架构设计主要是将系统分为哪些模块,数据流怎么走,控制流怎么走,以及计算系统运行的带宽和评估系统的工作频率;

3)硬件选型:根据系统架构分析结果,我们就可以来选择合适规模和性能的 FPGA 芯片,这个工作称为 FPGA 器件选型,然后根据 FPGA 型号选择合适的 FPGA 板卡。FPGA 器件选型是一个综合性的工作,和项目成本、FPGA 容量和性能、FPGA 器件熟悉程度等都有关系,等大家成为大牛后可能才会有一些切身体验;

4)绘制系统框图:确定系统内各个子模块的结构层次,梳理系统对外的输入输出信号和子模块之间的交互信号;

5)绘制波形图:根据该模块的功能并且结合芯片的数据手册或者接口协议,确定模块接口信号的时序关系,然后使用绘图软件绘制各个模块的时序波形图;

6)编写 RTL 代码:使用代码编辑软件严格按照上面的波形图编写各模块的代码;

7)软件仿真:首先按照 RTL 代码的输入激励需求,编写对应的仿真代码,然后使用仿真工具对编写的RTL 代码进行仿真。仿真过程中如果 RTL 代码有语法错误,仿真工具下面的提示框会显示语法报错详细信息,可以对照该信息修改 RTL 代码,直至 RTL 代码语法错误修改完毕,才能出现仿真波形。然后观察仿真的波形图是否与我们绘制的时序波形一致,如果两者一致,接下来就可以新建工程,如果不一致,则需要通过修改代码使仿真波形与我们绘制的时序波形一致。

8)新建工程:使用 FPGA 开发平台新建工程并添加我们前面编写的 RTL 代码;

9)分析与综合:对工程进行综合编译,通过观察综合编译生成的报告可以帮助避免最常见的设计错误,以便对设计进行分析和改进;

10)约束输入:在 FPGA 开发平台对工程引脚进行约束,引脚约束完成后就可以进行布局布线与生成下载文件;

11)设计实现:就是工程布局和布线的过程。它的作用是将综合生成的逻辑网表配置到具体的 FPGA 芯片上。布局布线完成后,就可以生成下载文件了,下载文件生成成功就可以进行下一步的上板验证。

12)上板验证及调试:连接好开发板与下载器,将生成的下载文件通过下载器下载到开发板,然后观察开发板的实物运行是否正常,如果上板实验现象正常,则说明前期设计与代码编写都正常;如果上板实验现象不正常,可以通过迭代前面设计的每一步来查找问题,如果发现前面的步骤都没有问题,那么这时候可以通过在线调试来查找问题,直到解决问题,上板验证现象正常。

我的testbench的写法能力比较差 现在学习一下 tb的编写

`timescale 1ns / 1ns //仿真单位/仿真精度

这个 仿真单位是 我们在波形图上能够看到的单位

仿真精度是我们所能预见的最小精度

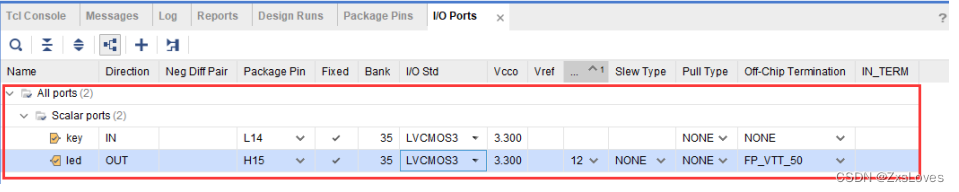

对于XDC 管脚约束文件的编写 我们可以在系统中配置完 让它自动生成xdc文件

Name:工程中顶层端口的名称。

Direction:说明管脚是输入还是输出。

Neg Diff Pair:负差分对,差分信号在 I/O Ports 窗口中只显示在一行里中(只会显示 P 端信号,N 端信号显示在 Neg Diff Pair 属性栏中)。

Package Pin:配置管脚封装。

Fixed:每一个端口都有 Fixed 属性,表明该逻辑端口是由用户赋值的。端口必须保持锁定状态,才能避免生成比特流时不会发生错误。

(Bank,I/O Std,Vcco,Slew Type,Drive Strength:显示 I/O 端口的参数值。)

Bank:显示管脚所在的 Bank。I/O

Std:配置管脚的电平标准,常用电平标准有 LVTTL 和 LVCMOS、SSTL、LVDS 与 HSTL 等

Vcco:选择的管脚的电压值。

Vref:在我们的设计中,硬件上 VREF 引脚悬空。

Drive Strength:驱动强度,默认 12mA。

Slew Type:指上升下降沿的快慢,设置快功耗会高一点,默认设置慢(slow)。

Pull Type:管脚上下拉设置,有上拉、下拉、保持与不设置。

Off-Chip Termination:终端阻抗,默认 50Ω。

IN-TERM:是用于 input 的串联电阻。

verilog 的逻辑值 的设计

Verilog 的逻辑值我们先看下逻辑电路中有四种值,即四种状态:

逻辑 0:表示低电平,也就是对应我们电路的 GND;

逻辑 1:表示高电平,也就是对应我们电路的 VCC;

逻辑 X:表示未知,有可能是高电平,也有可能是低电平;

逻辑 Z:表示高阻态,外部没有激励信号是一个悬空状态。

再次重申晶振 与系统时钟 之间的 关系 我们 发现晶振是 50MHz 那么 这样 算下来 时钟周期 就是 1/50M = 0.02us

0.02 微秒 就是 20ns

1秒等于10亿纳秒 我们 会发现

计算 0.5s 就是用 0.5/20ns = 25000000 个时钟周期

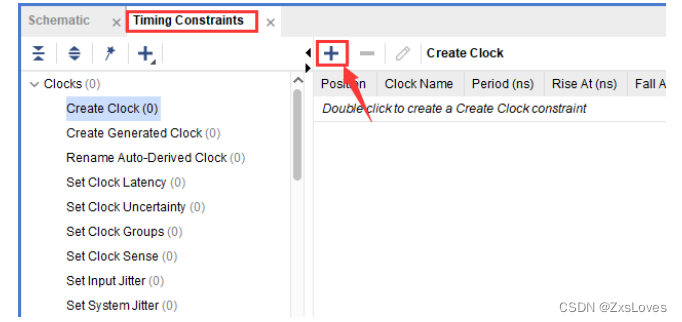

添加时钟约束的方法

约束的方法是在 XDC 文件中添加如下语句:create_clock -period 20.000 -name sys_clk [get_ports sys_clk]

“create_clock”是该命令的名称,它会创建一个时钟

;其后的“-name sys_clk”、“-period 20”、“[get_ports sys_clk ]”都是该命令的各个参数

,分别表示所创建时钟的名称是“sys_clk”、时钟周期是20ns

、时钟源是 sys_clk 端口,一般只对输入的时钟做周期约束。

点击“Edit Timing Constraints”按钮后,Vivado 就会打开“Timing Constraints”界面,我们点击该界面下的“+”号按键就可以添加时钟约束了,如下所示:

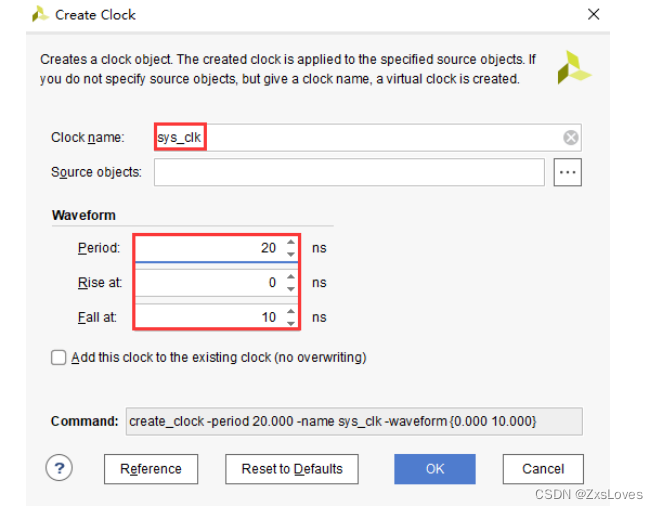

点击“+”号后,弹出的“Create Clock”界面如下所示:

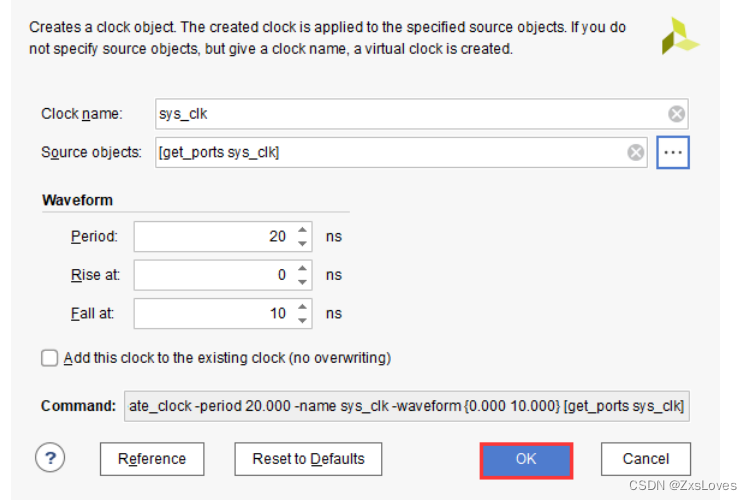

“Create Clock”界面中各参数定义如下:

1、Clock name:时钟名称,用于为所创建的时钟约束命名。为了可以一眼看出该时钟约束的约束源,

通常情况下其命名与被约束的时钟信号名相同,因为我们要对系统时钟(sys_clk)进行约束,所以这里我们

将其命名为 sys_clk。

2、Source objects:源对象,用于指定被约束的时钟对象,具体操作我们稍后进行讲解。

3、Waveform:波形,用于设置时钟的周期(Period),上升沿(Rise at)、下降沿(Fall at)以及勾选

Add this clock to the existing clock(是否将该时钟添加到现有时钟中)。因为我们的系统时钟为 50MHz(即

一个时钟周期为 20ns),占空比为 50%,所以 Period 设置为 20,Rise at 设置为 0,Fall at 设置为 10。因为

Add this clock to the existing clock 选项是在同一个约束源时钟存在多个时钟频率且每个时钟频率都需要进行

约束的情况下才需要勾选的,而我们的系统时钟只有一个频率,所以无需勾选。

4、Command:命令,即通过我们上述的配置后,vivado 自动生成的约束命令,该命令是可以直接复制

粘贴到 XDC 文件中使用的。

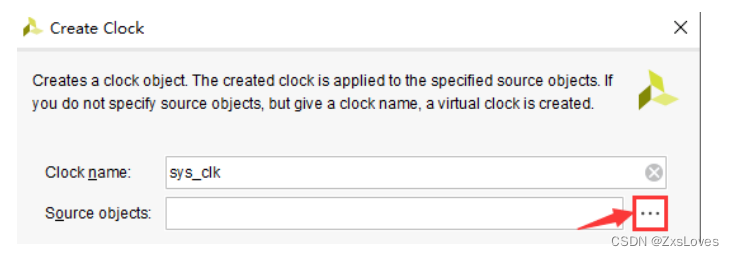

下面我们就来介绍下如何指定被约束的时钟对象,这里需要点击“Source objects”框后的“…”指定时

钟源对象,如下图所示:

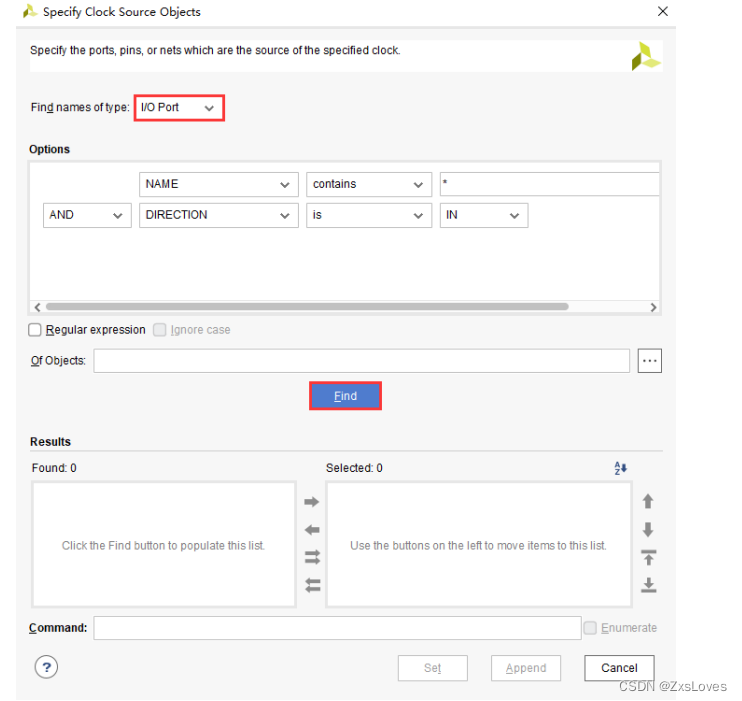

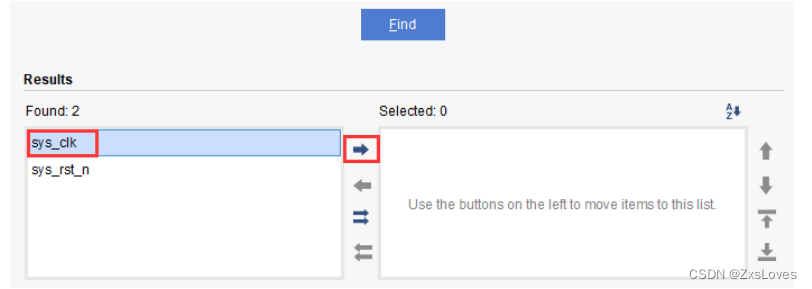

点击“…”后弹出的“Specify Clock Source Objects”界面如下所示:

“Specify Clock Source Objects”界面中“Find”之上的各个选项主要用于设置筛选条件,因为系统时钟

来自于 IO 口,所以“Find names of type(寻找名称类型)”选择“I/O Port”,其余选项保持默认,我们直

接点击“Find”按钮,如下所示:

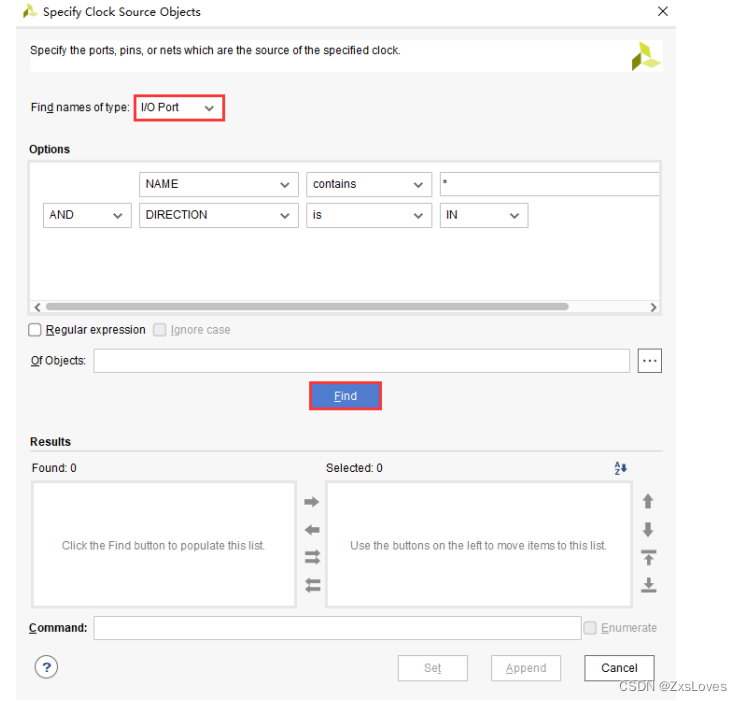

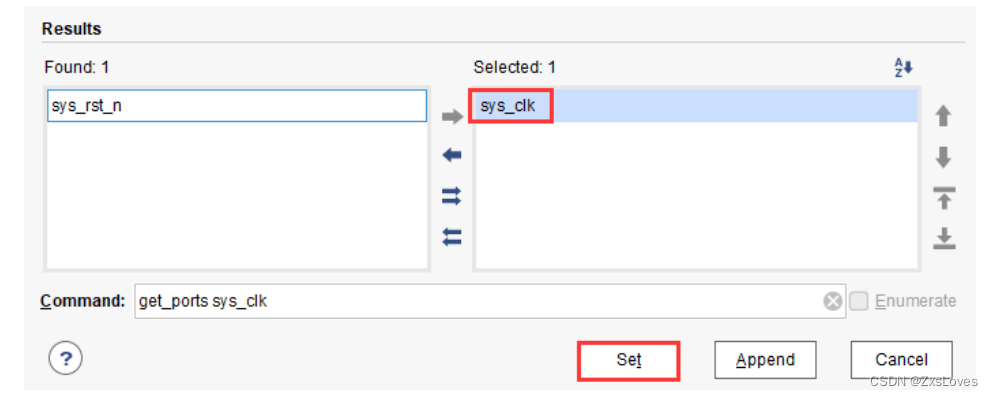

在找到的信号中,我们选择需要约束的系统时钟信号(sys_clk)然后点击“→”按钮将其添加到右侧窗

口,如下图所示

之后我们点击“Set”即可将该信号定义为源对象,此时的“Create Clock”界面如下所示:

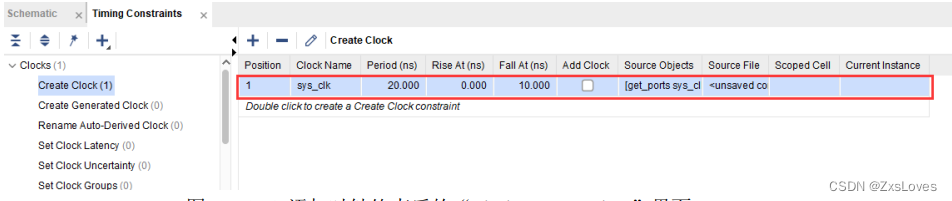

至此,时钟约束配置完成,我们点击“OK”即可添加约束并关闭“Create Clock”界面。此时的“Timing

Constraints”界面如下所示:

723

723

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?